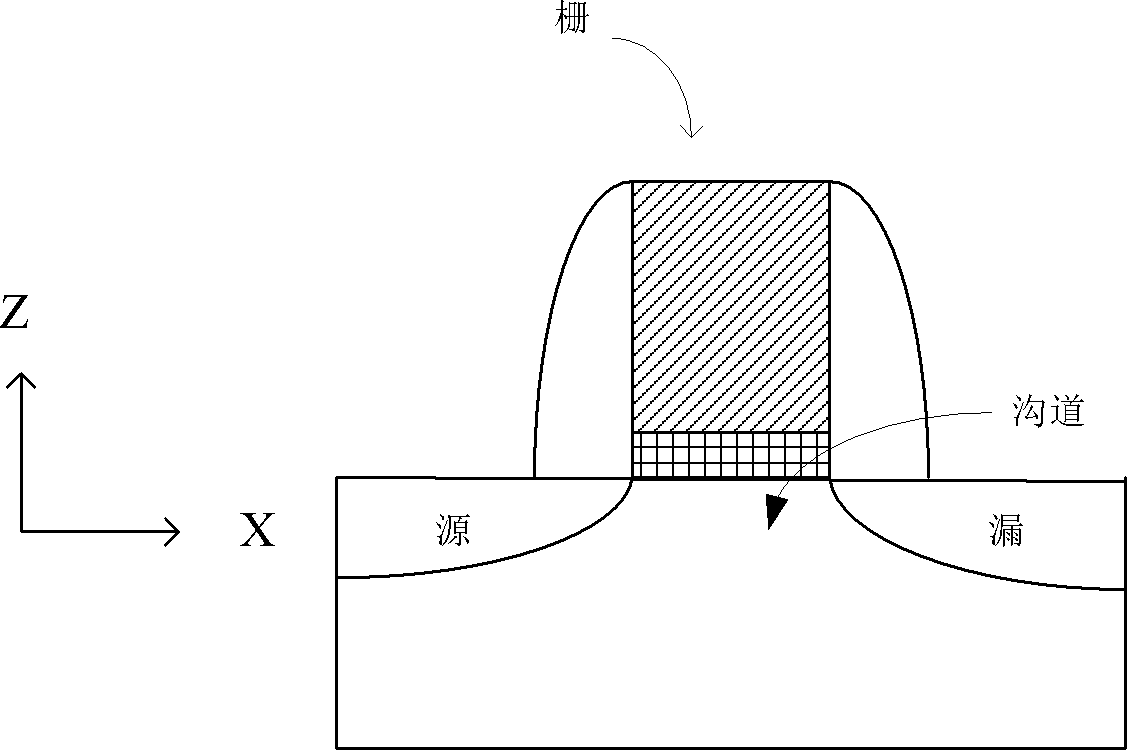

Method for introducing strain to channel and device manufactured by the same

A channel and compressive strain technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as channel introduction defects, complex processes, and weakened strain-induced effects, achieving simple process complexity, strong The effect of process flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

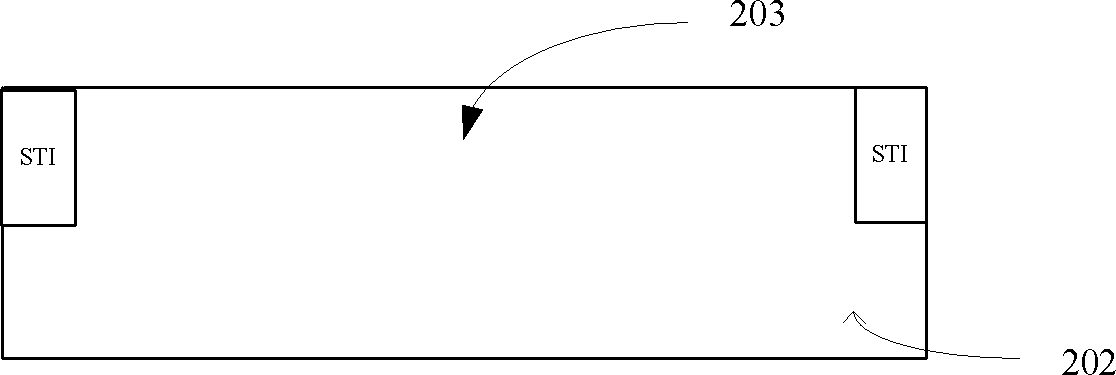

[0014] This embodiment gives the steps of making an NMOS device by using this method. A semiconductor substrate 202 is provided, which may be of any type known in the electronics field, such as bulk semiconductor, semiconductor-on-insulator (SOI). And the semiconductor substrate may be strained, unstrained, or contain strained or unstrained regions therein. After the semiconductor substrate is provided, an isolation region is formed in the semiconductor substrate 202 by using conventional techniques well known in the art. The isolation region is, for example, a trench isolation region (STI) or a field isolation region. In addition, the isolation region material Can be stressed material or unstressed material.

[0015] A channel 203 is formed on the semiconductor substrate in the active region between the isolation regions, such as Figure 2a shown.

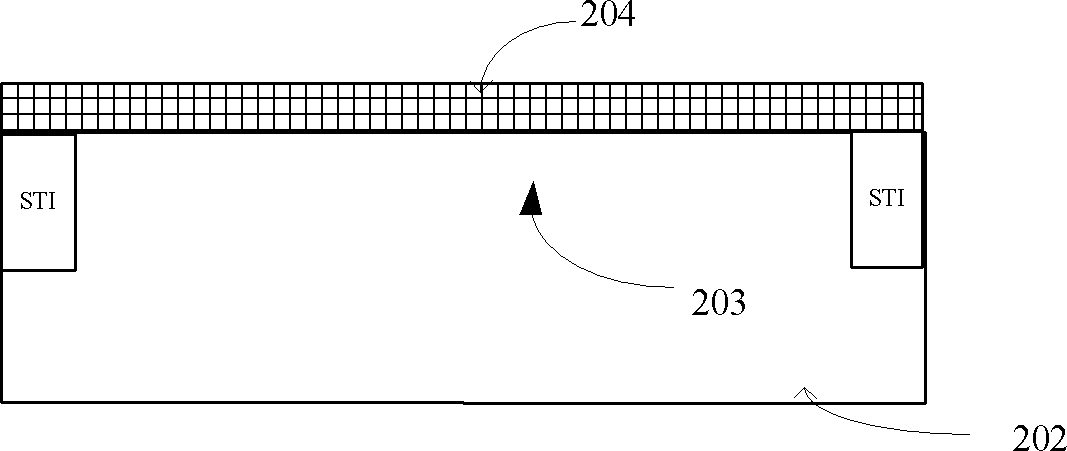

[0016] A gate dielectric layer 204 is formed on the channel, such as Figure 2b As shown, the material of the gate dielectri...

no. 2 example

[0030] This embodiment gives the steps of making a PMOS device by using this method. A semiconductor substrate 302 is provided, and the semiconductor substrate may be of any type known in the field of electronics, such as bulk semiconductor, semiconductor-on-insulator (SOI). And the semiconductor substrate may be strained, unstrained, or contain strained or unstrained regions therein. After the semiconductor substrate is provided, an isolation region is formed in the semiconductor substrate 302 by using conventional techniques well known in the art. The isolation region is, for example, a trench isolation region (STI) or a field isolation region. In addition, the isolation region material Can be stressed material or unstressed material.

[0031] A channel 303 is formed on the semiconductor substrate in the active region between the isolation regions, such as Figure 3a shown.

[0032] A gate dielectric layer 304 is formed on the channel, such as Figure 3b As shown, the ma...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More