Static discharging circuit

An electrostatic discharge circuit and voltage divider circuit technology, applied in circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, emergency protection circuit devices, etc., can solve problems such as affecting the maximum electrostatic discharge capacity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

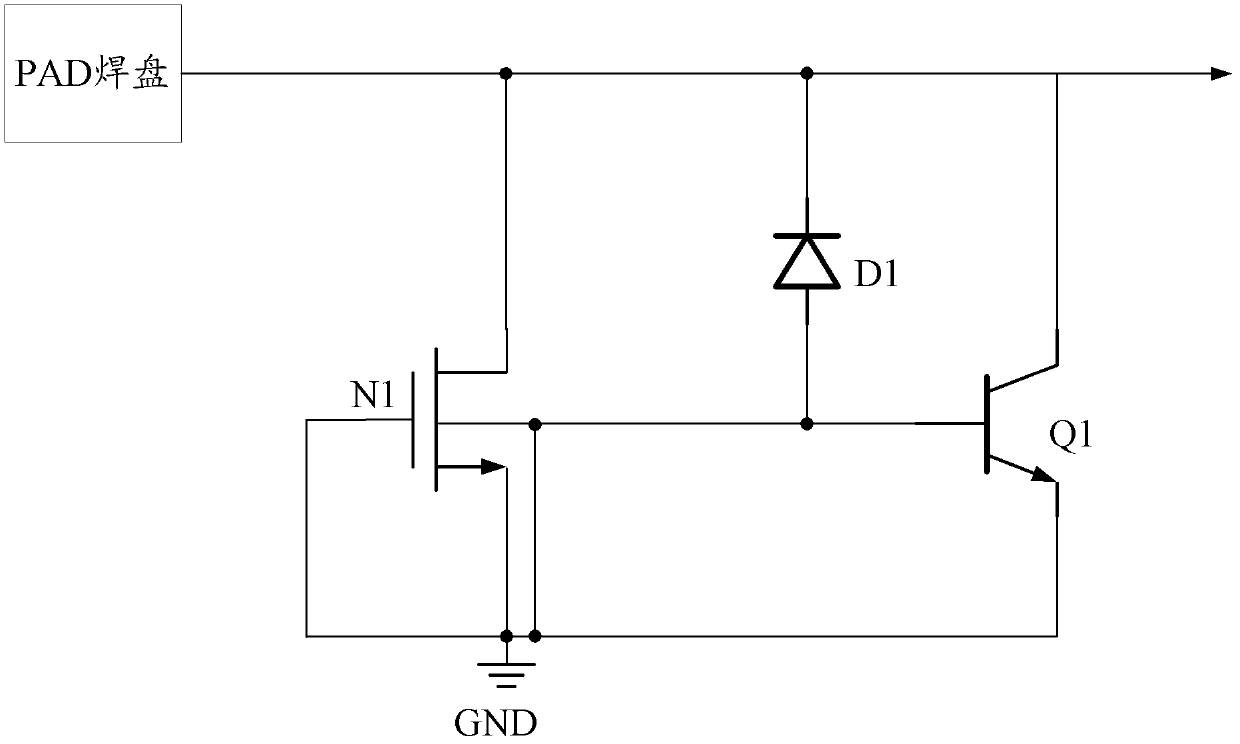

[0037] As mentioned in the background technology, in the prior art, the high-voltage resistance of devices formed by high-voltage technology or BCD technology is limited, and the ESD protection circuit using ordinary technology to stack MOS transistors solves the problem of high-voltage resistance, but it mainly uses parasitic NPN The triode releases the ESD current, which seriously affects its electrostatic discharge capability.

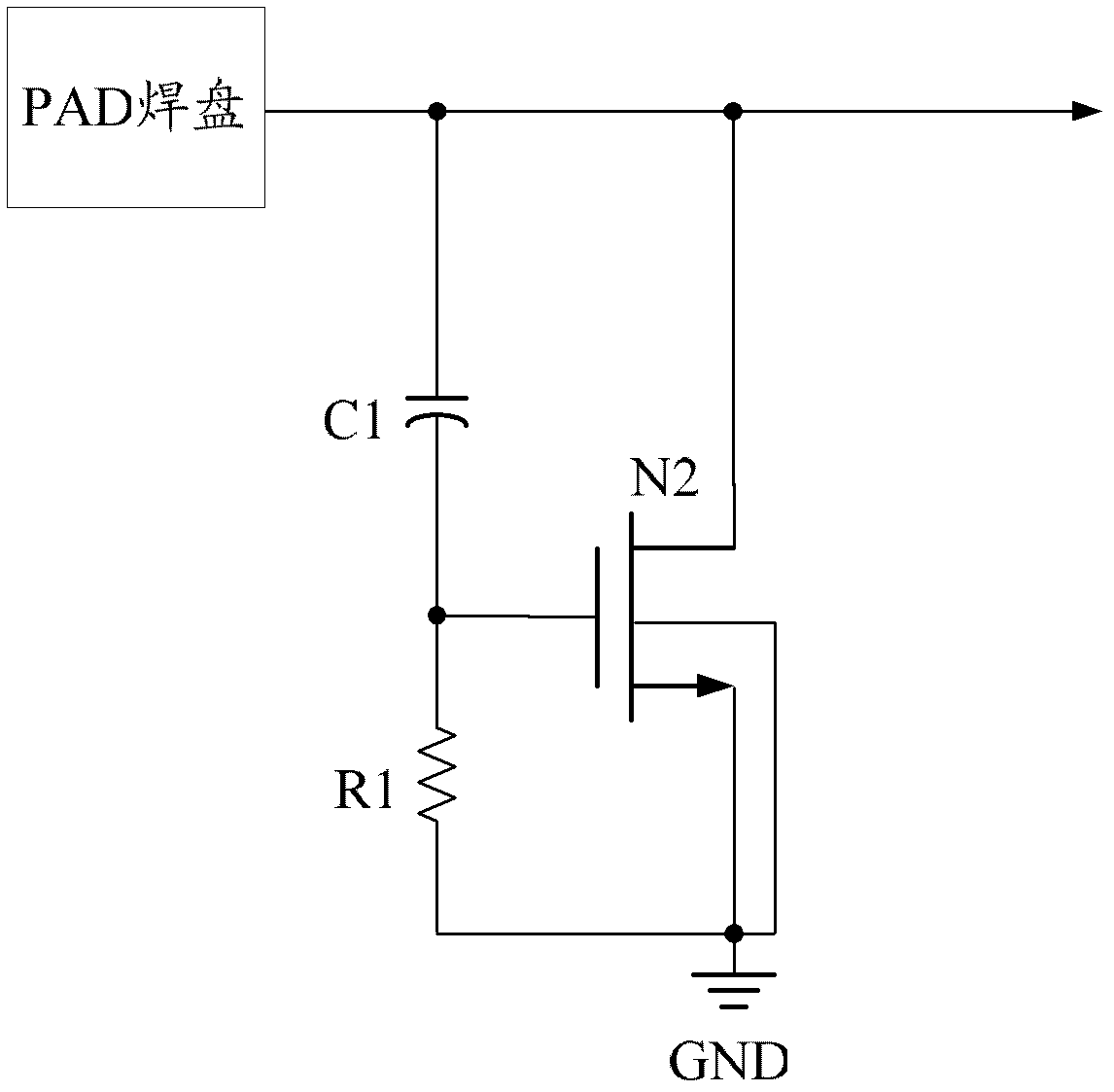

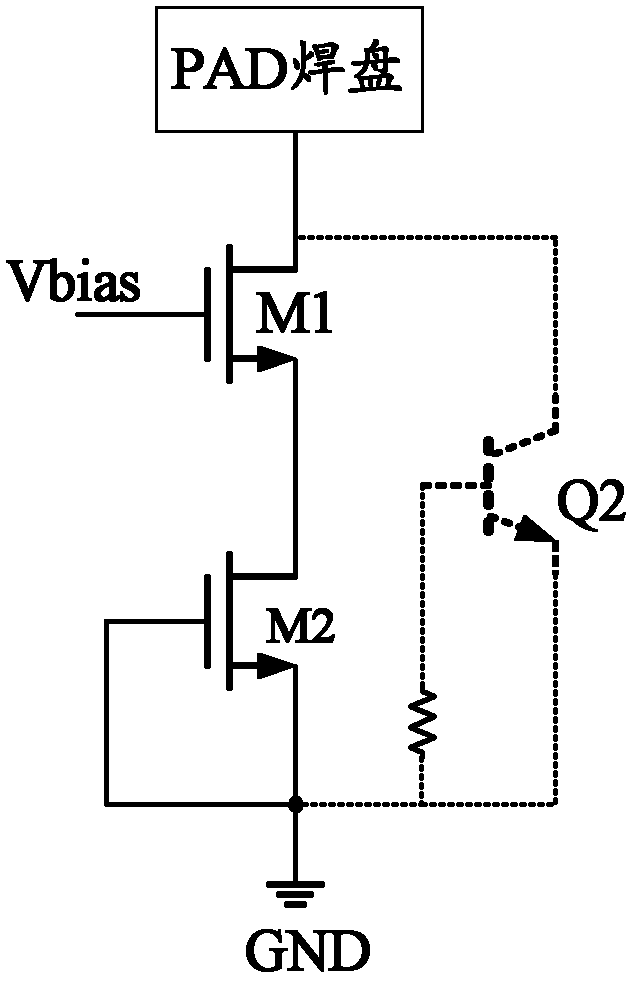

[0038]The electrostatic discharge circuit of the present invention includes a voltage divider circuit, a first NMOS transistor and a second NMOS transistor, and the voltage divider circuit is used to provide an appropriate bias voltage to the first NMOS transistor, so that the first NMOS transistor is in a conduction state; The second NMOS transistor is also quickly turned on during the ESD event, so that the first NMOS transistor and the second NMOS transistor form a path to quickly release the ESD current. In this circuit, the ESD current is relea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More