Check node updating circuit and method of LDPC (low-density parity-check) decoder

A technology for checking nodes and updating circuits, applied in error detection coding using multi-bit parity bits, error correction/detection using block codes, data representation error detection/correction, etc. problems such as power consumption, excessive hardware resources, etc., to achieve the effect of saving quantity, less hardware resources, and benefiting performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

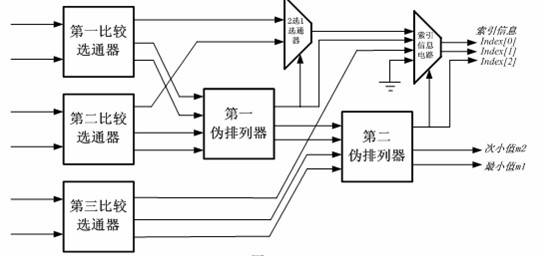

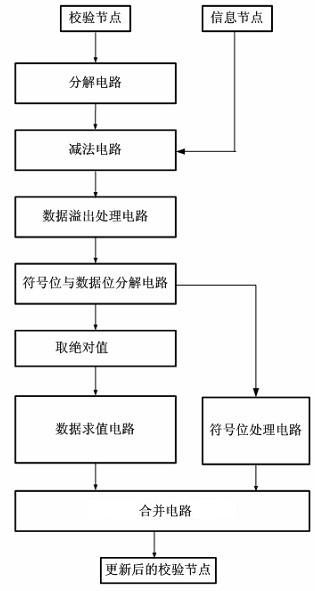

[0043] Such as figure 1 Shown is the flowchart of the check node updating circuit of a kind of LDPC decoder of the present invention:

[0044] A method for updating a check node of an LDPC decoder, comprising the steps of:

[0045] (1) Decompose the 15-bit wide check node rin of the check node information memory into six 6-bit wide information data, which are rin0, rin1, rin2, rin3, rin4, rin5, and the principle of decomposition is Restore the 15-bit wide check node rin that contains the last check node update information; for the check node rin, rin[5:0] represents the sign bits of rin5~rin0 in turn, and rin[8:6] represents The index of the minimum value in rin0~rin5, rin[11:9] represents the value of the second smallest value in rin0~rin5, and rin[14:12] represents the value of the minimum value in rin0~rin5.

[0046] (2) Six 6-bit wide information data are subtracted from six 6-bit wide information nodes in the information node memory to obtain six 6-bit wide output data,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More