Current mirror circuit

A current mirror and circuit technology, applied in the direction of adjusting electrical variables, control/regulating systems, instruments, etc., can solve the problems of long time required to stabilize current and slow discharge time of NMOS tube N1, and shorten the required time and current leakage. Fast and stable effect of release ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

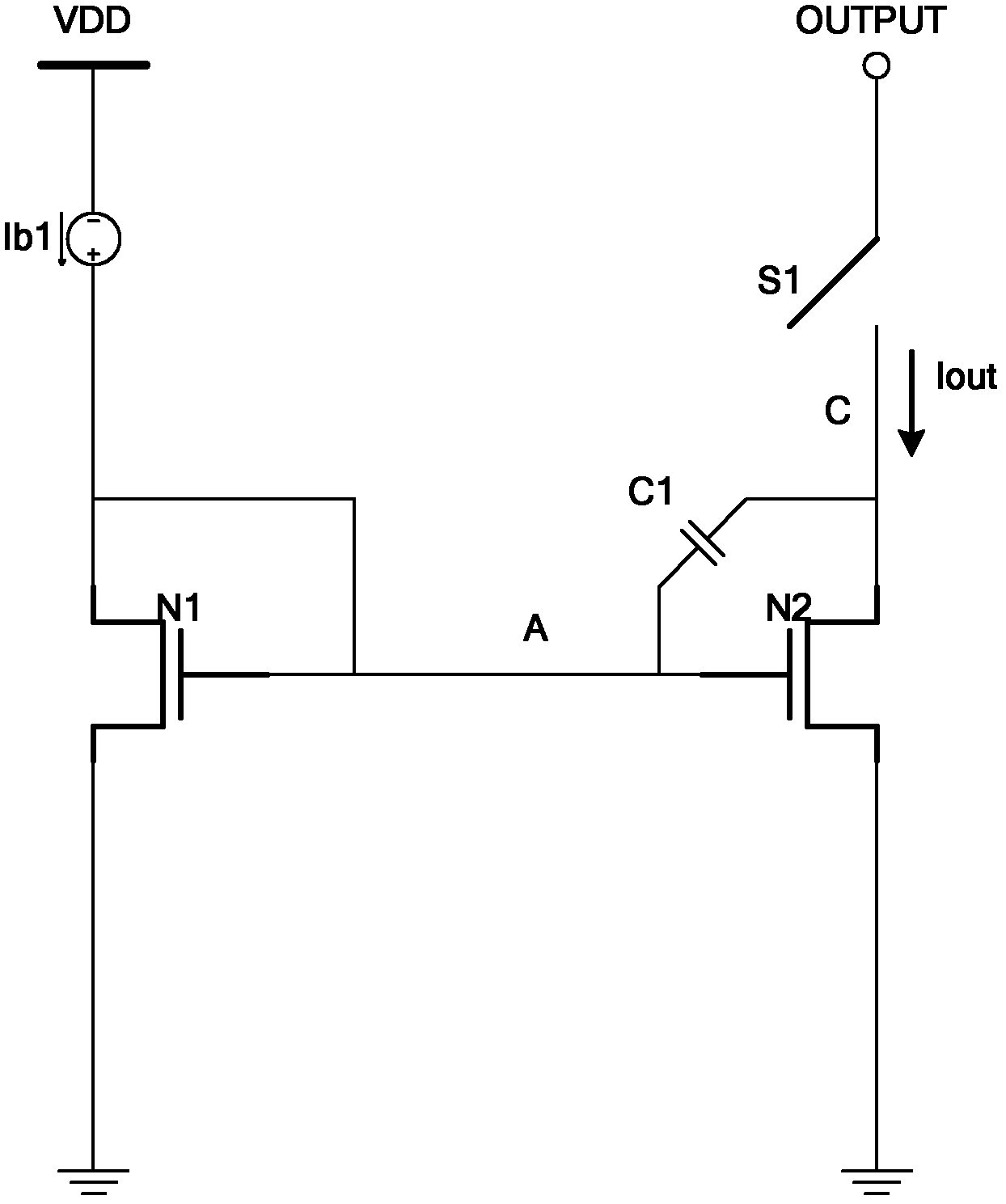

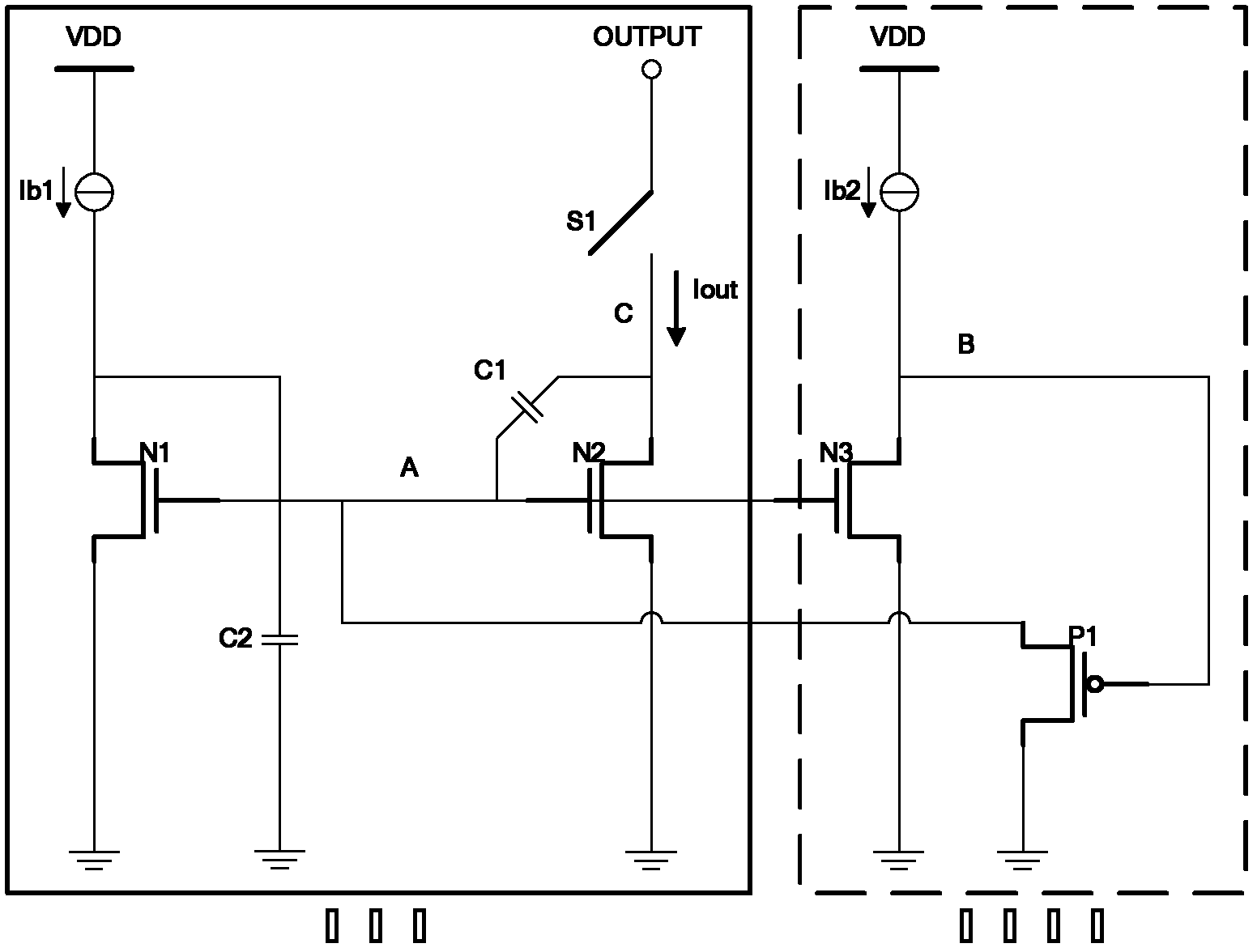

[0027] like figure 2 Shown, the first embodiment of the present invention comprises:

[0028] NMOS transistor N1, its drain is connected to the circuit power supply VDD through the constant current source Ib1, its gate is short-circuited with its drain, its gate is grounded through the capacitor C2, and its source is grounded;

[0029] NMOS transistor N2, its drain is connected to the output terminal OUTPUT through switch S1, its gate is short-circuited with its drain through capacitor C1, and its source is grounded;

[0030] NMOS tube N3, its drain is connected to circuit power supply VDD through constant current source Ib2, its gate is connected to the gates of NMOS tube N1 and NMOS tube N2, and its source is grounded;

[0031] The source of the PMOS transistor P1 is connected to the gate of the NMOS transistor N1, the gate is connected to the drain of the NMOS transistor N3, and the drain is grounded.

[0032] When the output current is not needed, the switch S1 is turne...

no. 2 example

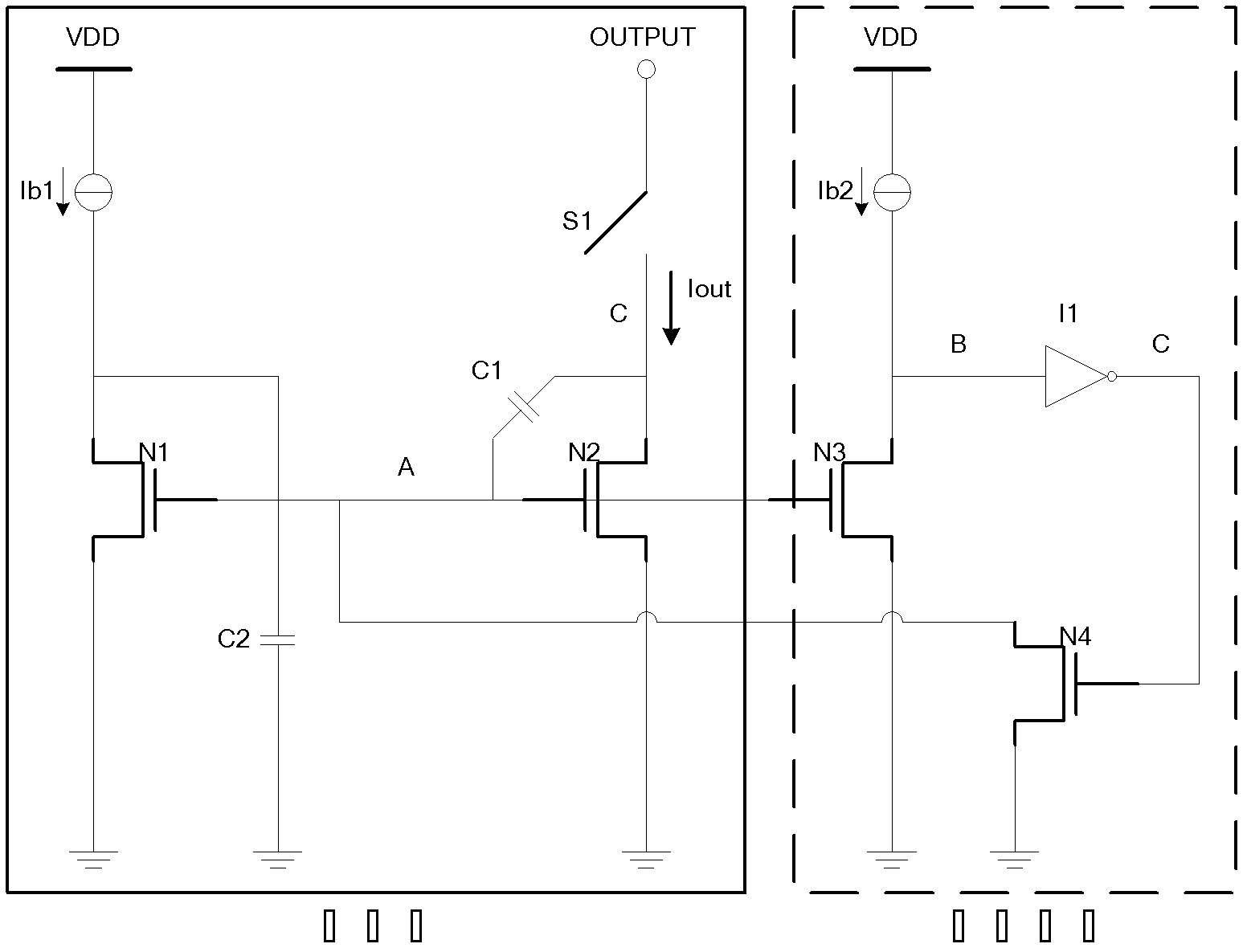

[0034] like image 3 Shown, the second embodiment of the present invention comprises:

[0035] NMOS transistor N1, its drain is connected to the circuit power supply VDD through the constant current source Ib1, its gate is short-circuited with its drain, its gate is grounded through the capacitor C2, and its source is grounded;

[0036] NMOS transistor N2, its drain is connected to the output terminal OUTPUT through switch S1, its gate is short-circuited with its drain through capacitor C1, and its source is grounded;

[0037] NMOS tube N3, its drain is connected to circuit power supply VDD through constant current source Ib2, its gate is connected to the gates of NMOS tube N1 and NMOS tube N2, and its source is grounded;

[0038] NMOS transistor N4, its drain is connected to the gate of NMOS transistor N1, its gate is connected to the drain of MOS transistor N3 through inverting amplifier I1, and its source is grounded;

[0039] The inverting amplifier I1 has its input conn...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More