Thread-aware multi-core data prefetching self-regulation method

A data prefetching and threading technology, applied in the field of performance optimization of multi-core storage systems, can solve problems such as affecting cache hits, and achieve the effect of improving hit rate and reducing competition.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

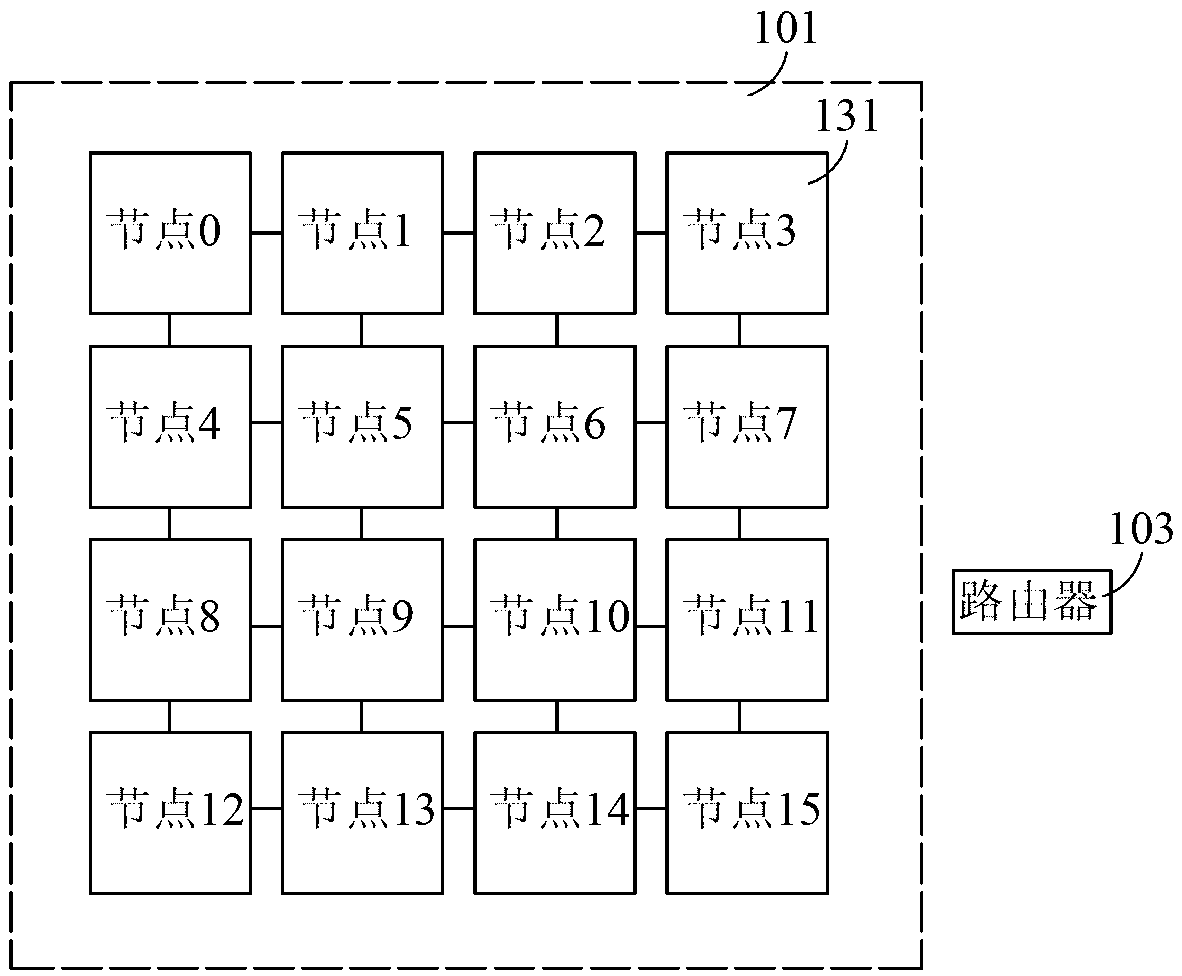

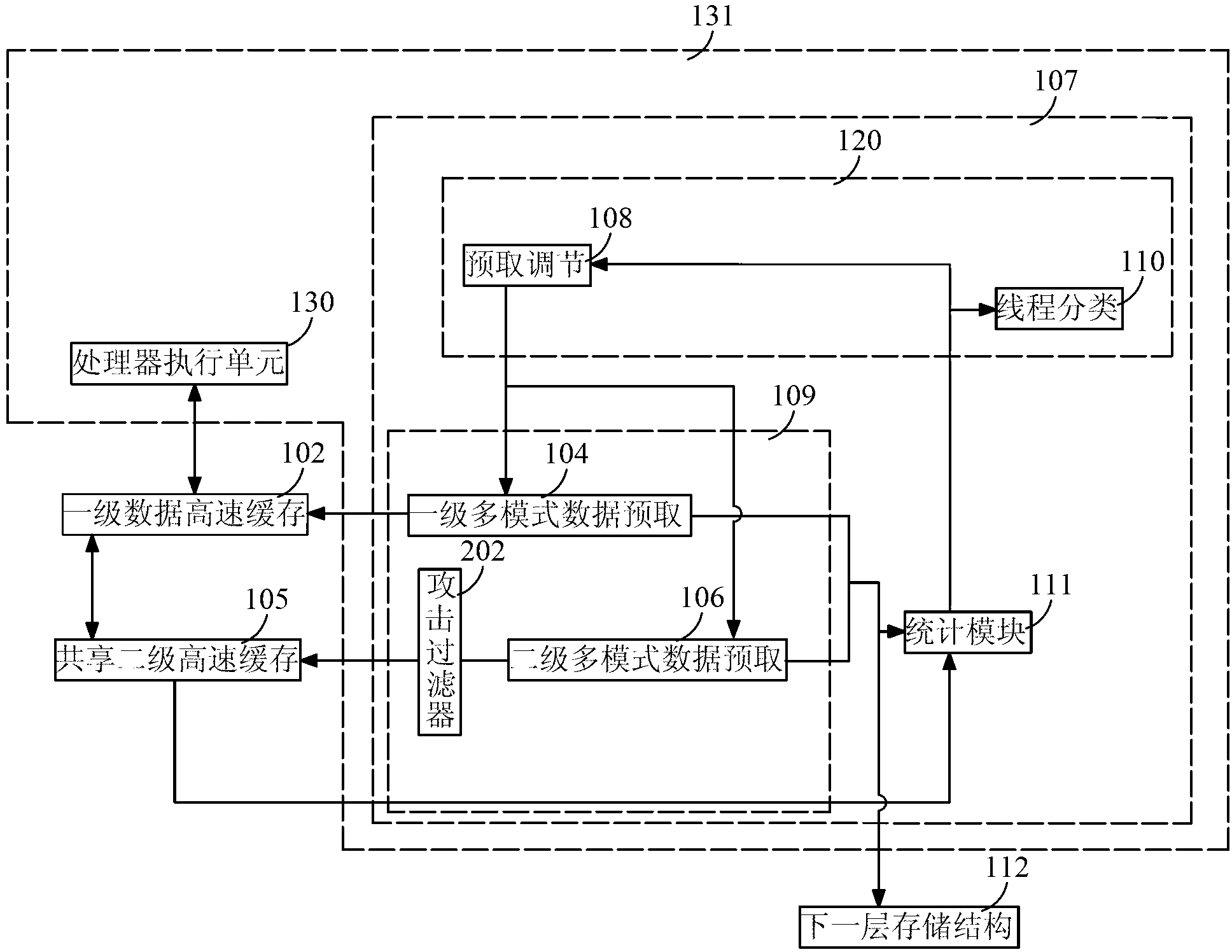

[0021] Embodiment 1, figure 1 and figure 2 Combined with a thread-aware multi-core data prefetch self-adjustment method; including a multi-core thread-aware multi-core data prefetch device; such as figure 1 As shown, the multi-core thread-aware multi-core data prefetching device includes multiple (at least two) processors 101 and routers 103; the processors 101 and the processors 101 are connected through an on-chip interconnection network.

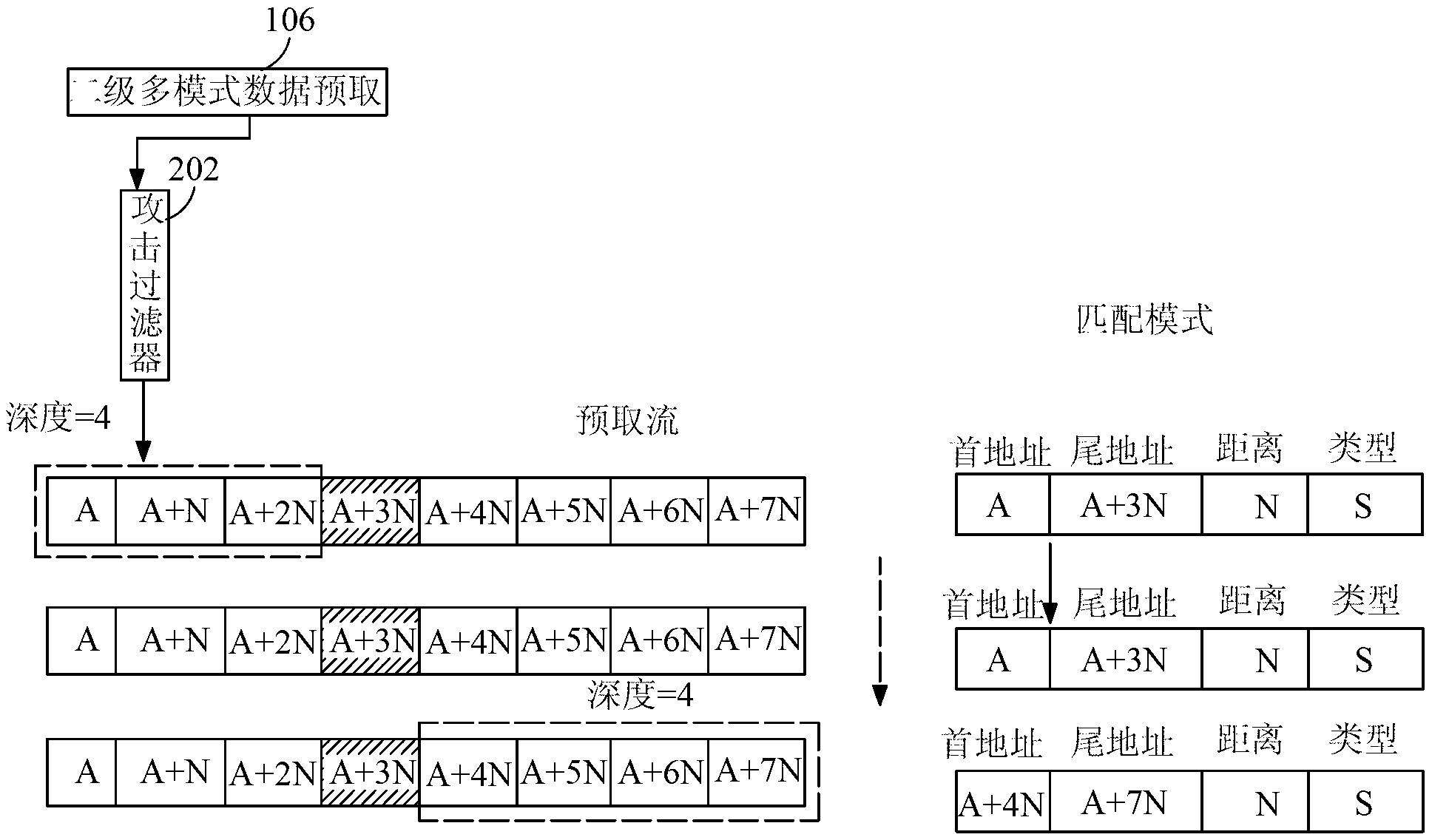

[0022] Such as figure 2 As shown, each processor 101 includes a number of nodes 131 (ie Tile), a number of L1 caches (ie figure 1 in the L1 data cache 102) and a L2 cache (i.e. figure 1 Shared L2 cache 105 in ), each node 131 has a one-to-one correspondence with each L1 cache, that is, each node 131 independently owns a private L1 data cache 102; all nodes 131 Both share the L2 cache (that is, share the L2 cache 105, which is assumed to be the last cache LLC on the chip), several nodes 131 (Tile), several L1 caches and a L2 cache ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More