Thread group address space scheduling and thread switching method under multi-core environment

An address space and thread group technology, applied in the computer field, can solve problems such as poor flexibility, achieve the effect of improving the Cache hit rate, reducing the number of address space switching, and improving the overall performance of the system

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

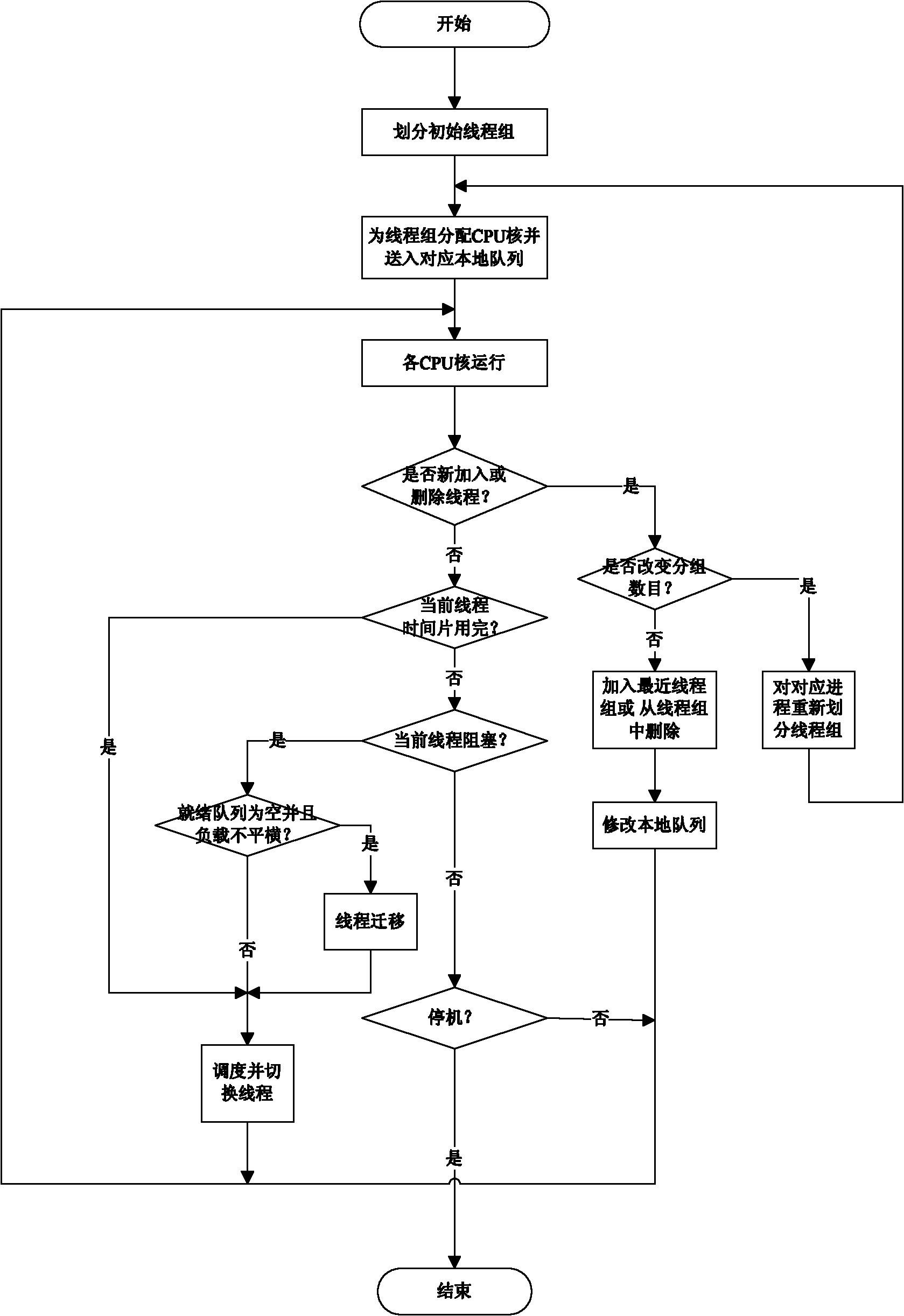

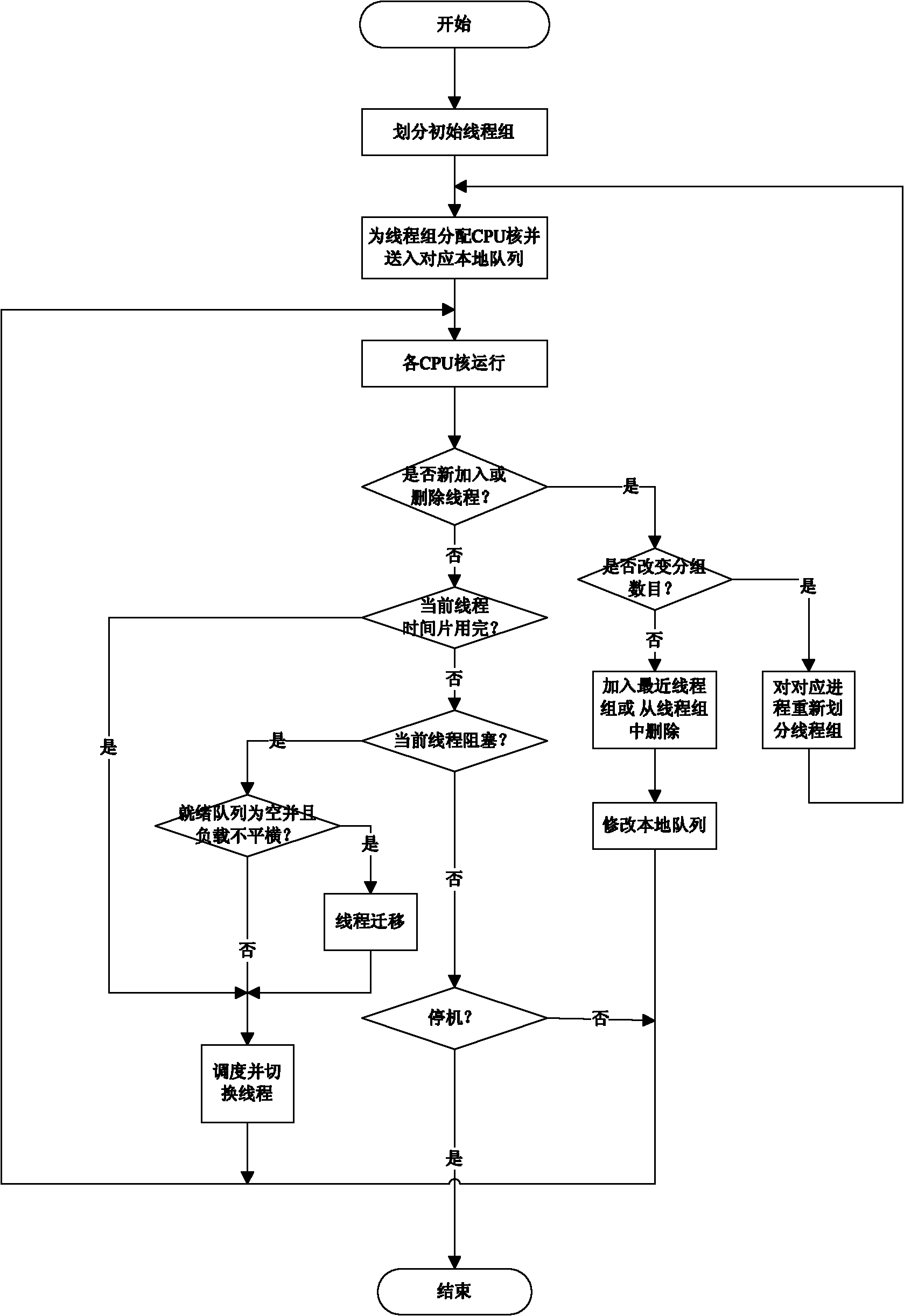

[0035] Such as figure 1 As shown, this embodiment includes the following steps:

[0036] In the first step, the threads included in each process are divided into thread groups to obtain several thread groups.

[0037] The described thread group division process includes the following steps:

[0038] 1.1) According to Get the number of thread groups divided by each process, where: P i Is the number of thread groups divided by the i-th thread, A is the number of cores of the processor, B i is the parallelism factor of the i-th thread, C i Is the number of threads of the i thread, the total number of threads of all threads in D;

[0039] 1.2) The sum of the thread instruction access mode difference and the thread data access mode difference is used as a difference function between threads;

[0040] 1.3) The K-medoids clustering method is used to divide the thread groups.

[0041] In the second step, the thread group is allocated, the CPU cores of each thread group are res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More