Address mapping method for flash translation layer of solid state drive

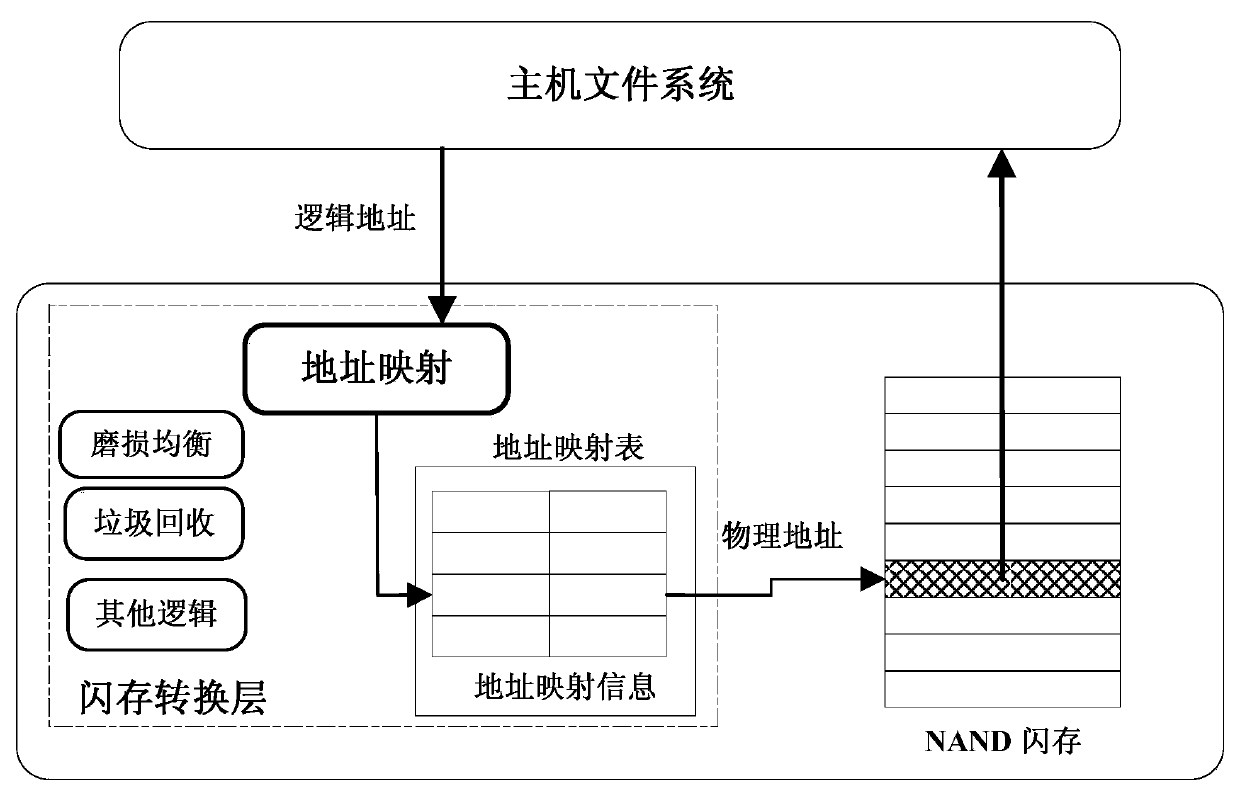

An address mapping and translation layer technology, applied in the direction of memory address/allocation/relocation, etc., can solve the problem of limited erasing times of memory cells, NANDFlash cannot directly update data blocks like disks, and cannot ensure data integrity in data blocks. correctness, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

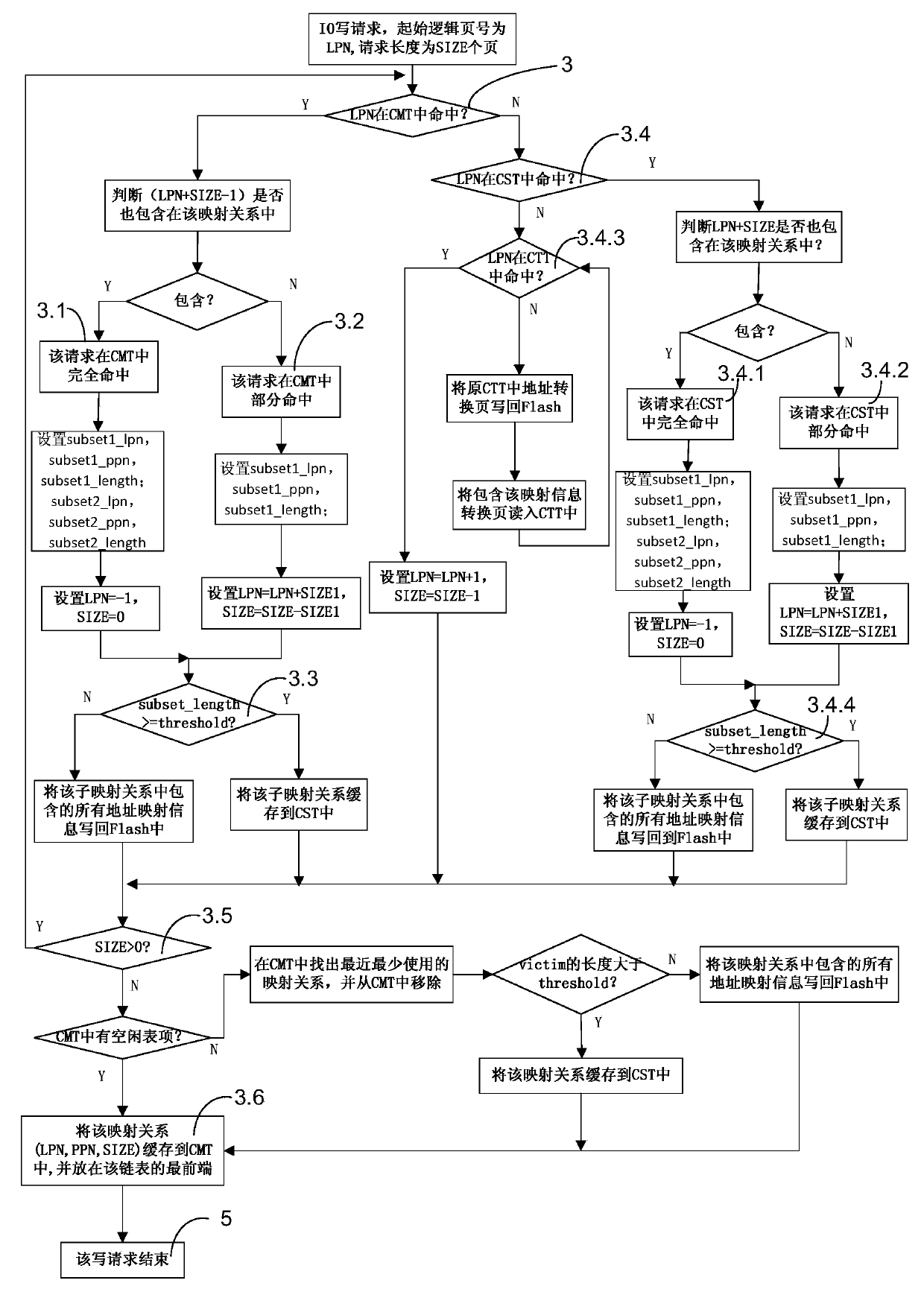

[0055] The implementation steps of the address mapping method in the flash memory translation layer of the solid state disk in this embodiment are as follows:

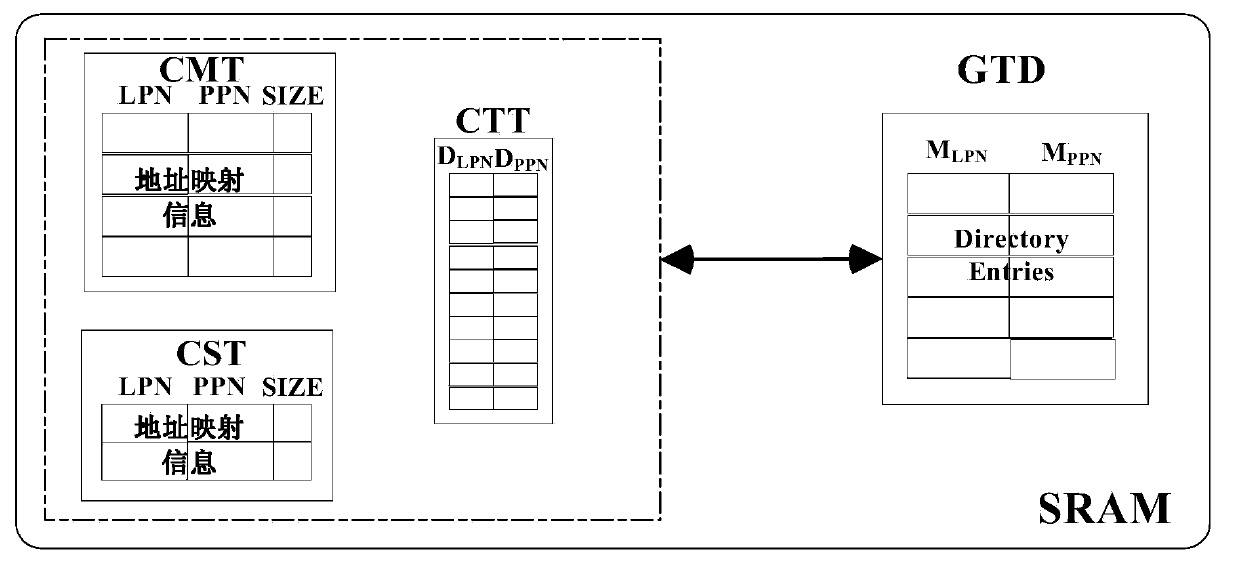

[0056] 1) Establish the cache mapping table (CachedMappingTable, CMT), cache split table (CachedSplitTable, CST), cache translation table (CachedTranslationTable, CTT) and global translation directory (GlobalTranslationDirectory, GTD) in the SRAM of the solid-state disk in advance, and the cache mapping table CMT The cache split table CST has three entry fields: the start logical page number (LogicalPageNumber, LPN), the start physical page number (PhysicalPageNumber, PPN), and the length (SIZE). The cache conversion table CTT has a logical page number D LPN and physical page number D PPN A total of two entry fields, the global translation directory GTD has a logical page number M LPN , logical page number M LPN The physical page number M stored in the SSD Flash PPN A total of two entry fields.

[0057] Such as f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More