Patents

Literature

85results about How to "Reduce read and write operations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Data access method for solid state disk

ActiveCN101673188AReduce read and write operationsExtended service lifeInput/output to record carriersMemory adressing/allocation/relocationPhase-change memoryAccess method

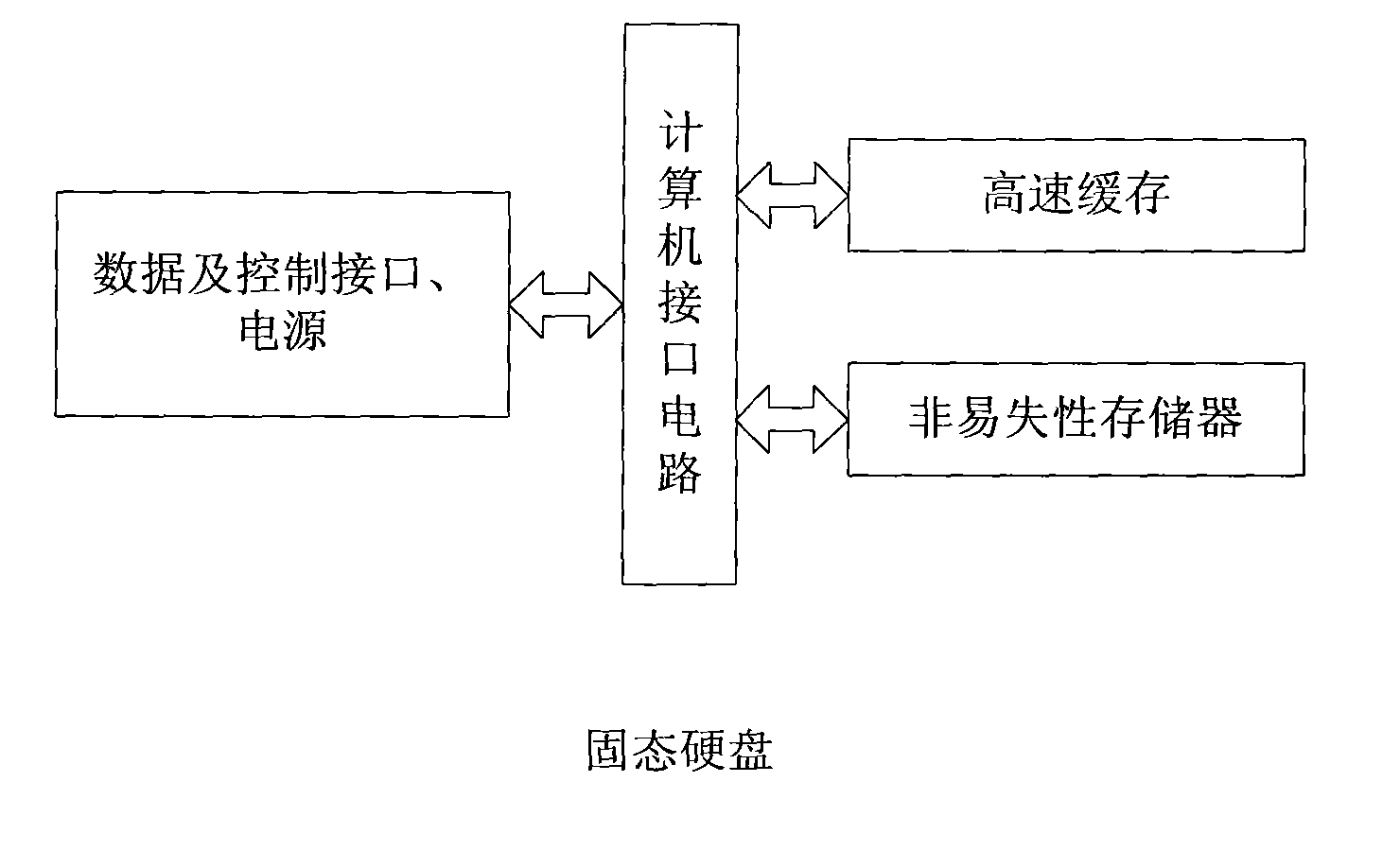

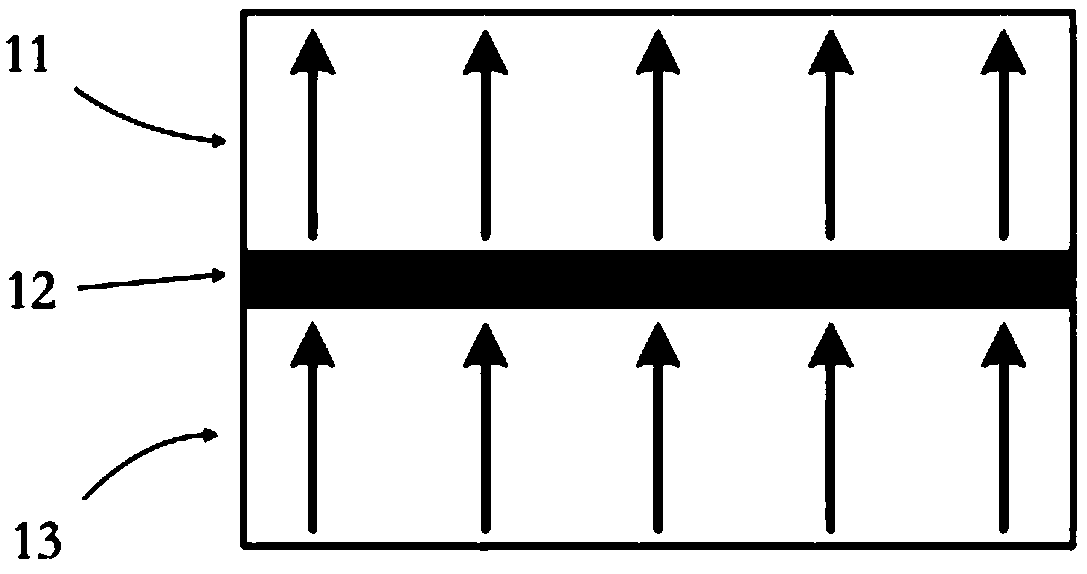

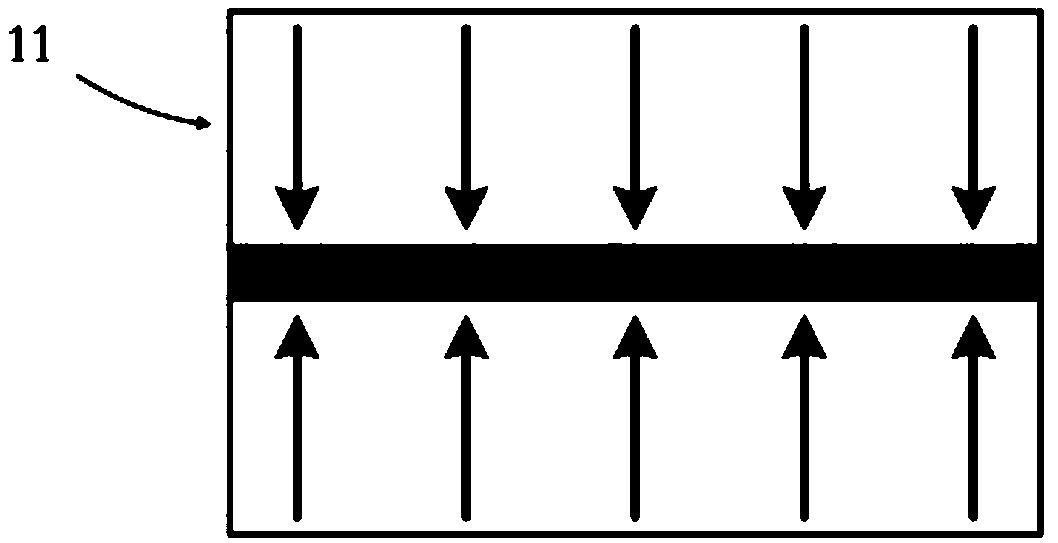

The invention discloses a data access method for a solid state disk. The solid state disk comprises a cache and a nonvolatile memory, wherein the cache consists of DRAM or SRAM, and the nonvolatile memory consists of a flash memory and a phase-change memory or a magnetic memory. The data access method comprises the following steps: when writing data, firstly saving the data into the cache, and then saving the data into the nonvolatile memory; when reading the data, firstly reading the data from the cache, and then reading the data from the nonvolatile memory. The method divides the cache intoa plurality of data blocks, and records the write-in times, reading times and marks of the data blocks in the cache; and the method divides the nonvolatile memory into a plurality of data blocks, andrecords the write-in times, reading times and marks of the data blocks in the nonvolatile memory. By balancing the read-write load of each data block, the data access method for the solid state disk effectively prolongs the service life of the solid state disk, improves the data read-write efficiency, and ensures the security of storing the data.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Local data updating method based on erasure code cluster storage system

InactiveCN102681793ASave bandwidthReduce transmissionInput/output to record carriersRedundant data error correctionOperating systemData node

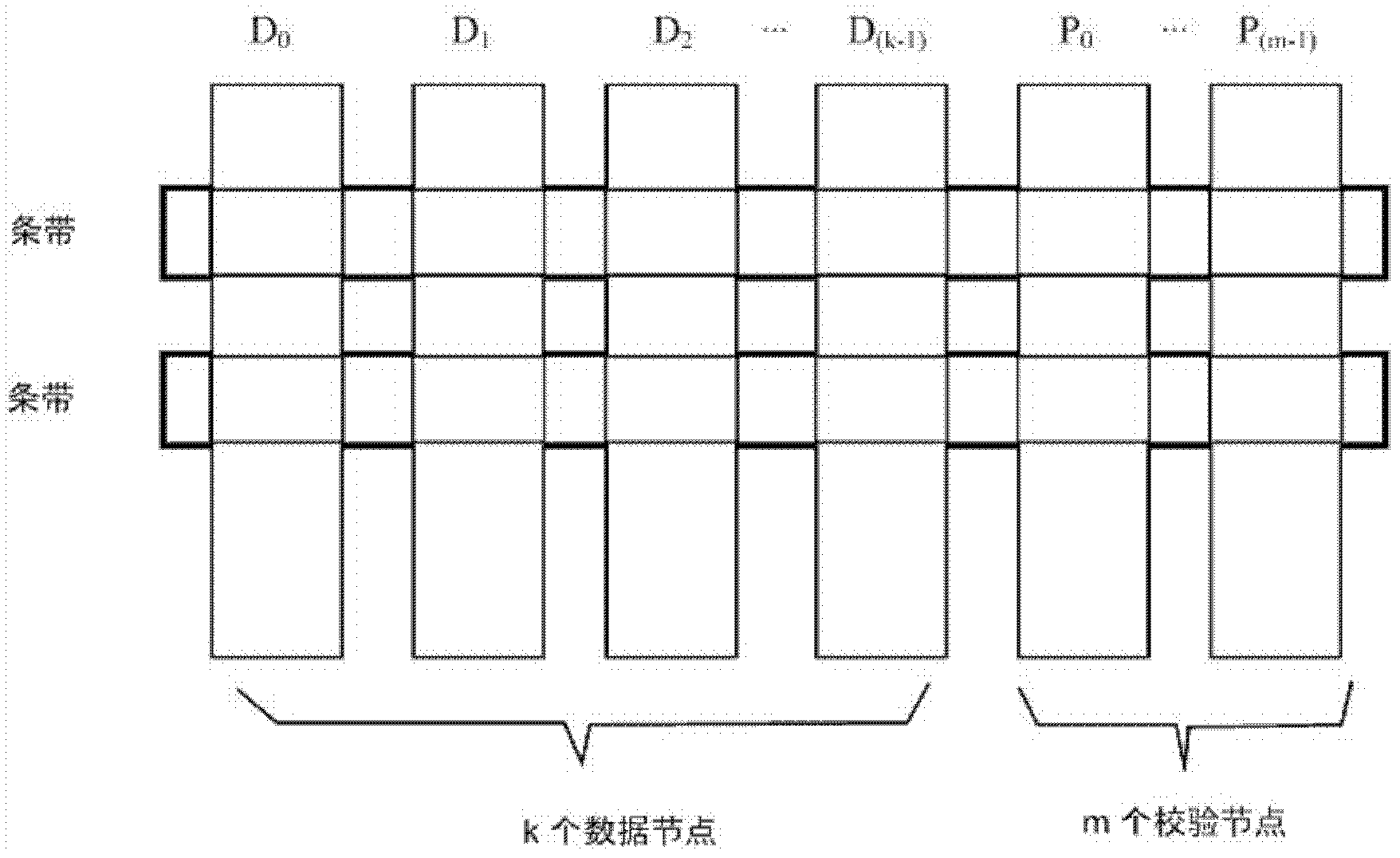

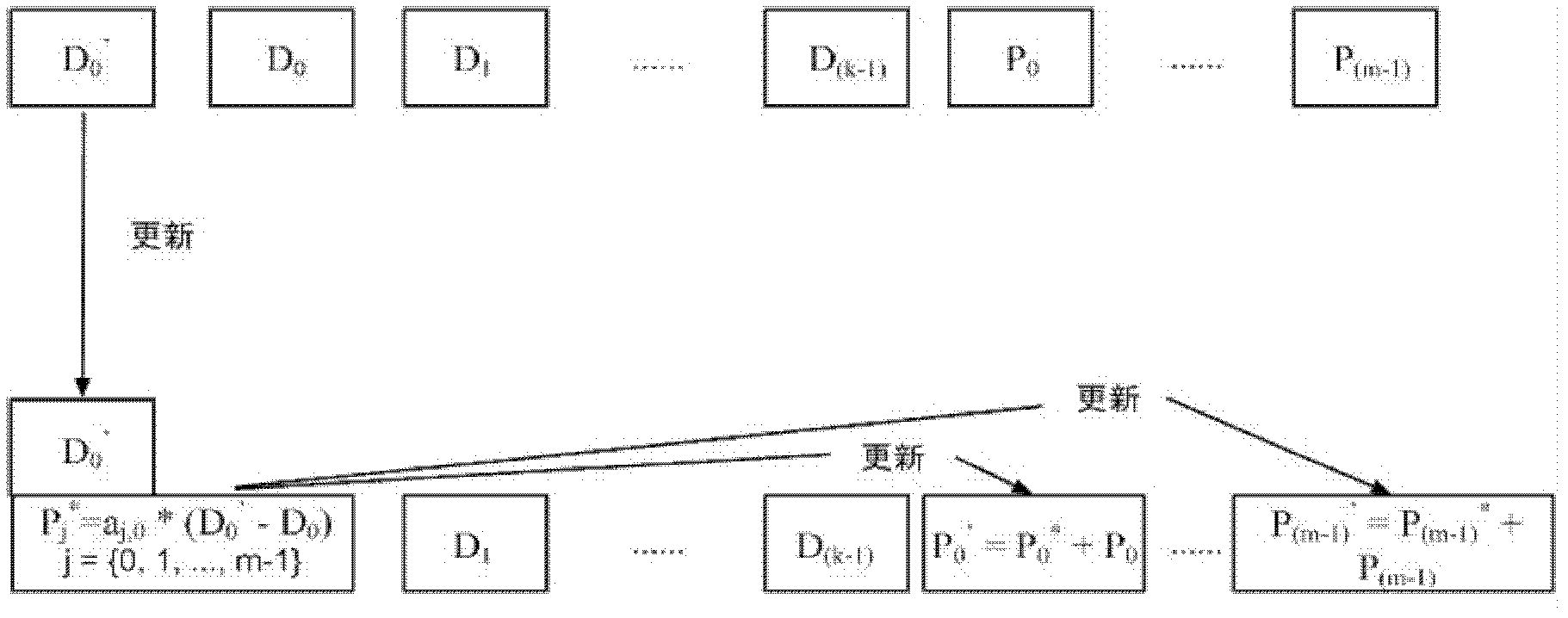

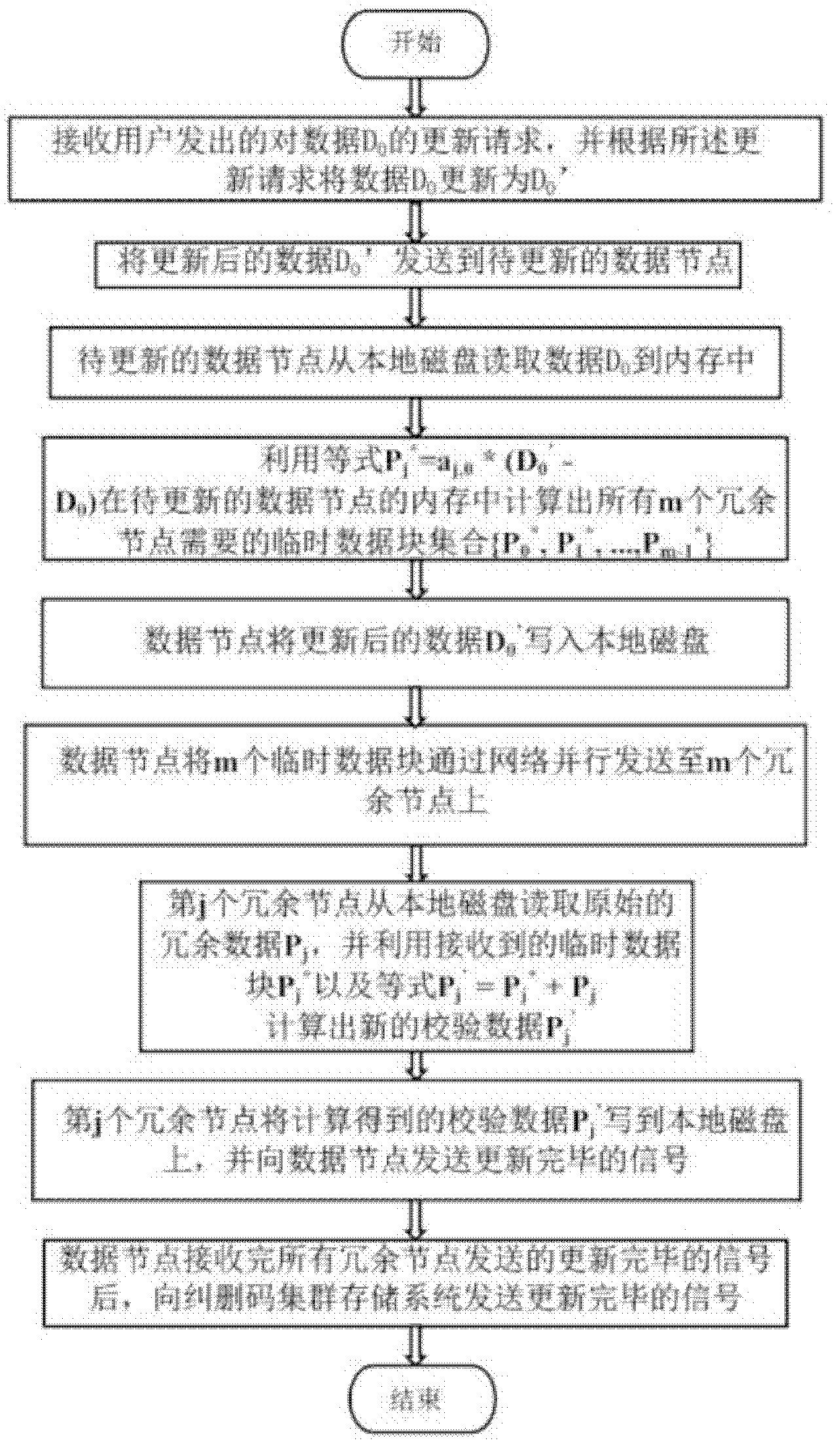

The invention discloses a local data updating method based on an erasure code cluster storage system, which comprises the following steps: receiving a data D0 updating request sent by a user; updating a data D0 into a data D0'; sending the data D0' to a data node to be updated; reading the data D0' from a local disc to a memory by the data node to be updated; calculating a provisional data block set needed by m redundant nodes in the memory of the data node to be updated; writing the data D0' into the local disc by the data node to be updated; sending m provisional data blocks onto the m redundant nodes by the data node to be updated through the network at the same time; reading an original redundant data Pj by the j redundant node from the local disc, and calculating to obtain a new check data Pj'; and writing the check data block Pj' obtained through calculating into the local disc by the redundant node. Due to the adoption of the local data updating method based on the erasure code cluster storage system, the consumption of the bandwidth can be reduced effectively, the load pressure of the update server can be decreased, and the data updating performance can be improved.

Owner:HUAZHONG UNIV OF SCI & TECH

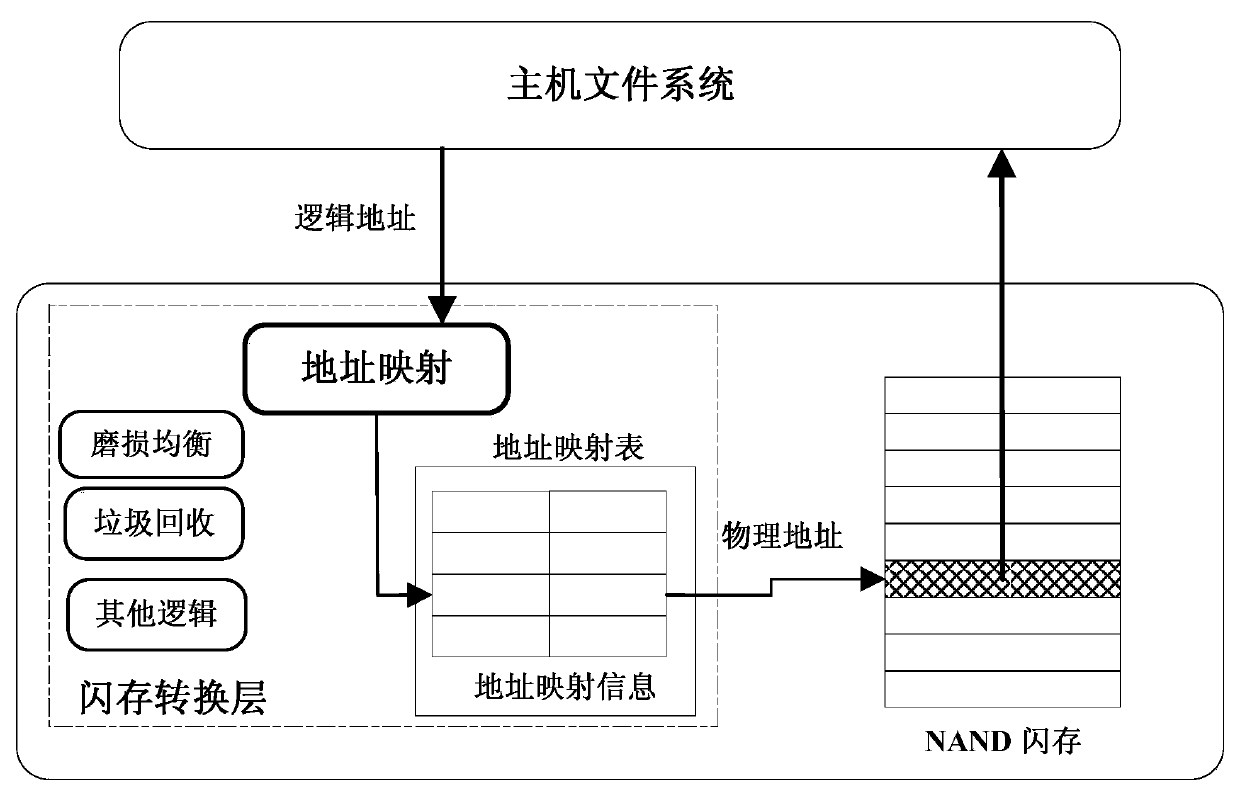

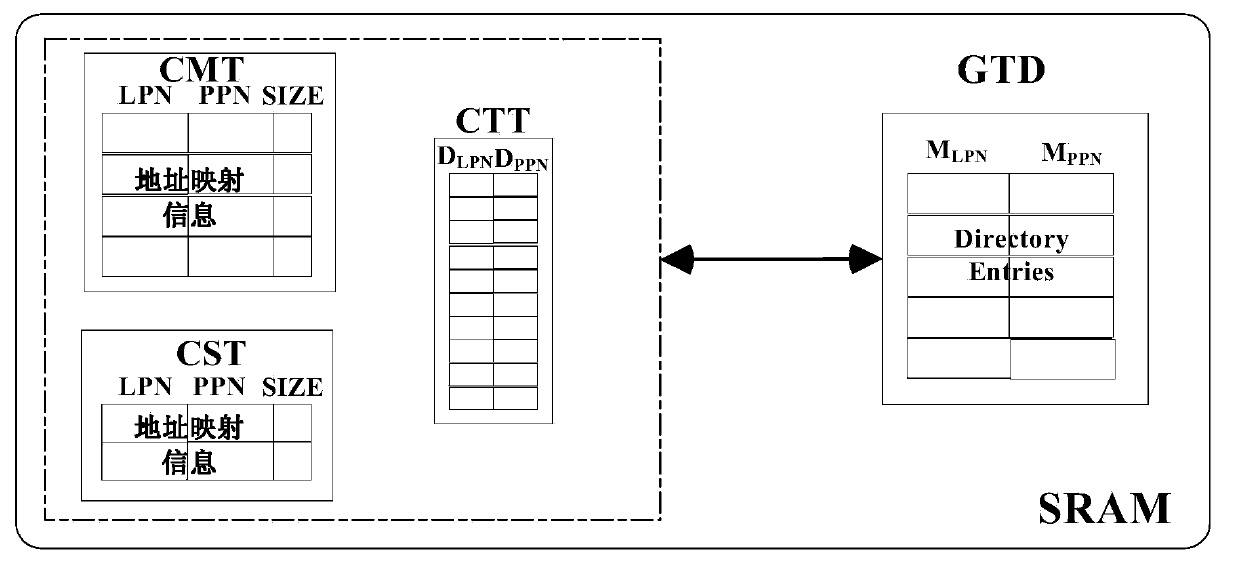

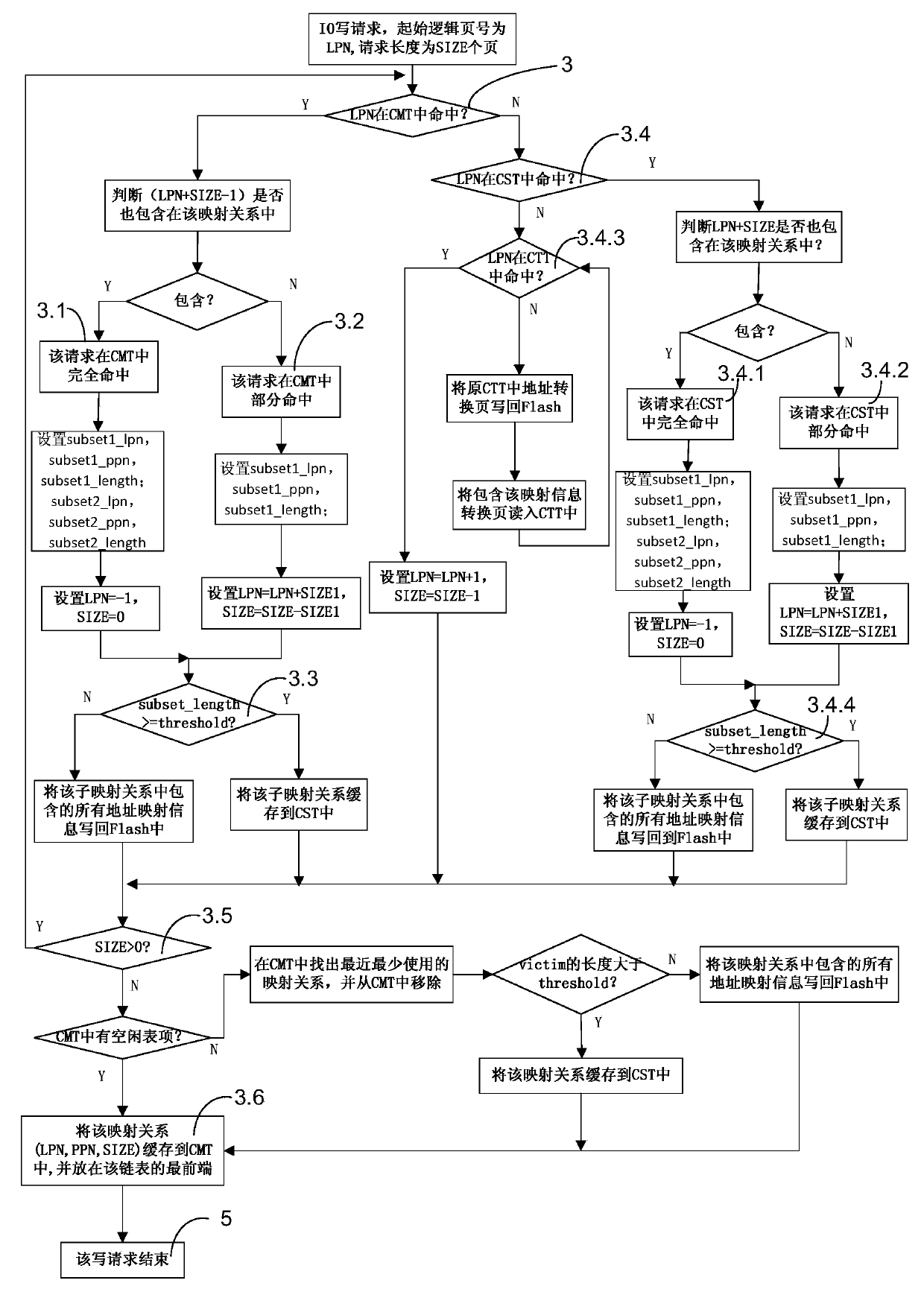

Address mapping method for flash translation layer of solid state drive

ActiveCN103425600AImprove random write performanceImprove hit rateMemory architecture accessing/allocationMemory adressing/allocation/relocationStatic random-access memorySolid-state drive

The invention discloses an address mapping method for a flash translation layer of a solid state drive. The method comprises the following steps of (1) establishing a cached mapping table, a cached split table, a cached translation table and a global translation directory in an SRAM (static random access memory) in advance; (2) receiving an IO (input / output) request, turning to a step (3) if the IO request is a write request, otherwise turning to a step (4); (3) preferentially and sequentially searching the tables in the SRAM for the hit condition of the current IO request, finishing write operation according to hit mapping information, and caching the mapping information according to a hit type and a threshold value; (4) preferentially searching the tables in the SRAM for the hit condition of the current IO request, and finishing read operation according to the hit mapping information in the SRAM. The method has the advantages that the random write performance of the solid state drive can be improved, the service life of the solid state drive can be prolonged, the efficiency of the flash translation layer is high, the hit ratio of address mapping information in the SRAM is high, and less additional read-write operation between the SRAM and the solid state drive Flash is realized.

Owner:NAT UNIV OF DEFENSE TECH

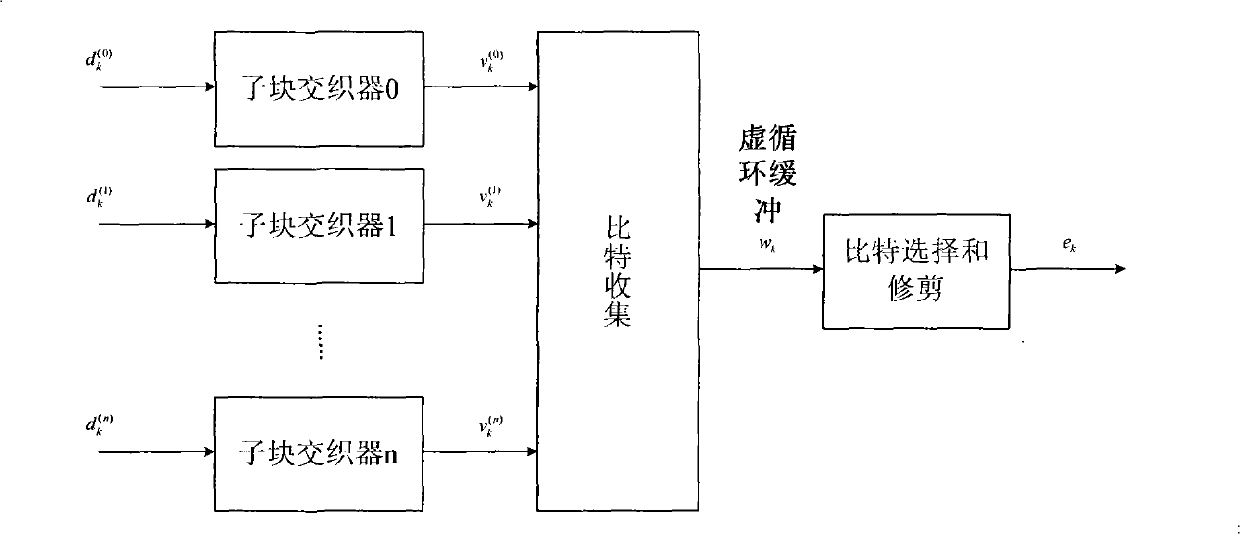

Method for interlacing rate matching and de-interlacing off-rate matching

InactiveCN101540654AReduce read and write operationsError preventionNetwork traffic/resource managementComputer scienceOff rate

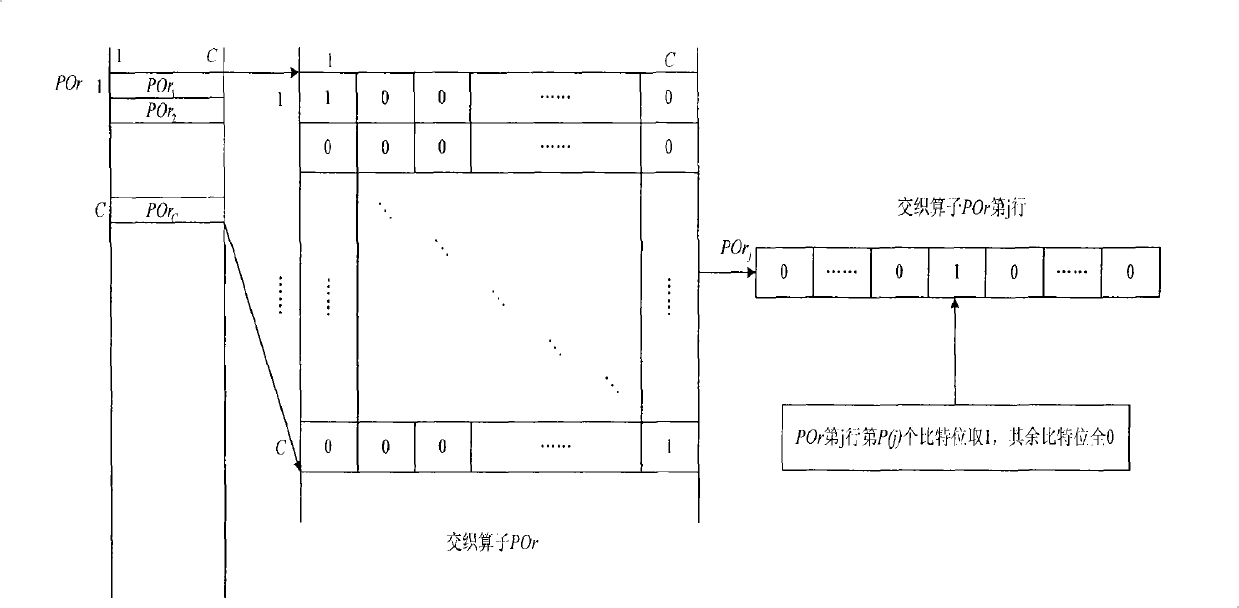

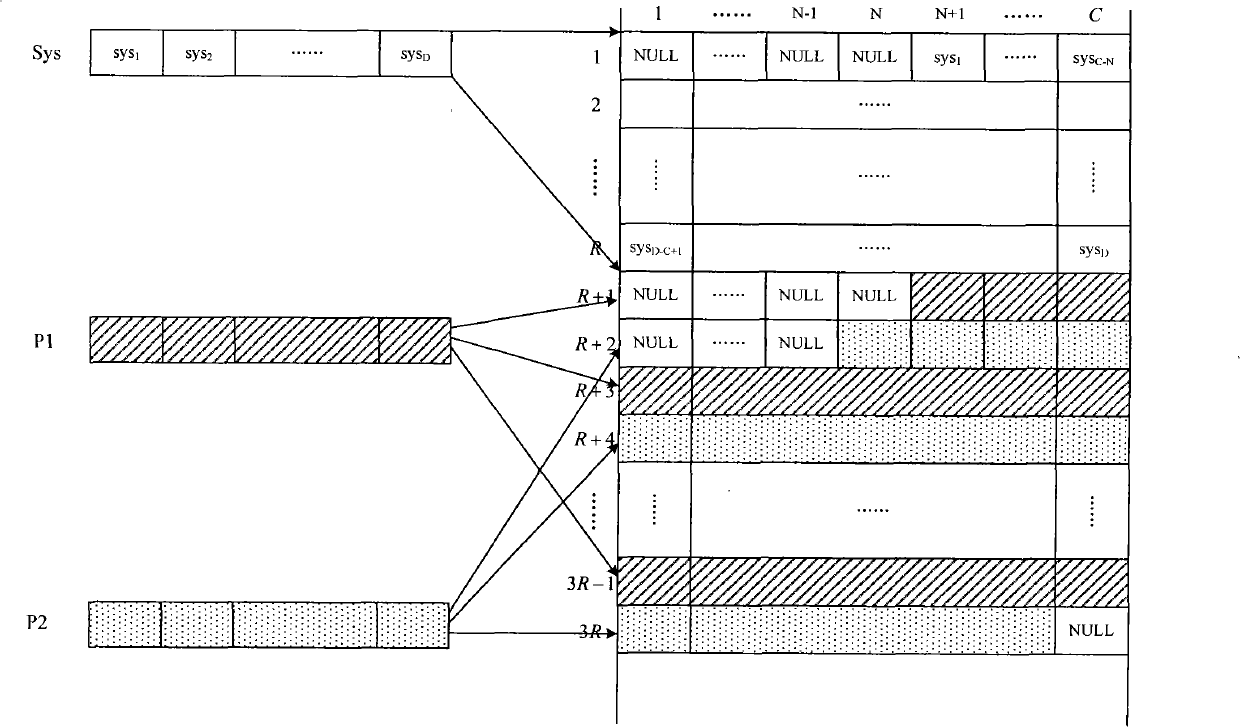

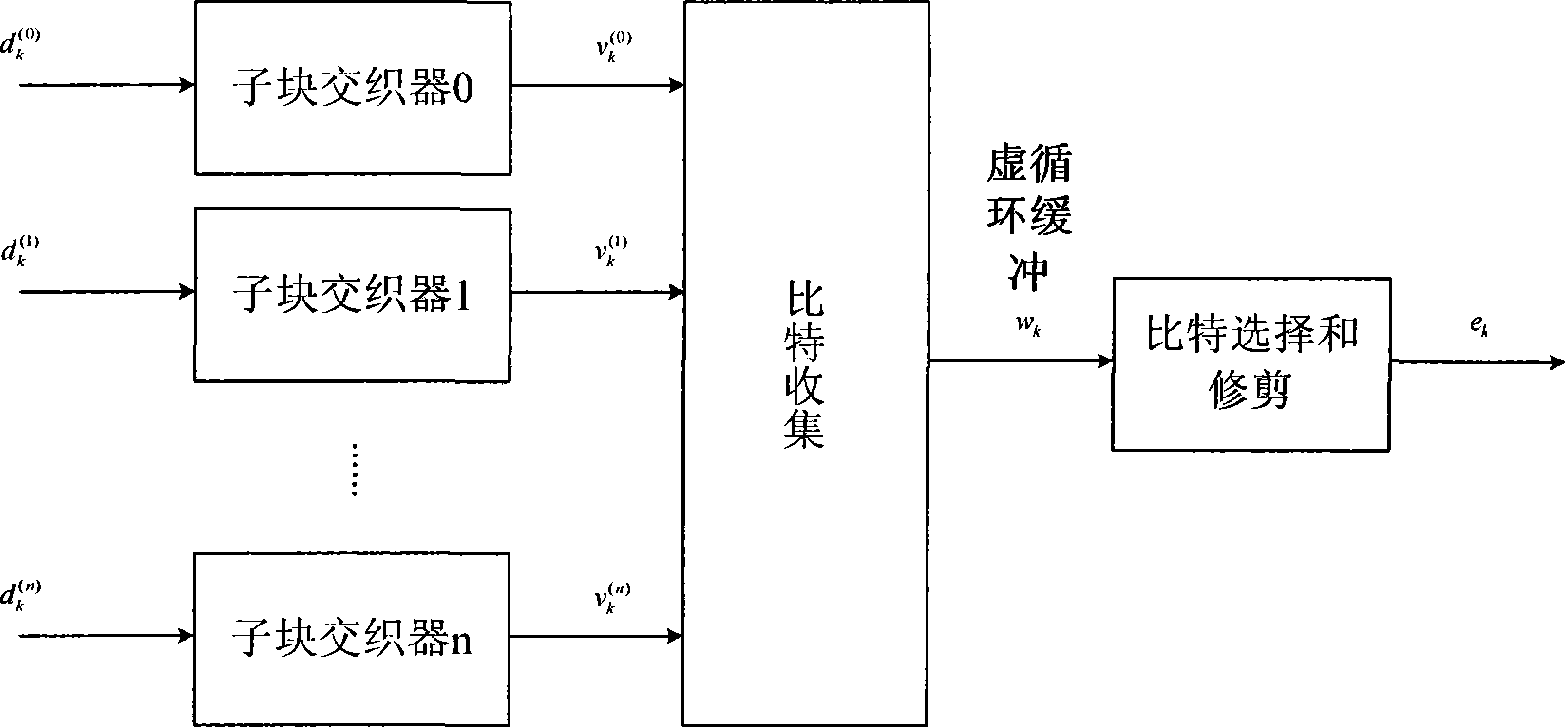

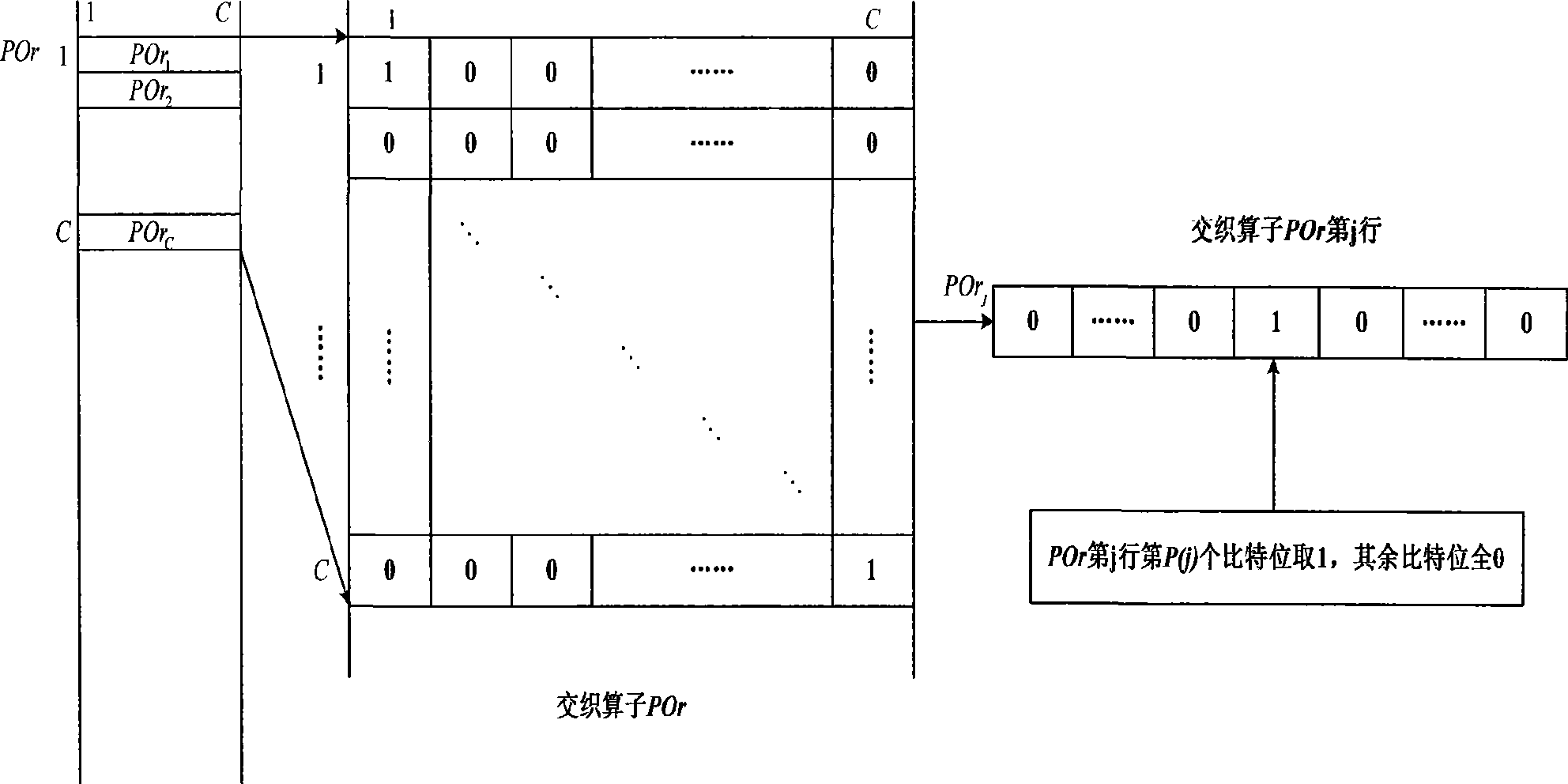

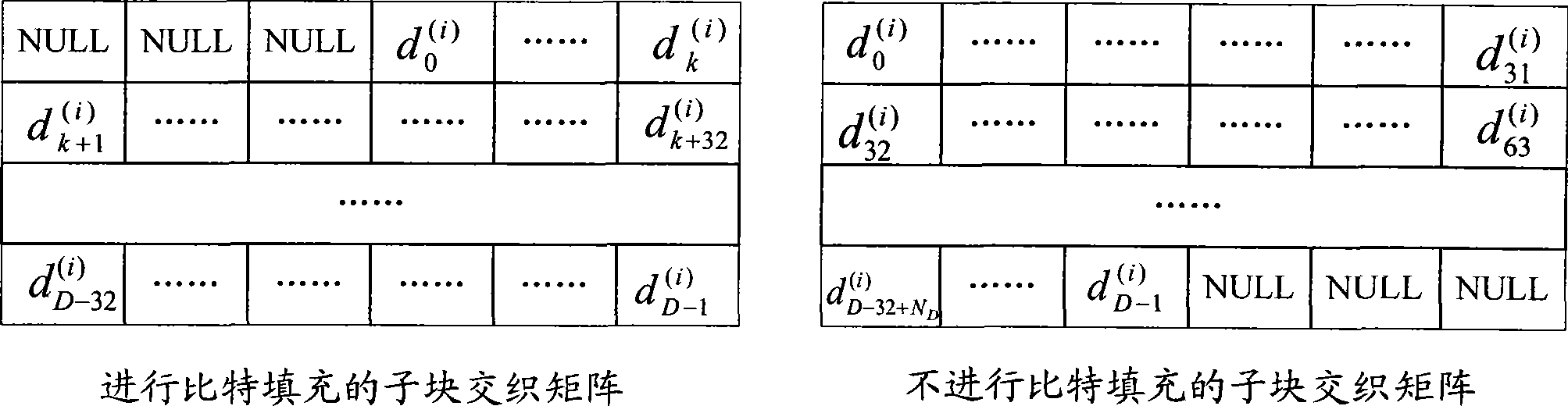

The invention discloses an interlacing matching method. The method determines interlacing operators according to a column interlacing mode, and uses the sequence of the interlacing operators to carry out interlacing processing for a sub-block interlacing matrix, wherein in one mode, the method uses the interlacing operators to carry out the interlacing processing for bits needing to be output in the sub-block interlacing matrix according to the requirement of a redundancy version, and directly outputs sub-block interlacing results ordered by a protocol at the same time of finishing sub-block interlacing till reaching corresponding code rate requirement; and in the other mode, the method can use the interlacing operators to carry out the interlacing processing for the sub-block interlacing matrix one by one, outputs sub-block interlacing results ordered by the protocol to a cyclic buffer at the same time of finishing sub-block interlacing, and outputs corresponding interlaced bits according to the requirement of the redundancy version. Moreover, the invention also discloses a de-interlacing off-rate matching method corresponding to the interlacing rate matching method. The method can be applied to interlacing rate matching and de-interlacing off-rate matching, and greatly reduces used caches and read-write operations for the caches.

Owner:POTEVIO INFORMATION TECH CO LTD

Interleaving and rate matching and de-interleaving and rate de-matching methods

InactiveCN101547064AReduce read and write operationsError preventionMatching methodsComputer science

The invention discloses an interleaving and rate matching method. A correction interleaving mode is determined according to a column interleaving mode and head filling bits, an interleaving operator is determined according to the correction interleaving mode, and the interleaving operator is utilized to perform interleaving processing on subblock interleaving matrices in sequence; one mode can utilize the interleaving operator to perform the interleaving processing on bits required to be output in the subblock interleaving matrices according to the requirement of redundancy version, directly output subblock interleaving results after protocol sorting while completing the interleaving of subblocks until meeting the corresponding requirement of the code rate; and the other mode can utilize the interleaving operator to perform the interleaving processing on the subblock interleaving matrices one by one, output the subblock interleaving results after protocol sorting to a circulating buffer while completing the interleaving of subblocks, and then output corresponding bits after the interleaving according to the requirement of the redundancy version. Furthermore, the invention also discloses a de-interleaving and rate de-matching method corresponding to the interleaving and rate matching method. The methods can greatly reduce buffers to be used and read-write operation of the buffers in the interleaving and rate matching and de-interleaving and rate de-matching processes.

Owner:POTEVIO INFORMATION TECH

Data processing method, knowledge base reasoning method and related device

ActiveCN104915717AIncrease flexibilityExpandable and flexibleInference methodsSpecial data processing applicationsData setTheoretical computer science

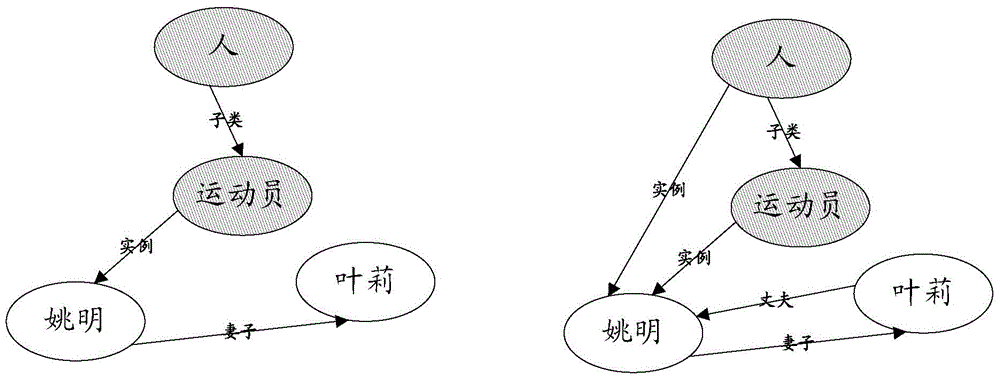

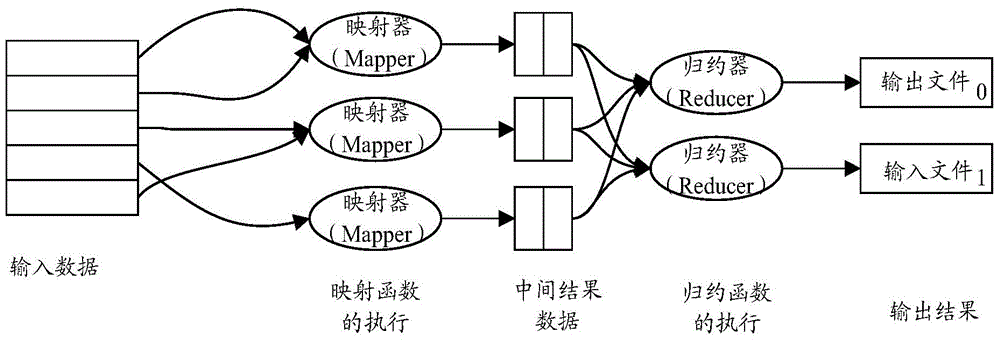

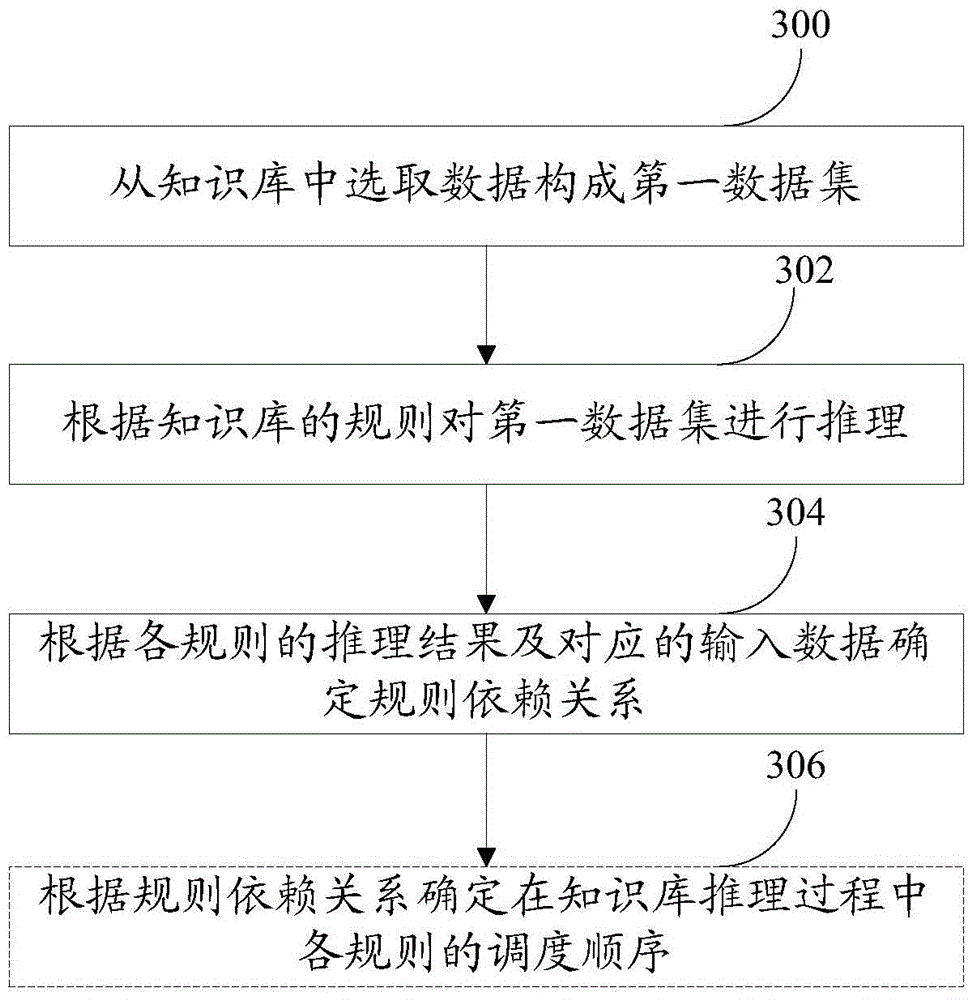

The invention discloses a data processing method, a knowledge base reasoning method and a related device. The data processing method includes the step that the following modes are adopted to determine the rule dependence relationship of the scheduling order of rules in a knowledge base reasoning process: data are selected from a knowledge base so as to form a first data set; the first data set is reasoned according to the rules of the knowledge base; and the rule dependence relationship is determined according to the reasoning results of the rules and corresponding input data. With the data processing method, the knowledge base reasoning method and the related device of the invention adopted, application scenes and flexibility of the reasoning technology of the knowledge base can be improved, and the efficiency of the execution of the rules and overall reasoning performance can be improved.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

How to speed up firefox startup

ActiveCN102289380AReduce I/O read and write operationsReduce read and write operationsProgram loading/initiatingConfiguration optimizationComputer science

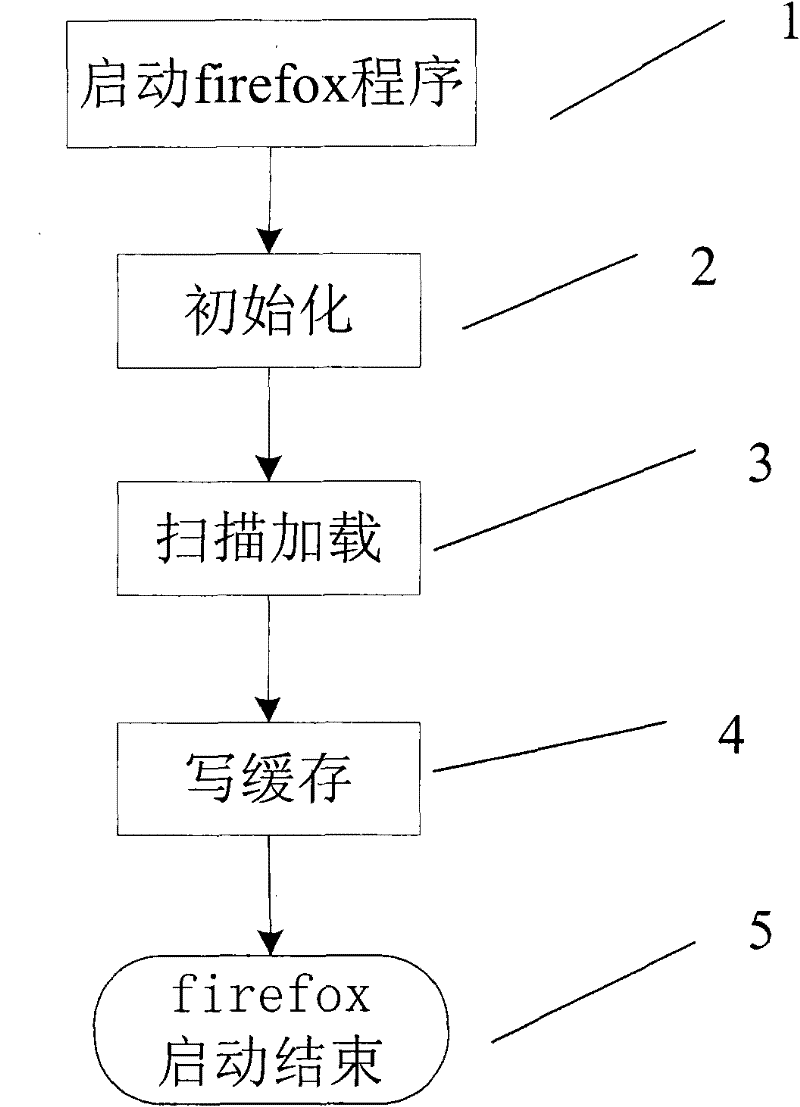

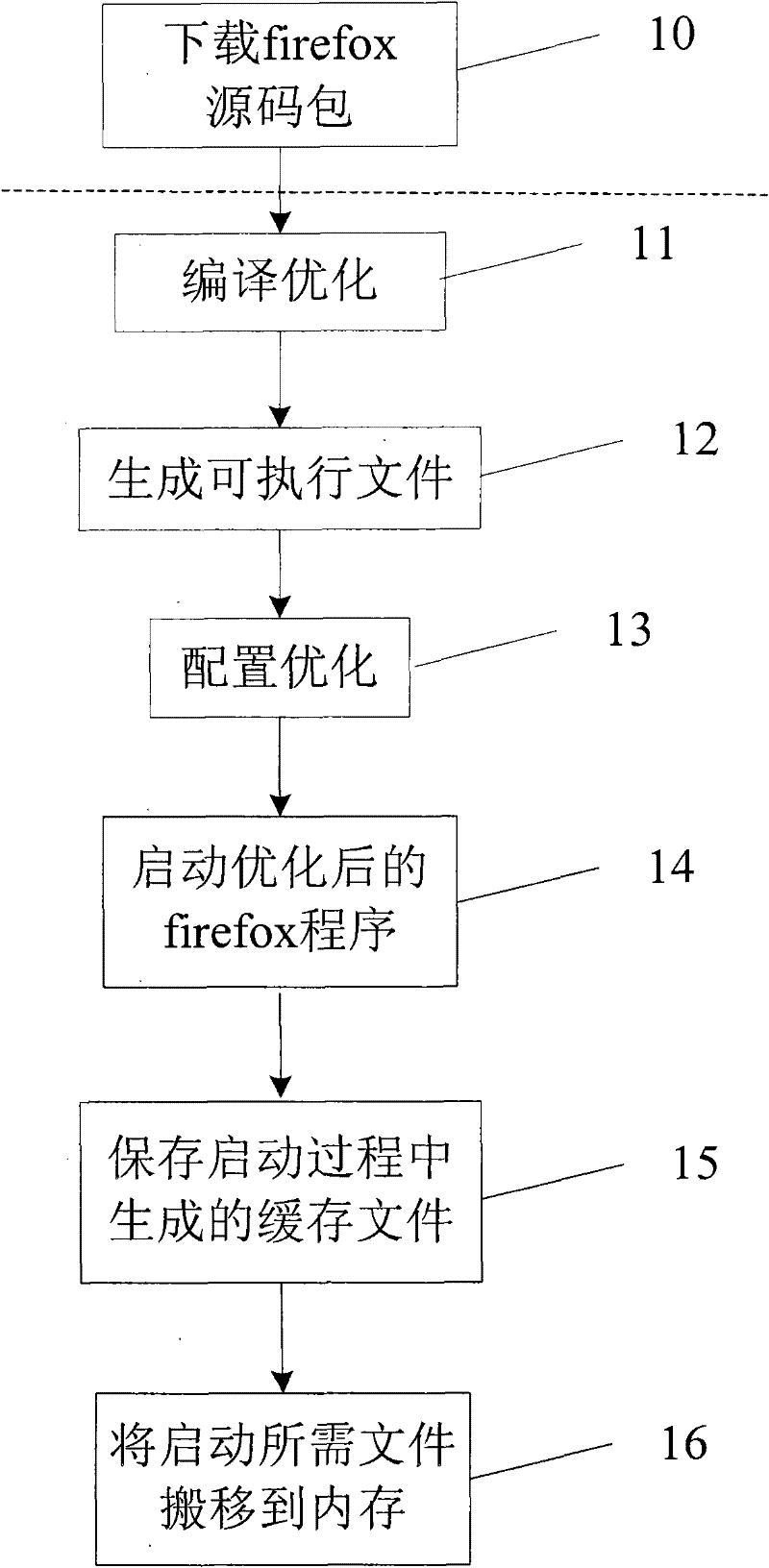

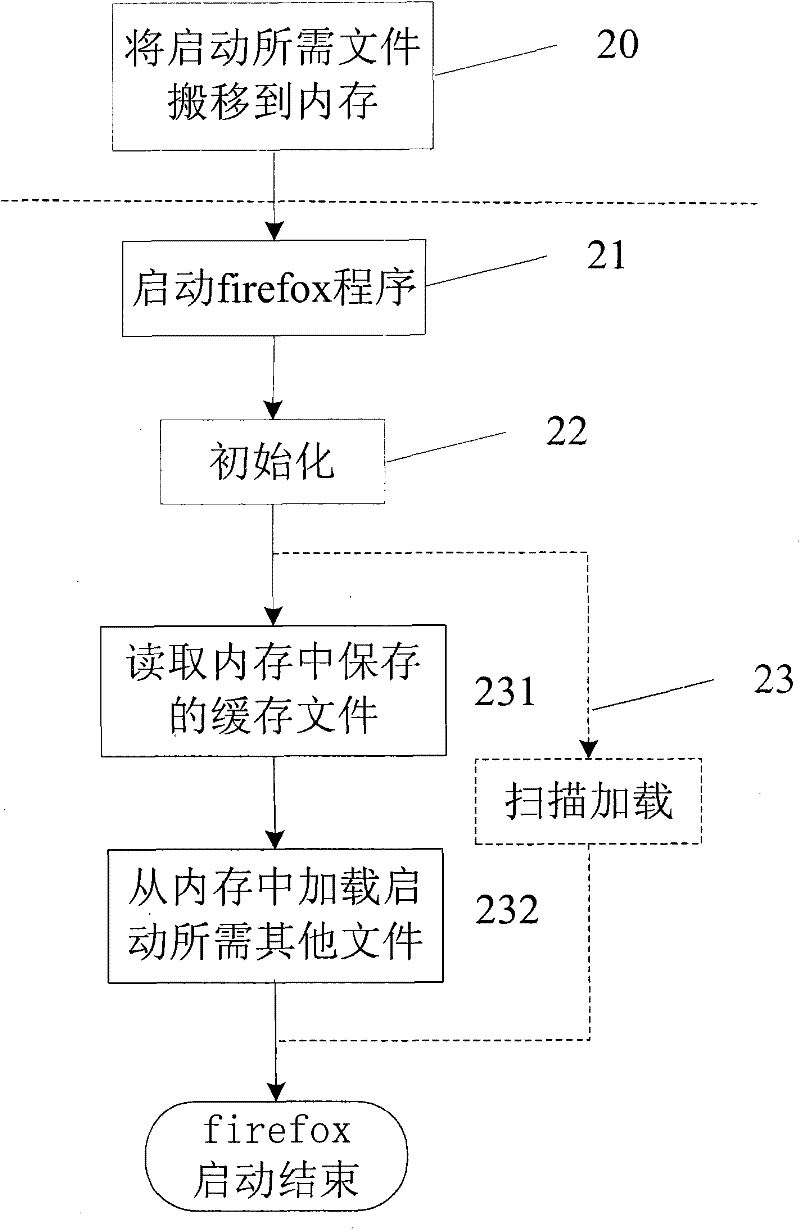

The invention relates to a firefox starting acceleration method. Before a step of starting a firefox program or after the step (21) of starting the firefox program and before a step (22) of initializing, the method comprises a step (20) of moving files, except system files, required by starting into a memory, so that the firefox can be started in the memory. In the firefox starting acceleration method, four aspects, such as compiling optimization, configuration optimization, starting cache file storage and moving of the files required by starting, of the firefox are started in the memory to optimize a starting process of the firefox on a linux platform, so that input / output (I / O) reading and writing operations during starting of the firefox can be reduced greatly, thus the firefox starting speed can be increased effectively.

Owner:CHINA STANDARD SOFTWARE

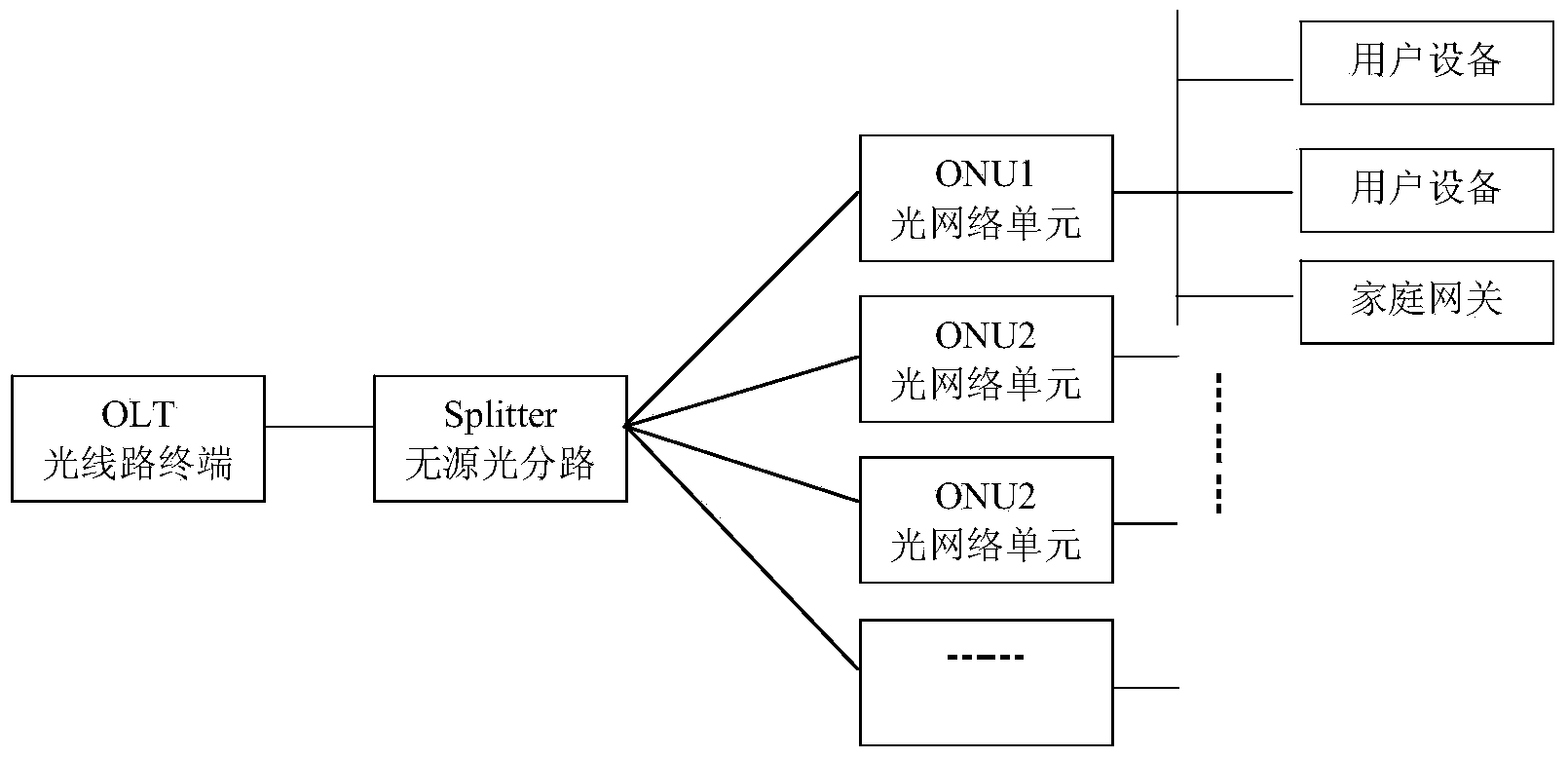

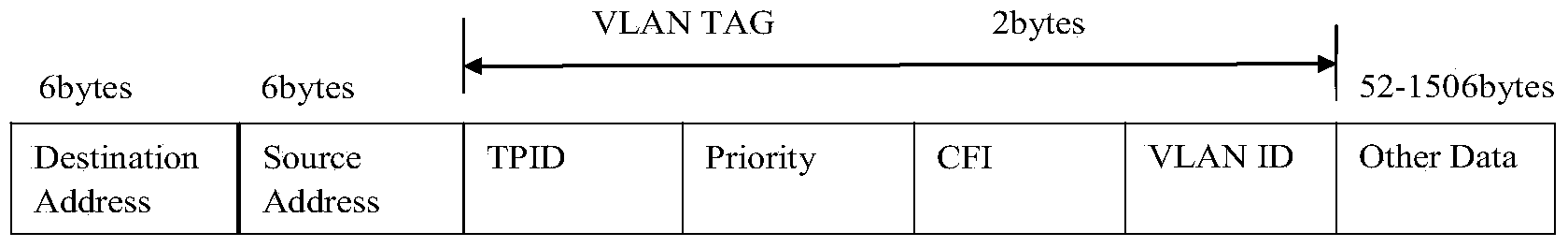

Method and system for achieving user port VLAN service management in ONU

ActiveCN103840996AEfficient implementation of configurationEfficient implementation of deletionNetworks interconnectionNetwork managementService configuration

The invention provides a method and system for achieving user port VLAN service management in an ONU. The method includes the steps that operation is carried out on related service hardware and logic according to VLAN service configuration data attribute tables, and the VLAN service configuration data attribute tables are saved in a first memory space of the ONU; a new table is formed according to VLAN service configuration data issued by a gateway and saved in a second memory space of the ONU; the related service hardware and logic and the VLAN service configuration data attribute tables in the first memory space are updated according to comparison results between table data in the first memory space and table data in the second memory space so as to bring service configuration into effect. By comparing new configuration and original configuration first according to the configuration data issued by network management software and then determining a next action according to marked content, user port VLAN service configuration and deletion can be efficiently achieved, VLAN service configuration states can be tracked comprehensively, specific requirements for hardware forms are avoided, and the method can be simplified and is short in implementation cycle.

Owner:FENGHUO COMM SCI & TECH CO LTD

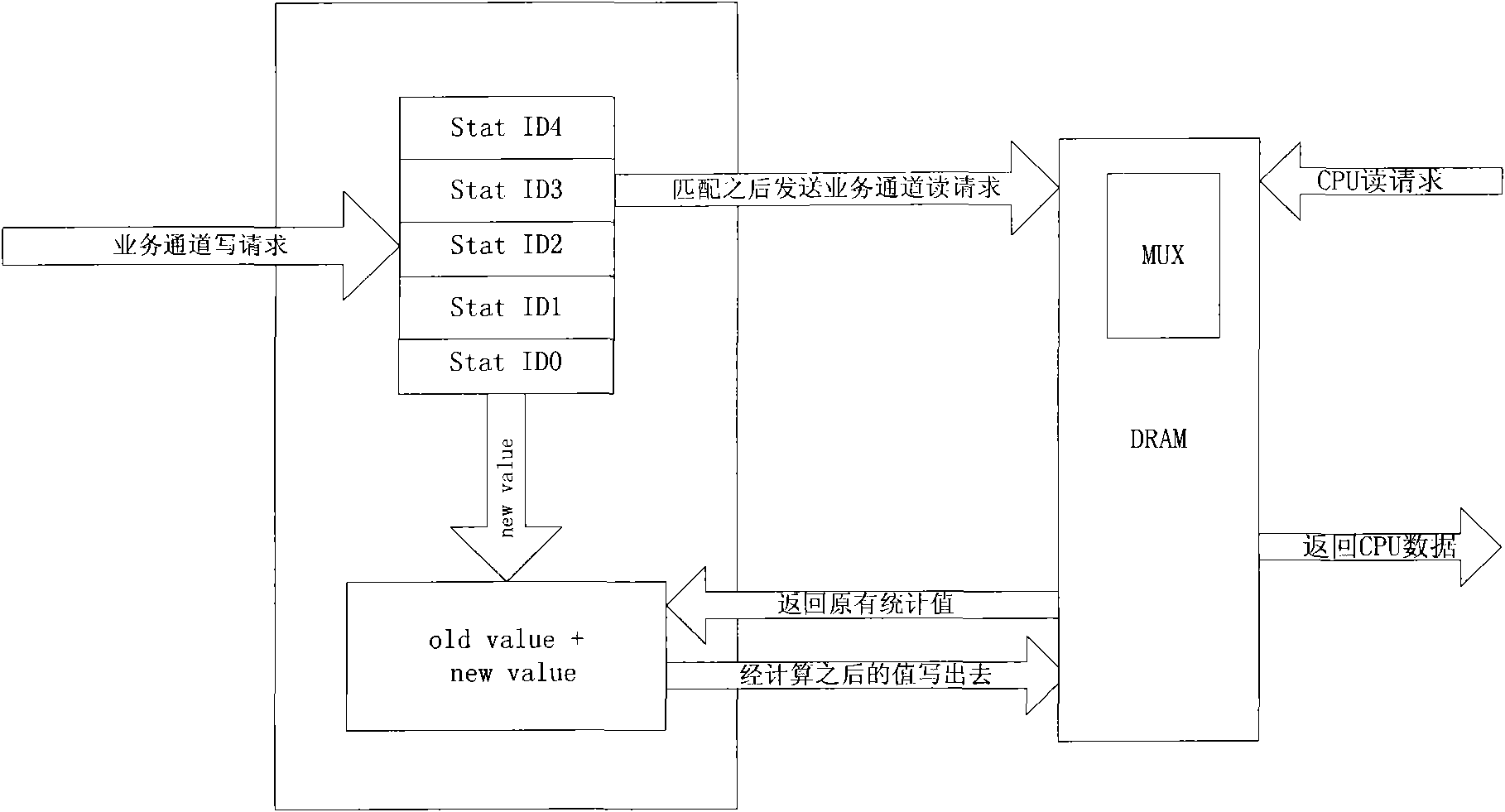

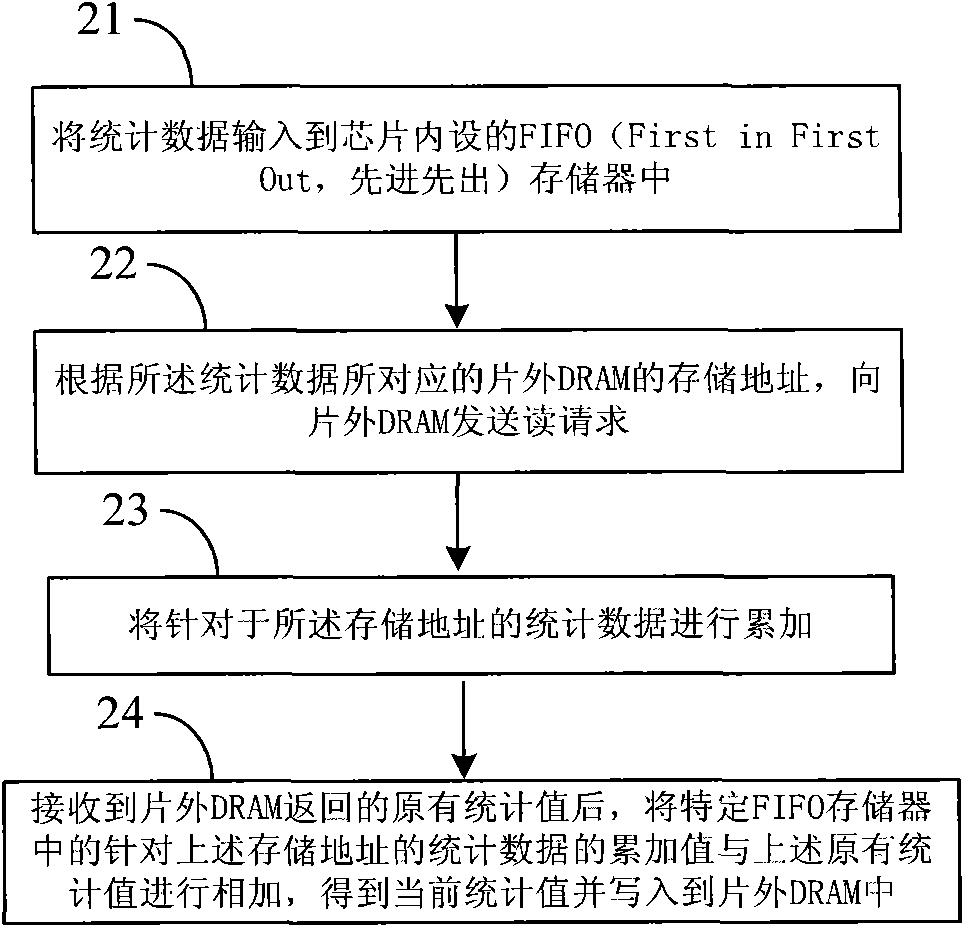

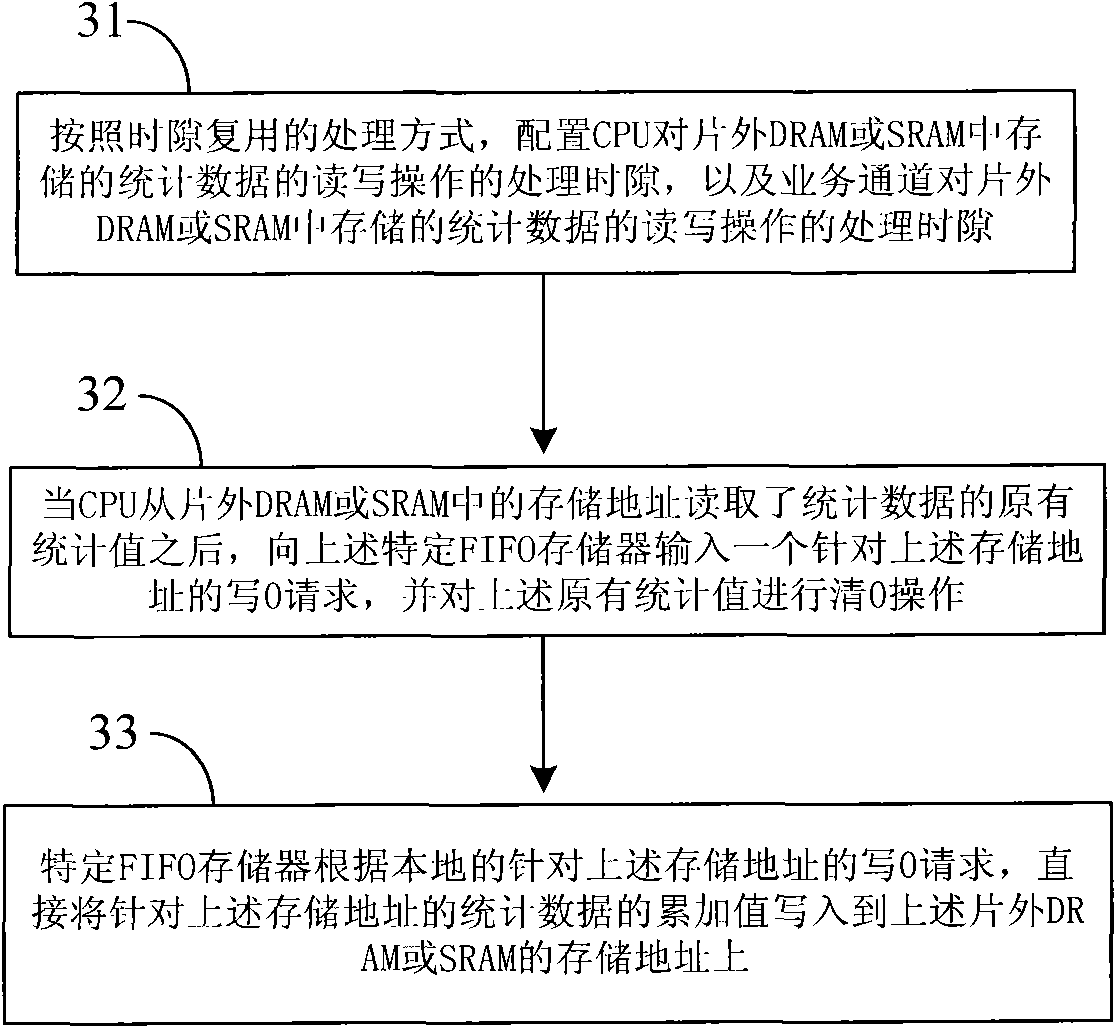

Management method and management device for statistical data of chip

InactiveCN101848135AEasy to handleReduce read and write operationsMemory adressing/allocation/relocationData switching networksMemory addressComputer science

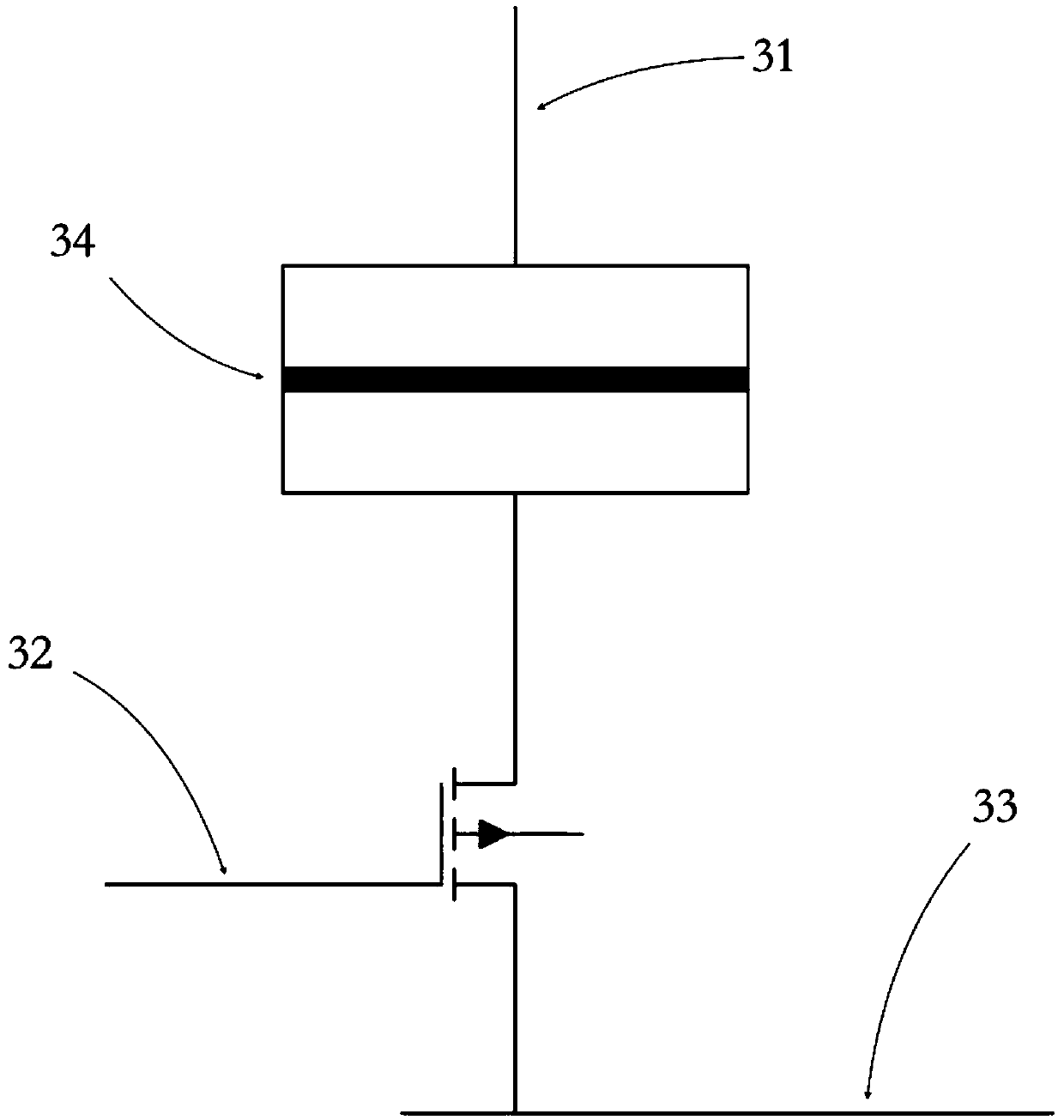

The embodiment of the invention provides a management method and a management device for statistical data of a chip. The method mainly comprises the following steps: accumulating statistical data corresponding to the same memory address in an off-chip memory device to obtain an accumulated value, obtaining an original statistical value at the same memory address in the off-chip memory device, adding the accumulated valve to the original statistical value to obtain a current statistical value, and writing the current statistical value into the same memory address in the off-chip memory device. By adopting the invention, a plurality of statistical data at the same memory address can be written into an off-chip memory through one writing operation. Thereby, the reading and writing operations of the off-chip memory are effectively buffered, the conflict with the access to a bank in the off-chip memory is effectively reduced, and the processing capacity of the chip to the statistical data is greatly improved.

Owner:HUAWEI TECH CO LTD

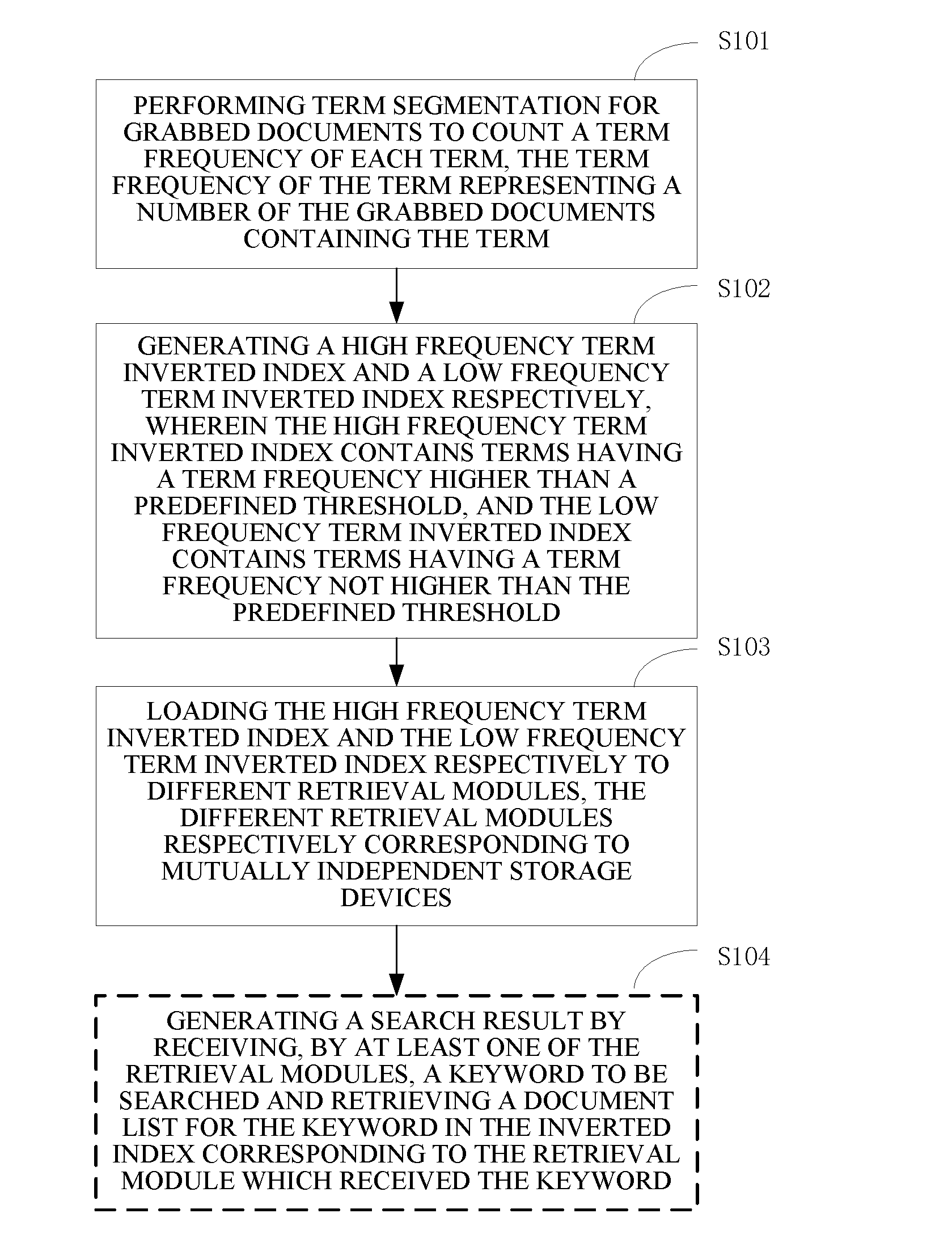

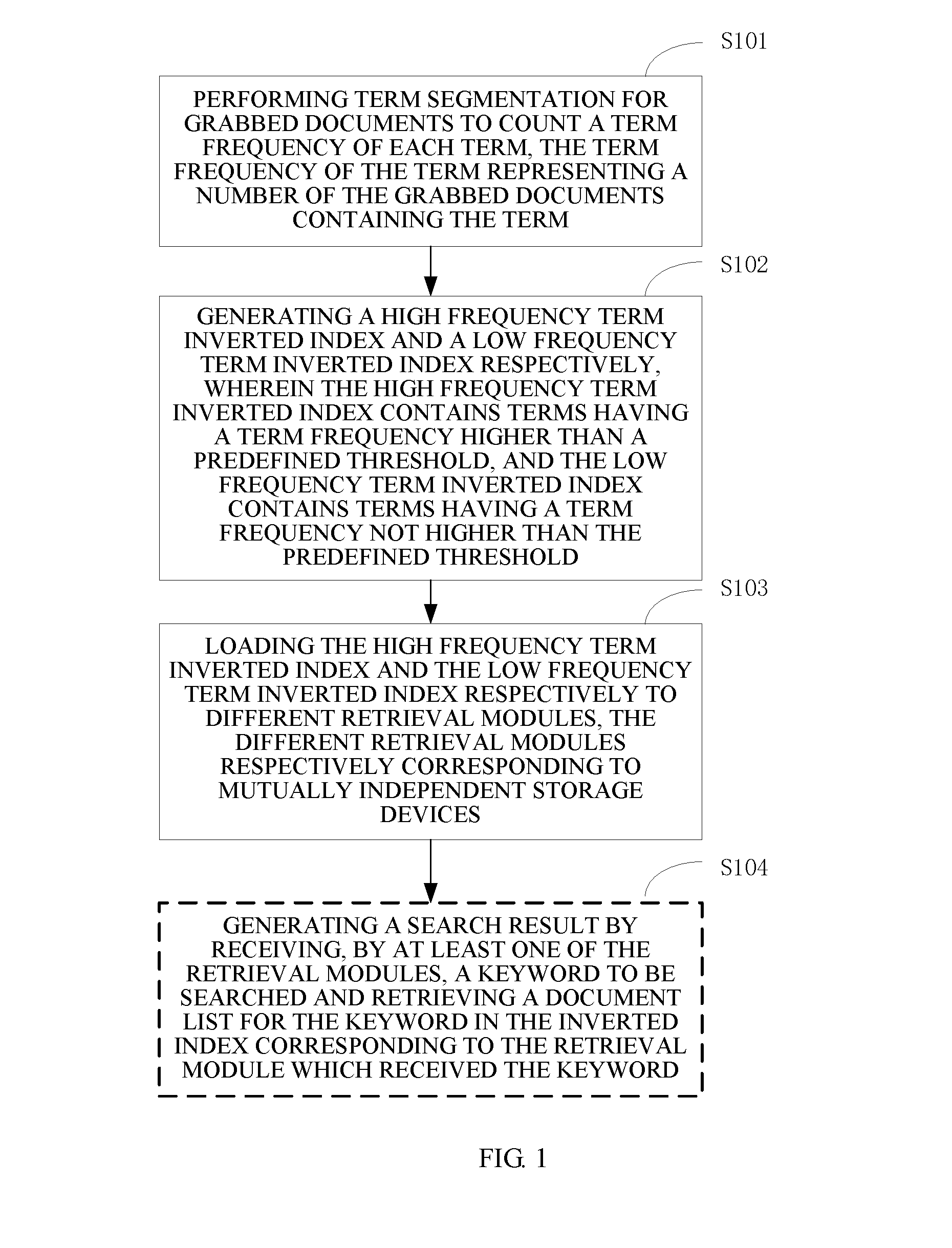

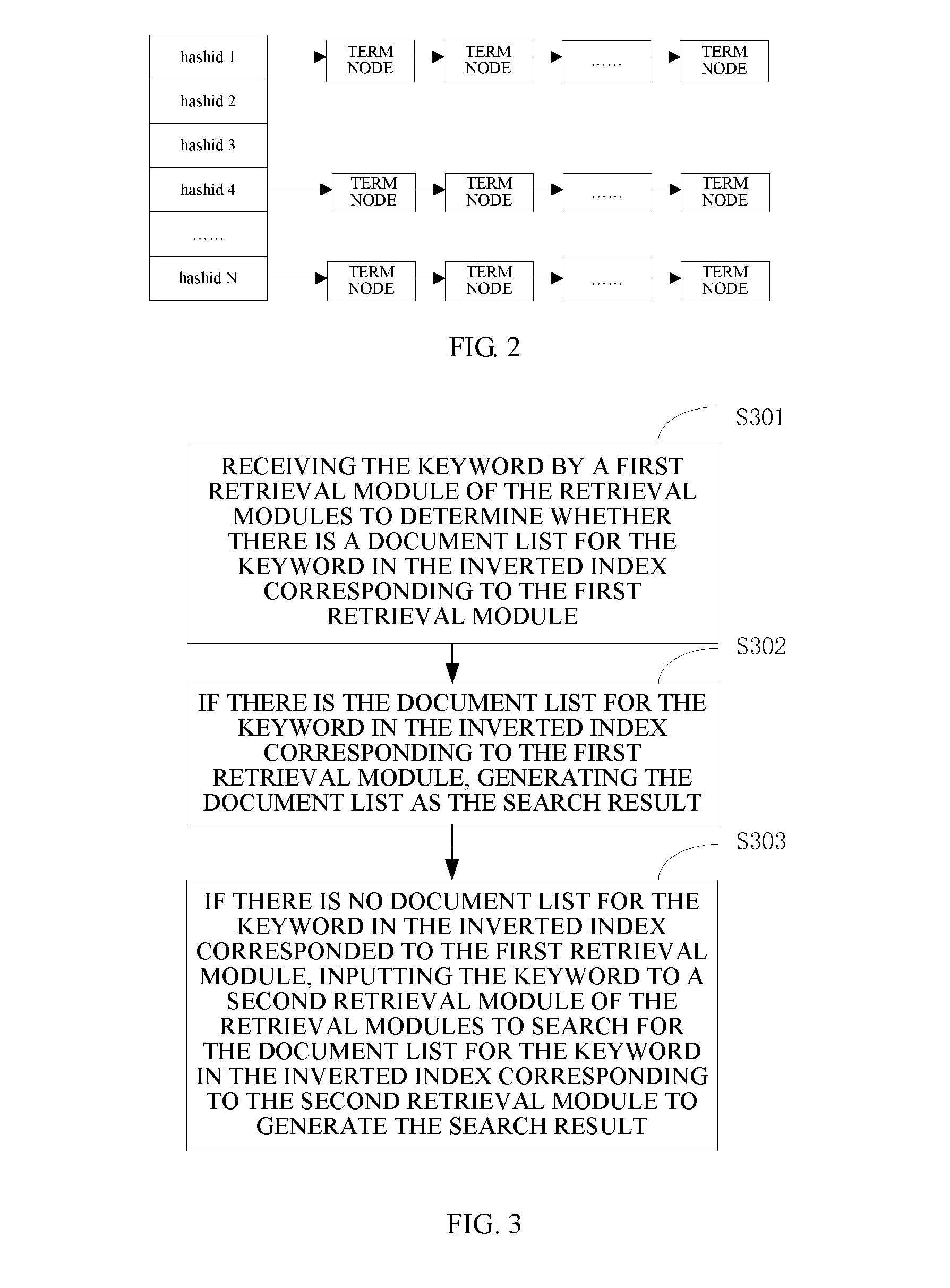

Method and apparatus for search

ActiveUS20160275178A1Memory occupancyReduce readWeb data indexingSpecial data processing applicationsReverse indexLow frequency

Methods and apparatuses for search are provided and related to the field of search technology. A method may include: performing term segmentation for grabbed documents to count a term frequency of each term, the term frequency of the term representing a number of the grabbed documents containing the term; generating a high frequency term inverted index and a low frequency term inverted index respectively, wherein the high frequency term inverted index contains terms having a term frequency higher than a predefined threshold, and the low frequency term inverted index contains terms having a term frequency not higher than the predefined threshold; and loading the high frequency term inverted index and the low frequency term inverted index respectively to different retrieval modules, the different retrieval modules respectively corresponding to mutually independent storage devices.

Owner:TENCENT TECH (SHENZHEN) CO LTD

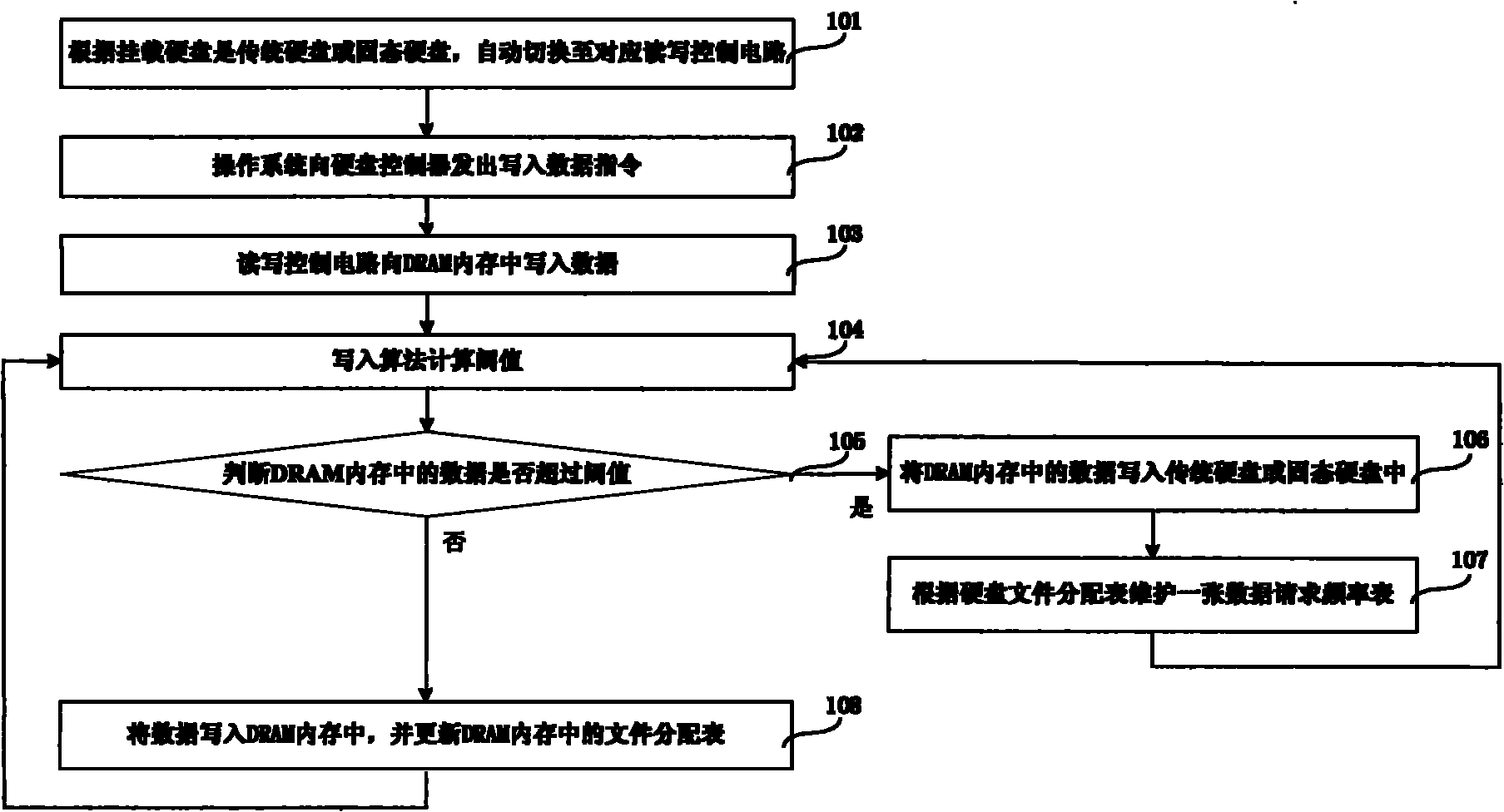

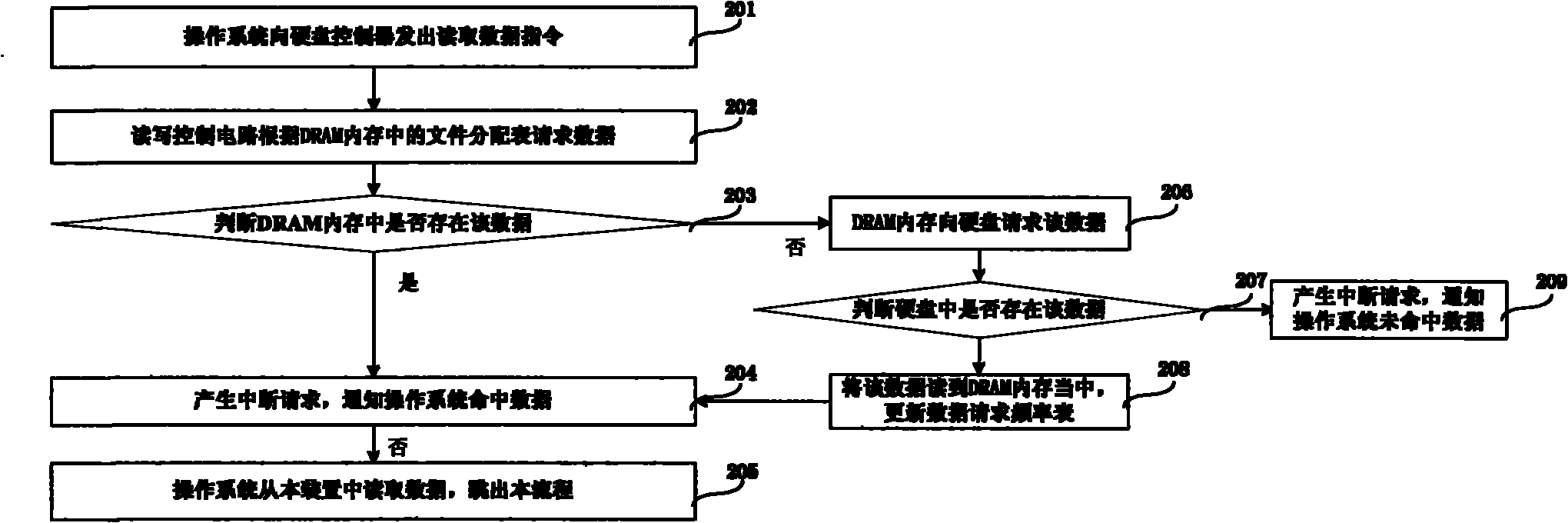

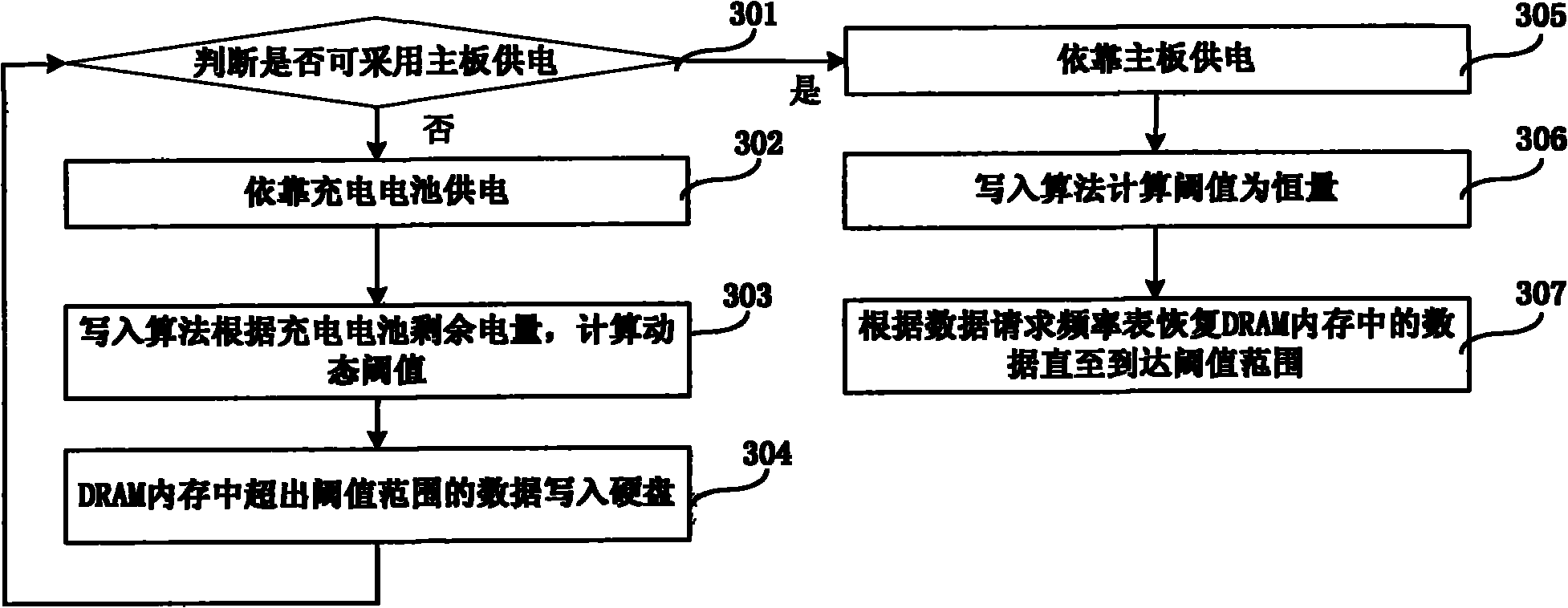

Hard disk storage method and device integrated with battery and DRAM

InactiveCN102110034AImprove read and write speedReduce read and write operationsMemory loss protectionRedundant hardware error correctionDram memorySolid-state drive

The invention discloses hard disk storage equipment integrated with a battery and a DRAM. The method comprises steps as follows: the DRAM (dynamic random access memory) is integrated with a traditional hard disc or a solid hard disc, a rechargeable battery is used for supplying battery, the traditional hard disc or the solid hard disc is adopted as a back-up permanent storage device, and the DRAM is ordinarily adopted as a main storage component. When the power is cut off or the data size stored in the DRAM exceeds a pre-set threshold value, the data in the DRAM is written in the traditional hard disc or the solid hard disc. Compare with the prior art, the hard disk storage equipment has the advantages that data writing and reading speed is quick, the hard disc service life is prolonged, and data loss and physical damage caused by unexpected power failure can be avoided. The invention discloses a hard disc storage device integrated with battery and DRAM.

Owner:BEIJING SAFE CODE TECH

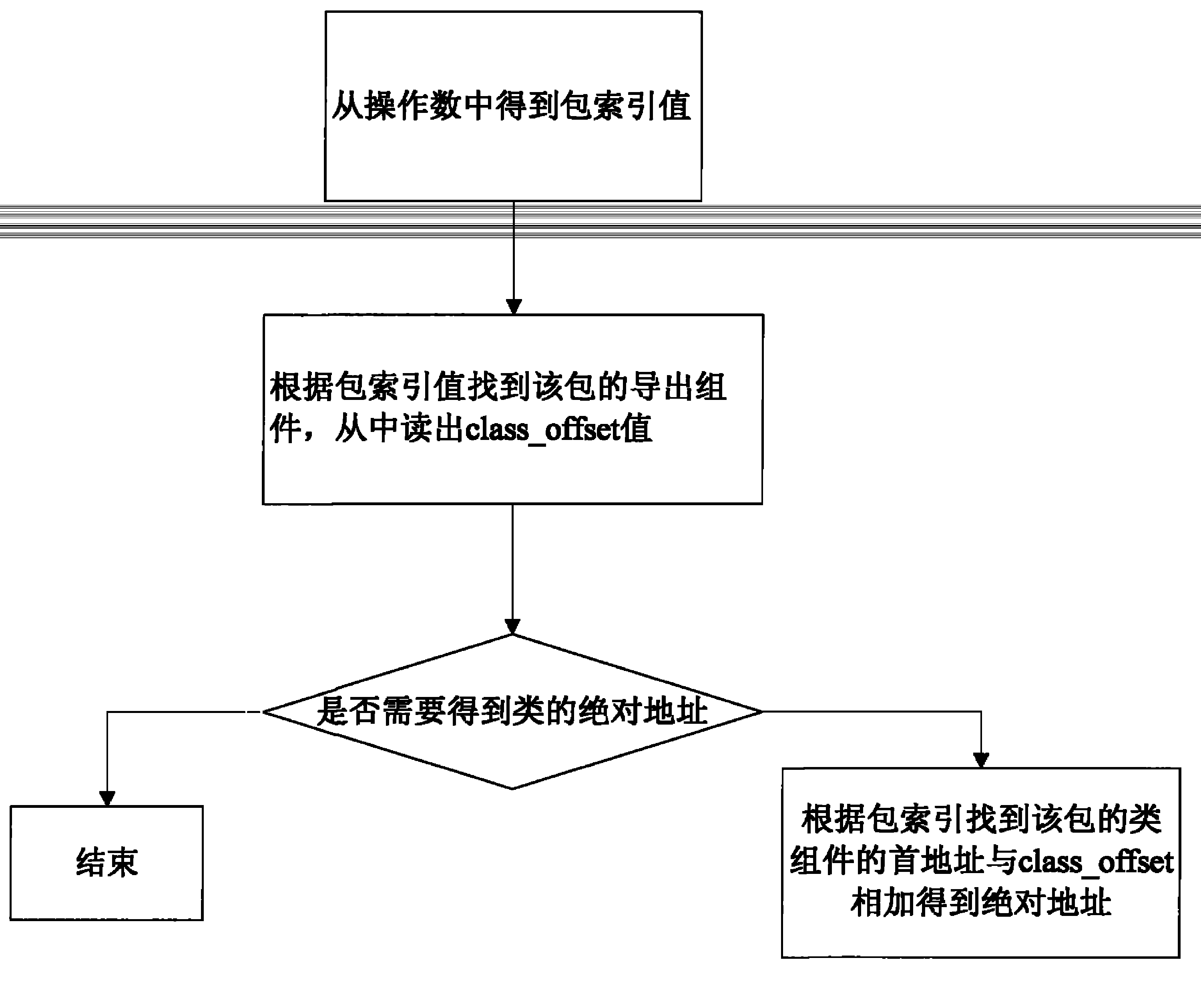

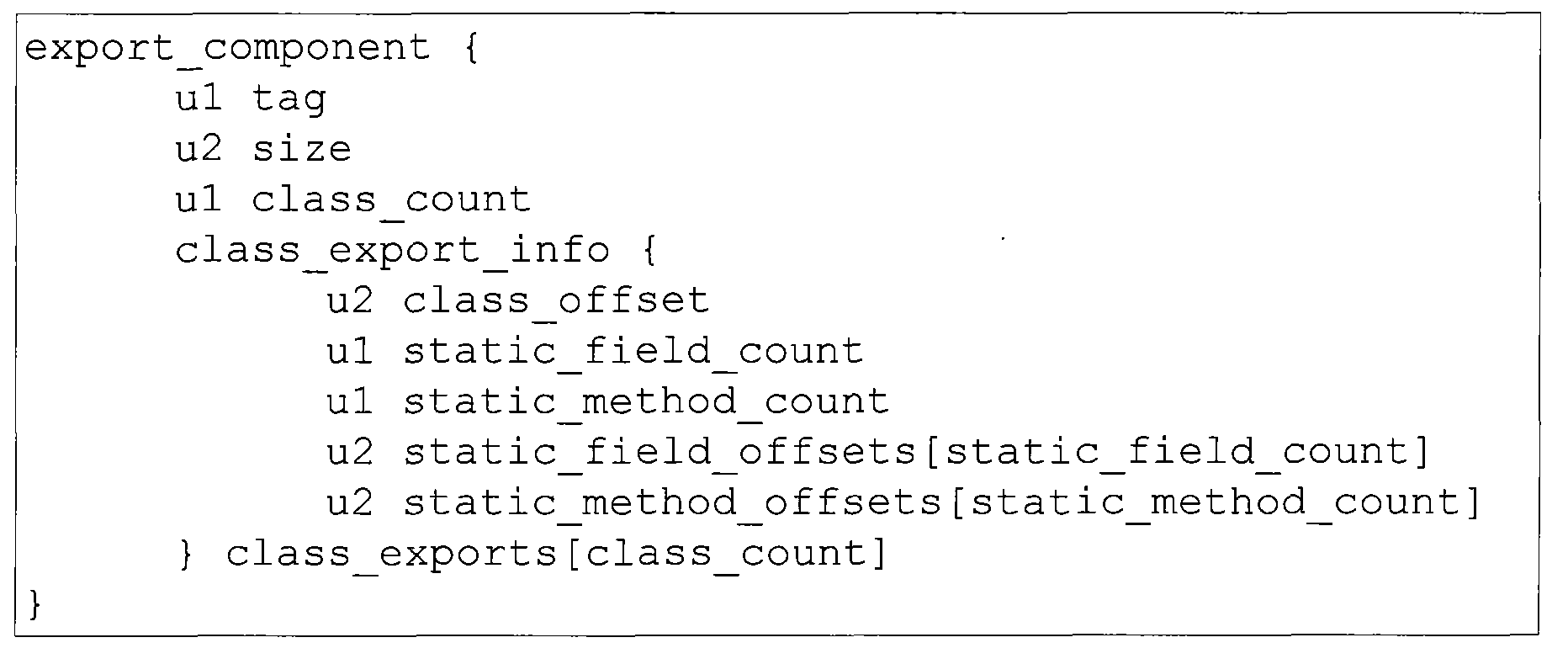

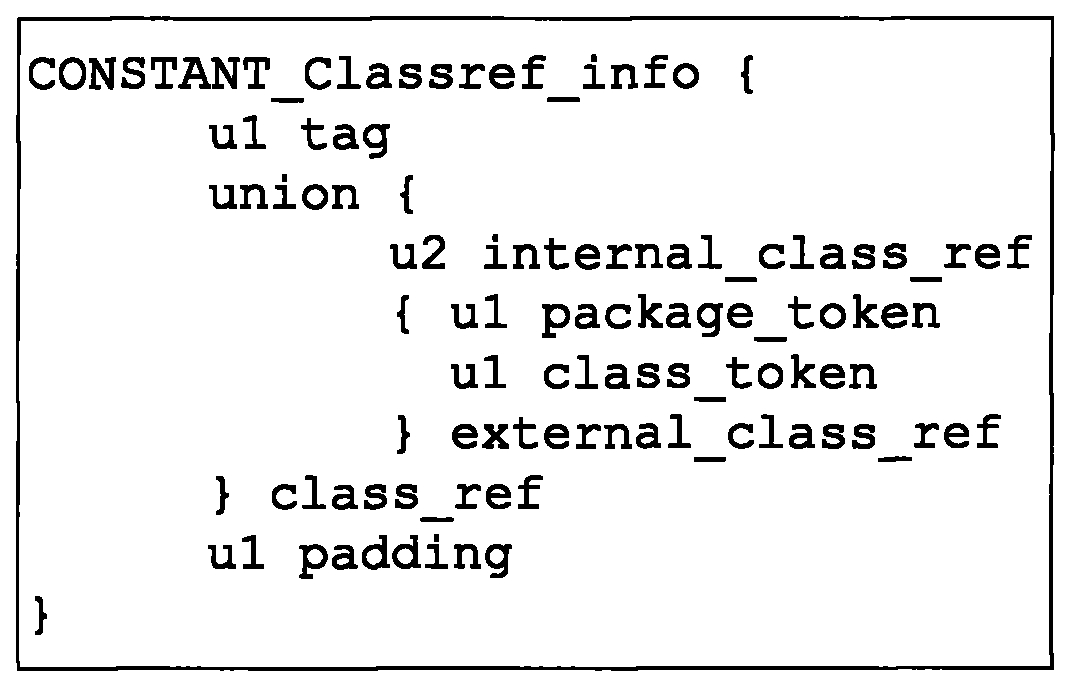

Method for analyzing Classref constant of CAP file

ActiveCN103677778AReduce read and write operationsShorten the timeSpecific program execution arrangementsOperandComputer science

The invention discloses a method for analyzing a CONSTANT_Classref constant of a CAP file pool assembly. The method includes retaining an original value of the class_offset in the class_export_info of a leading out assembly of a JCRE system package and a downloading package; if the CONSTANT_Classref constant in the constant pool assembly is of a category other than the package, finding a package index of the package through a package_token item, storing the package index to replace the package_token item, enabling the highest position of the package index to be 1, retaining the value of the class_token item, replacing a constant pool index in a byte code operand with the value of the analyzed constant during reference position assembly analysis, finding a leading out assembly of the package through the package index during virtual machine explanation execution, directly reading the value of the class_offset from the corresponding class_export_info according to the class_token, and meanwhile finding a similar assembly head address of the package can be found through the package index. The absolute address of the category can be obtained through calculation according to the obtained deviation value.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

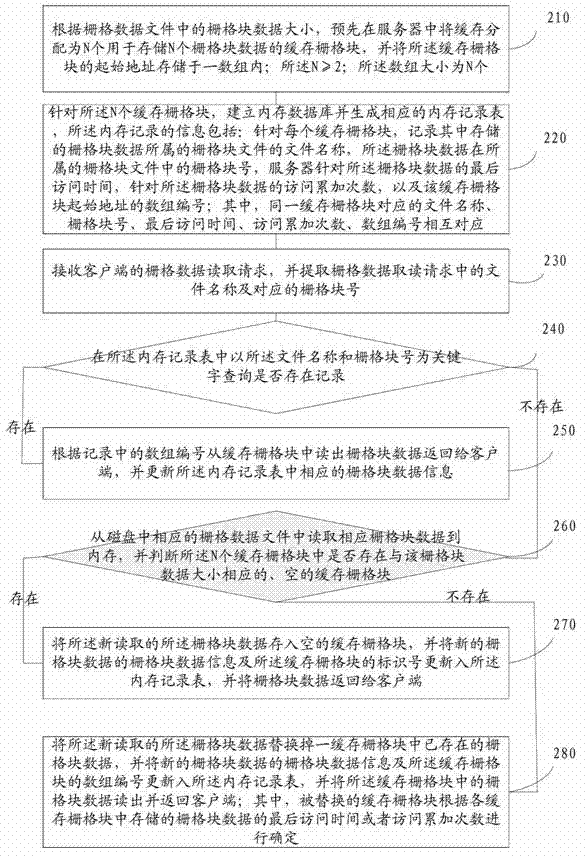

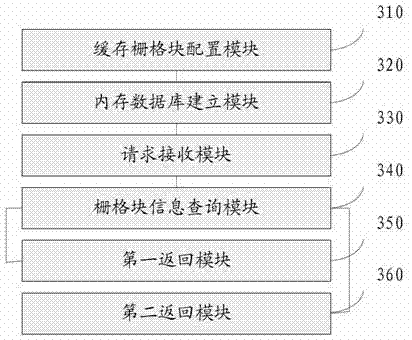

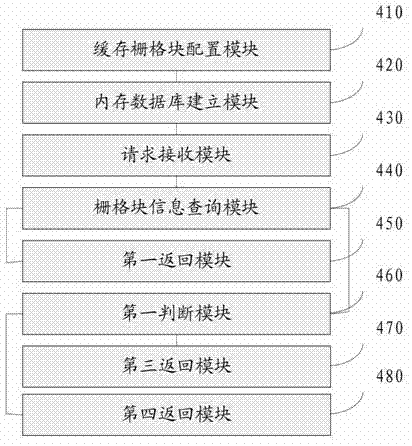

Method and device for reading and processing raster data

ActiveCN102968456AImprove data processing efficiencySave system resourcesSpecial data processing applicationsRaster dataData library

The invention provides a method and device for reading and processing raster data, and relates to the technical field of space information services. The method comprises the following steps of separating a buffer into N buffer raster blocks in a server in advance, wherein the N buffer raster blocks are used for storing data of the N raster blocks; according toiming at the N buffer raster blocks, building a memory database, and generating a corresponding memory recording table, wherein the memory recording table is used for recording the use information of each buffer raster block; then, receiving a request for reading raster data from a client; and inquiring the memory recording table to judge whether the requested raster block data exist or not, wherein, if the requested raster block data exist, reading the raster block data are read from the buffer raster blocks and returneding the raster block data to the client, and if the requested raster block data do not exist, extracting the corresponding raster block data are extracted from a disc, and are storeding the corresponding raster block data into an empty buffer raster block or are alternatively selecteding to enter one buffer raster block, updating the records in the memory are updated, and returning the raster block data are returned to the client. The method and the device have the advantages that the processing efficiency of the raster data is improved, and the system resource is saved.

Owner:BEIJING DATUM TECH DEV

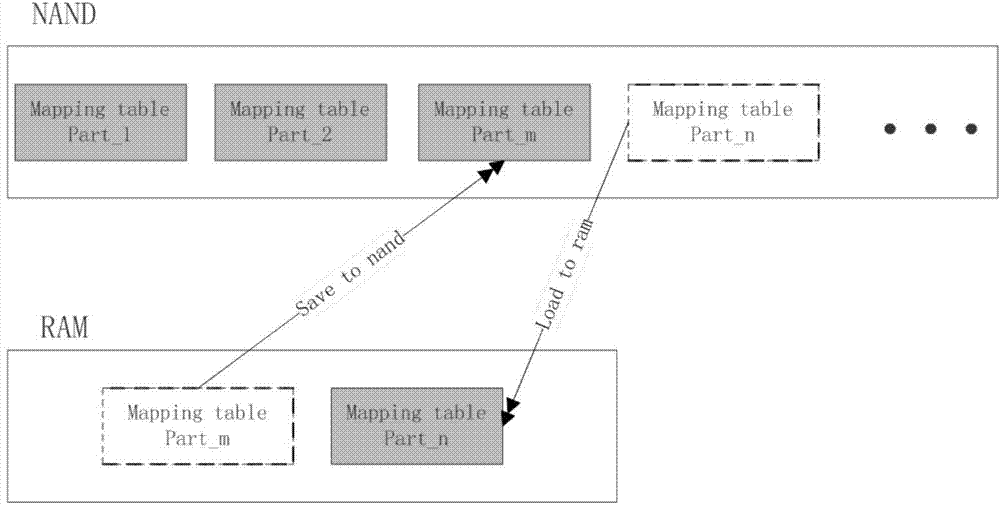

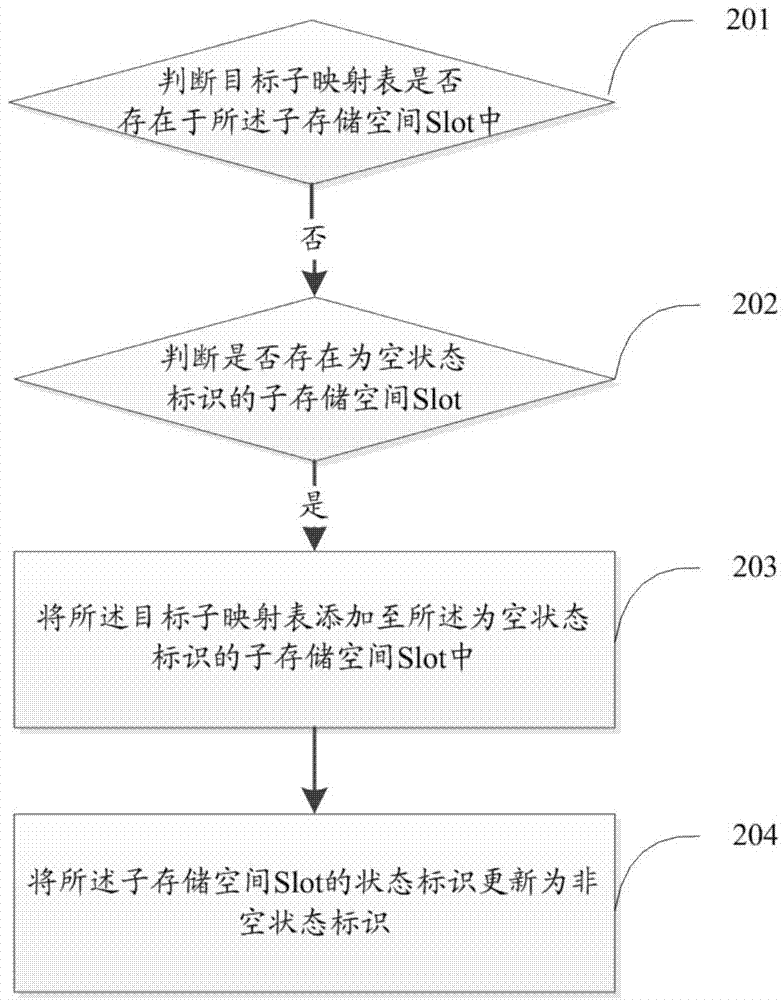

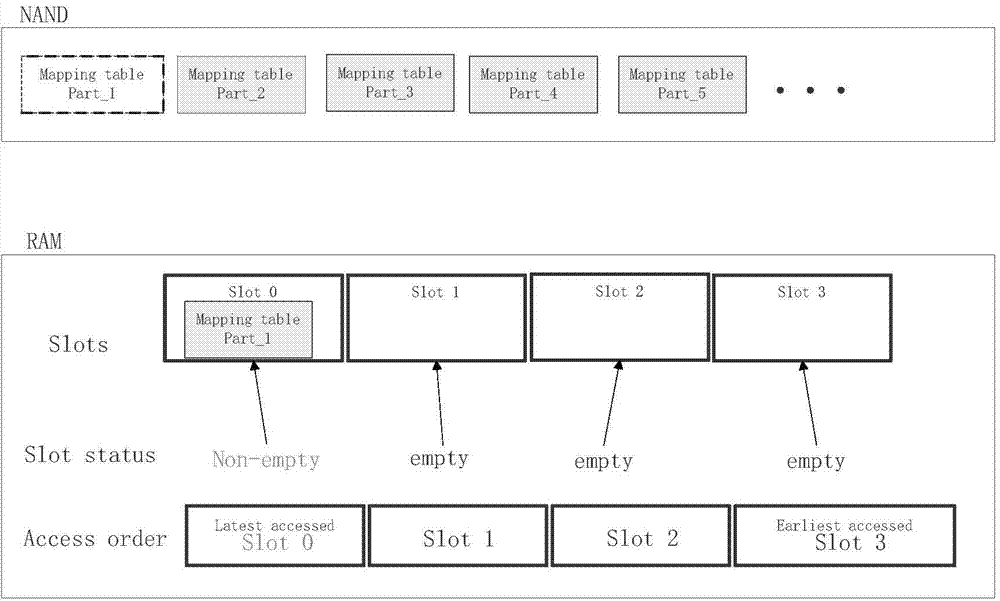

Method and device for processing mapping tables in memory

ActiveCN104281535AReduce conversionReduce read and write operationsMemory adressing/allocation/relocationData mining

The invention discloses a method and a device for processing mapping tables in the memory. The method includes steps of judging whether target mapping sub-tables exist in memory sub-spaces Slot or not; if no target mapping sub-stables exist in the memory sub-spaces Slot, judging whether the memory sub-spaces Slot with empty state identifiers exist or not, and if yes, adding the target mapping sub-tables to the memory sub-spaces Slot with the empty state identifiers; updating the state identifiers of the memory sub-spaces Slot into non-empty state identifiers. By the method and the device for processing the mapping tables in the memory, conversion times of the mapping tables in the memory and read-write operation of data are reduced, and read-write delay is shortened.

Owner:GIGADEVICE SEMICON (BEIJING) INC

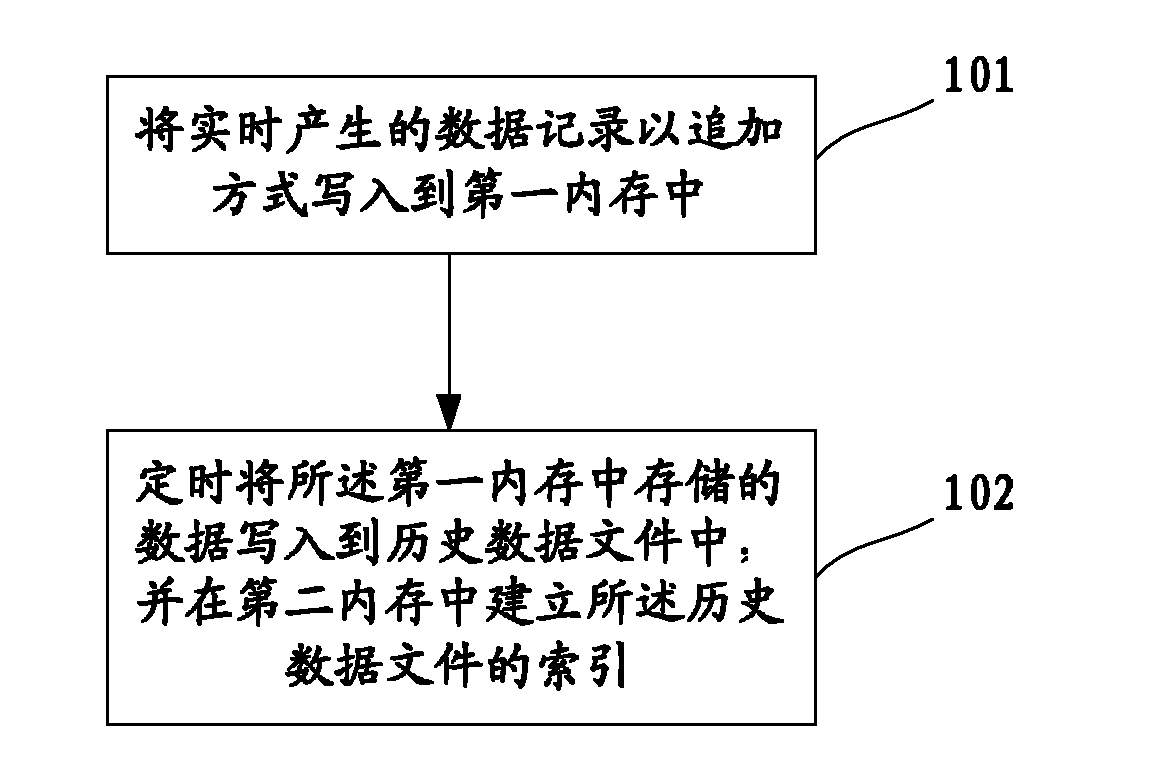

Real-time massive data index construction method and system

InactiveCN102207964AReduce read and write operationsReduce consumptionSpecial data processing applicationsData fileData recording

The invention relates to a data processing technology and discloses a real-time massive data index construction method and system. The method comprises the following steps: writing data records generated in real time into a first memory in an appending manner; and writing the data stored in the first memory into a historical data file periodically, and constructing an index of the historical datafile in a second memory. The method and system provided by the invention can be used for rapidly constructing the index with high efficiency so as to meet the requirement of quick query.

Owner:TELEFON AB LM ERICSSON (PUBL)

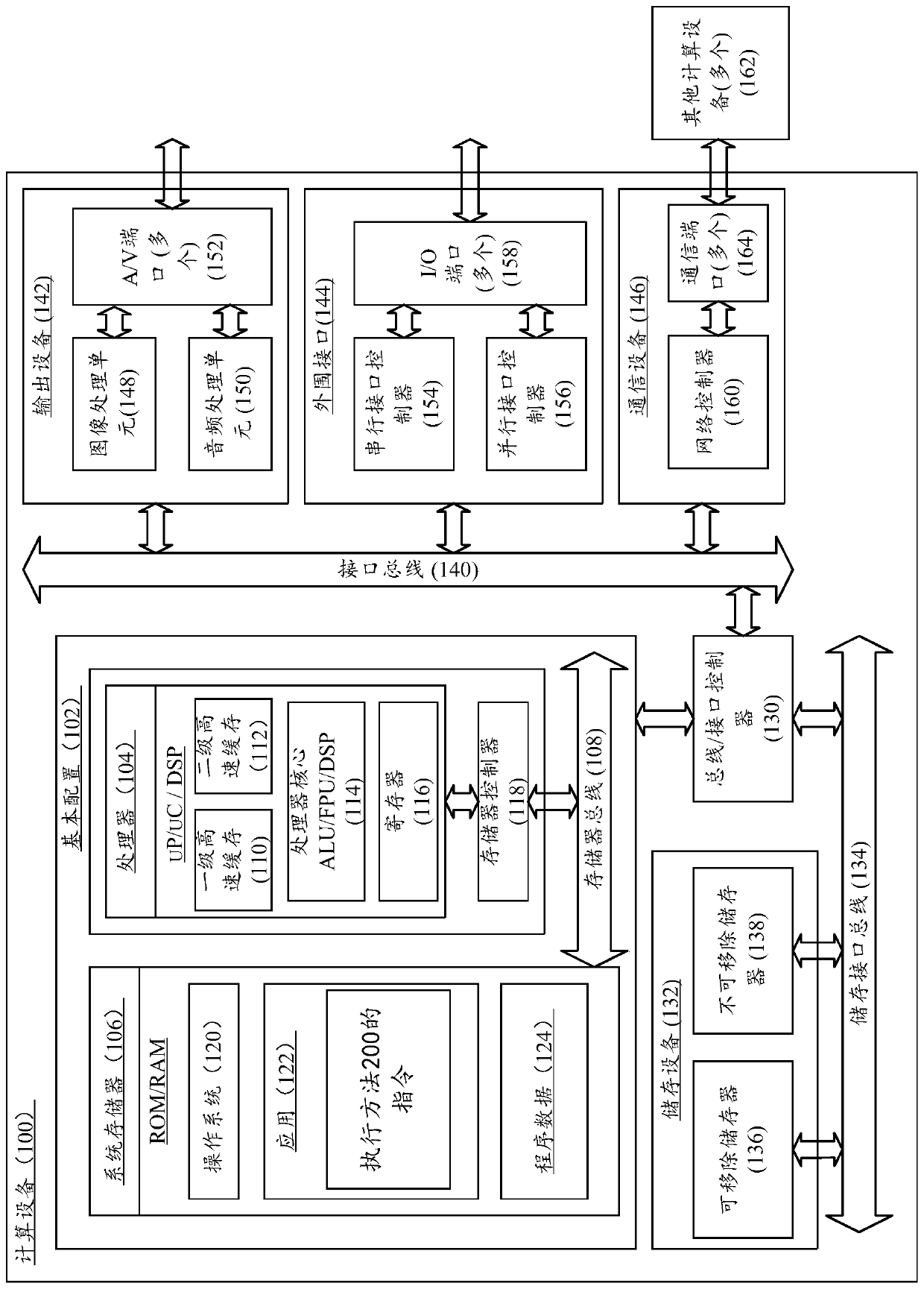

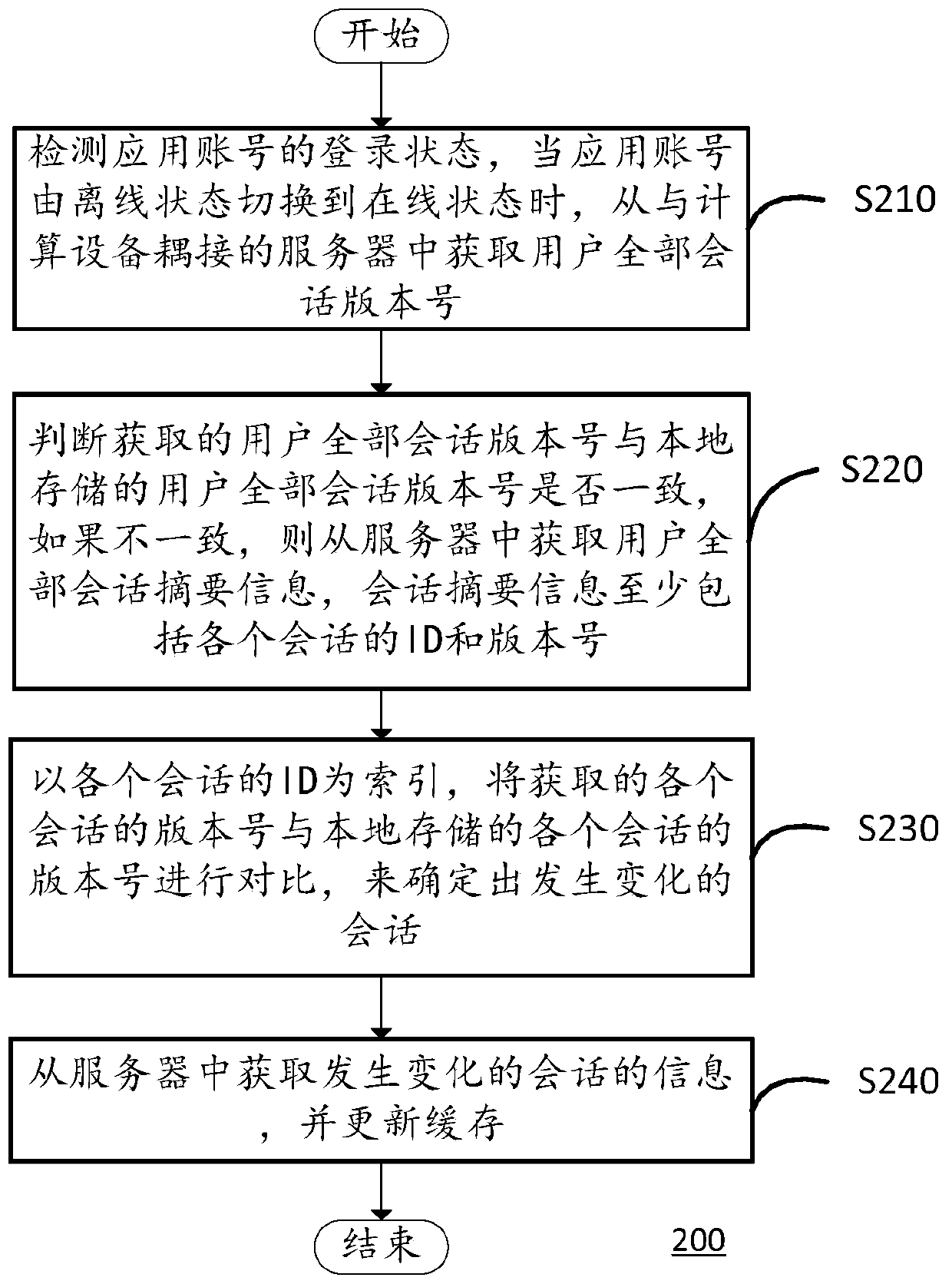

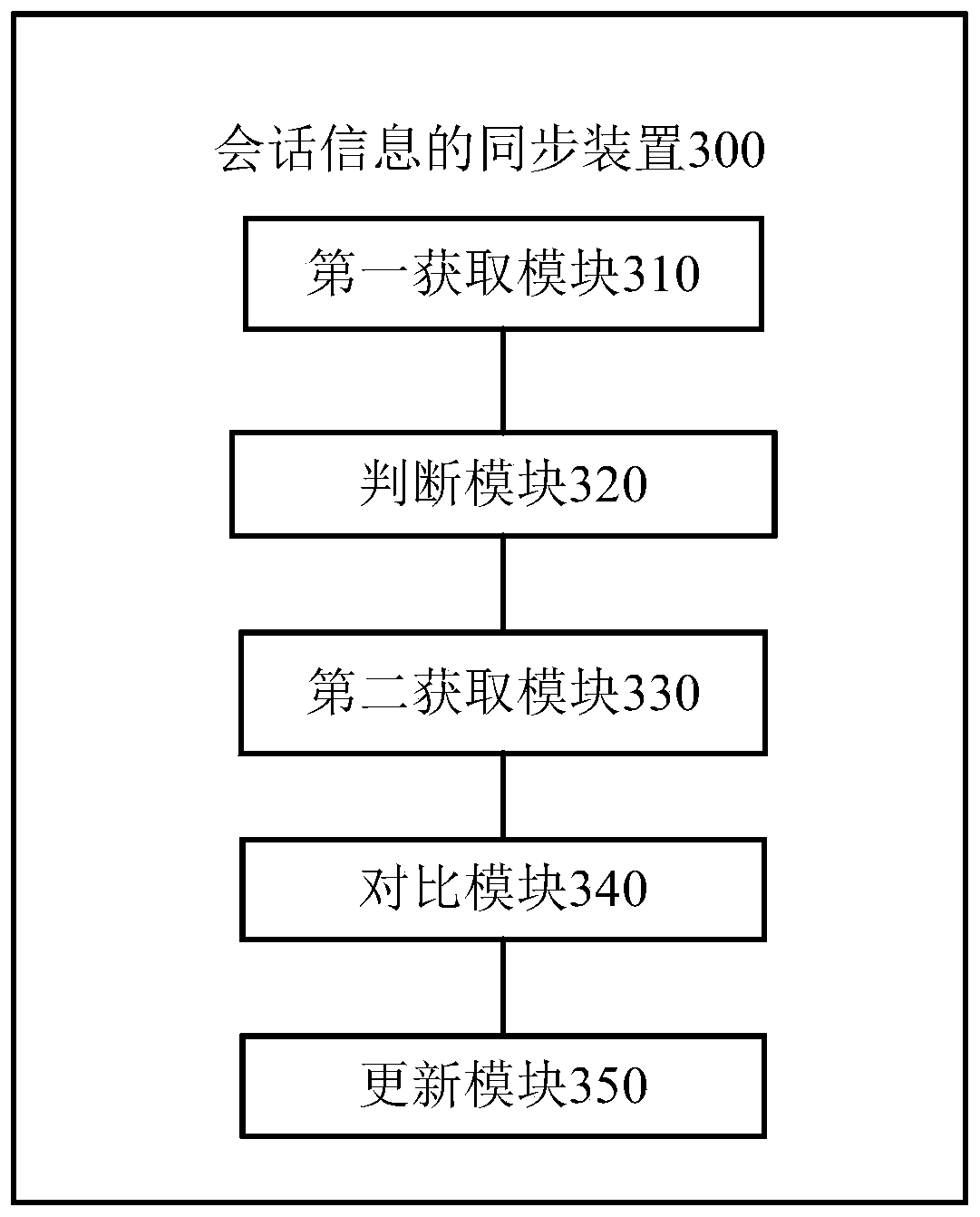

Session information synchronization method, device, computing equipment and storage medium

ActiveCN110493122AIntegrity guaranteedReduce consumptionData switching networksOperating systemInstant messaging

The invention discloses a session information synchronization method. The method is suitable for being executed in the computing equipment. An application used for instant messaging resides in the computing equipment. The method comprises the steps of detecting the login state of an application account; when the application account is switched from an offline state to an online state, obtaining all session version numbers of a user from a server coupled with the computing equipment; judging whether the obtained user all session version numbers are consistent with locally stored user all session version numbers or not; if not, obtaining user all session summary information from a server, wherein the session summary information at least comprises the ID and version number of each session; taking the ID of each session as an index, and comparing the obtained version number of each session with a locally stored version number of each session to determine a changed session; obtaining the information of the changed session from the server, and updating the cache.

Owner:北京拉勾网络技术有限公司

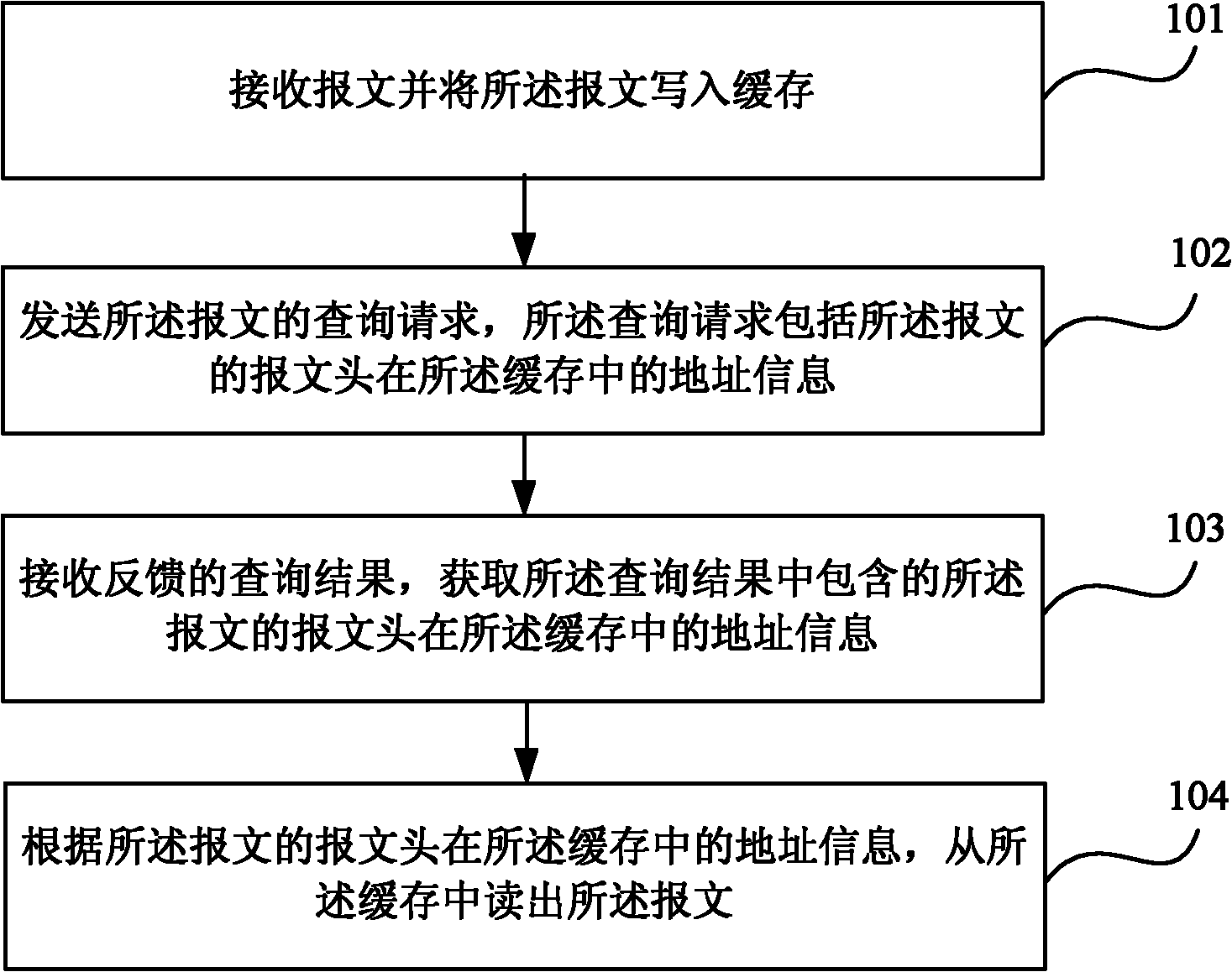

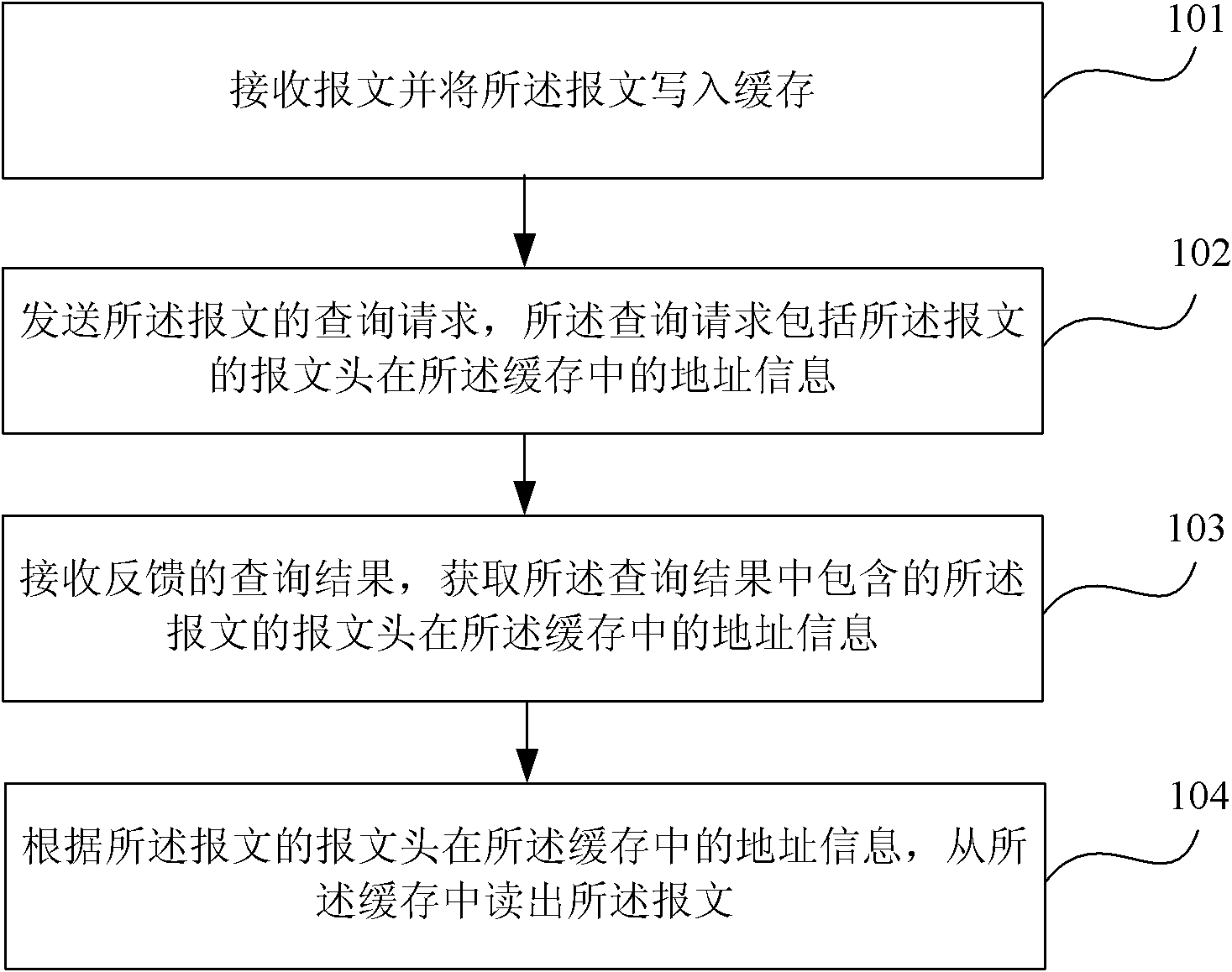

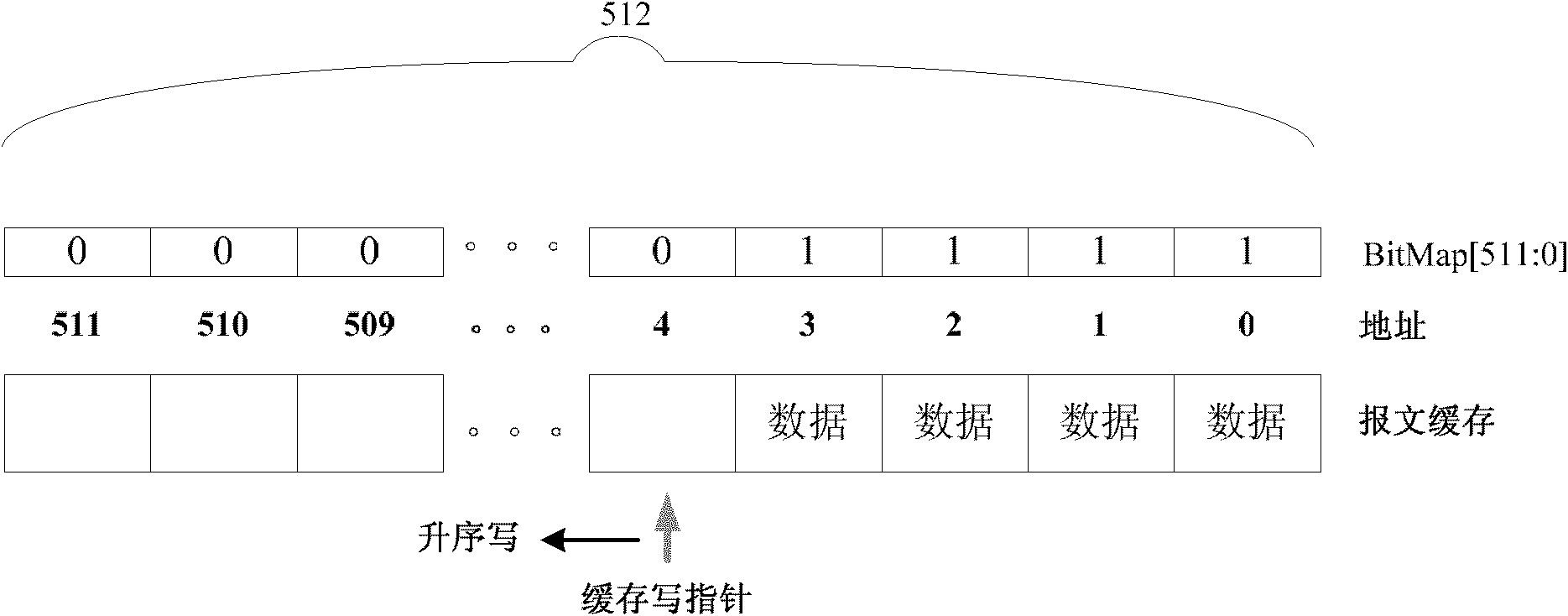

Message query method and device

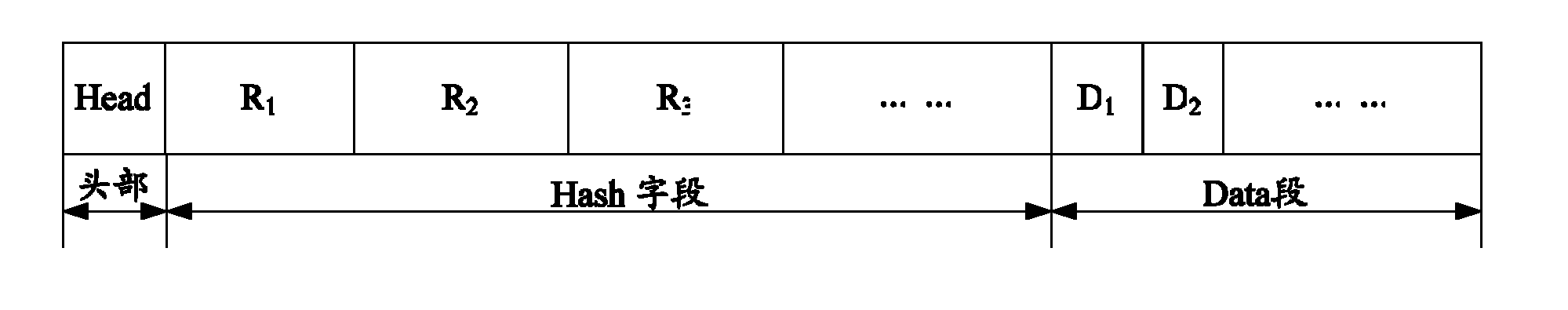

InactiveCN102098221AReduce read and write operationsSimplify Logic Design ComplexityData switching networksInternal memoryCache management

The embodiment of the invention provides a message query method and device. The message query method comprises the steps: receiving a message and writing the message into a cache; sending a message query request which comprises the address information of a message header of the message in the cache; receiving a feedback query result, and acquiring the address information of the message header of the message in the cache in the query result; and reading the message from the cache according to the address information of the message header of the message in the cache. The embodiment of the invention supports a bybass scene in multi-flow cache management and simplifies the complexity of logic design. Compared with linked list management, the invention removes the idle address cache and linked list pointer cache, thus saving resources, reducing the read-write operation of an internal memory and being in accordance with the demand of low power consumption.

Owner:HUAWEI TECH CO LTD

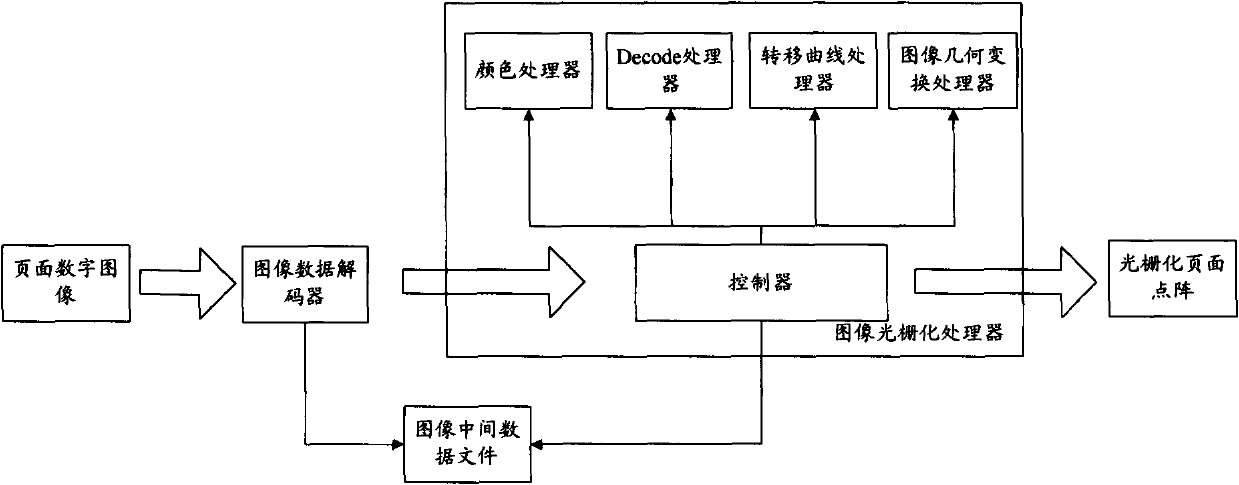

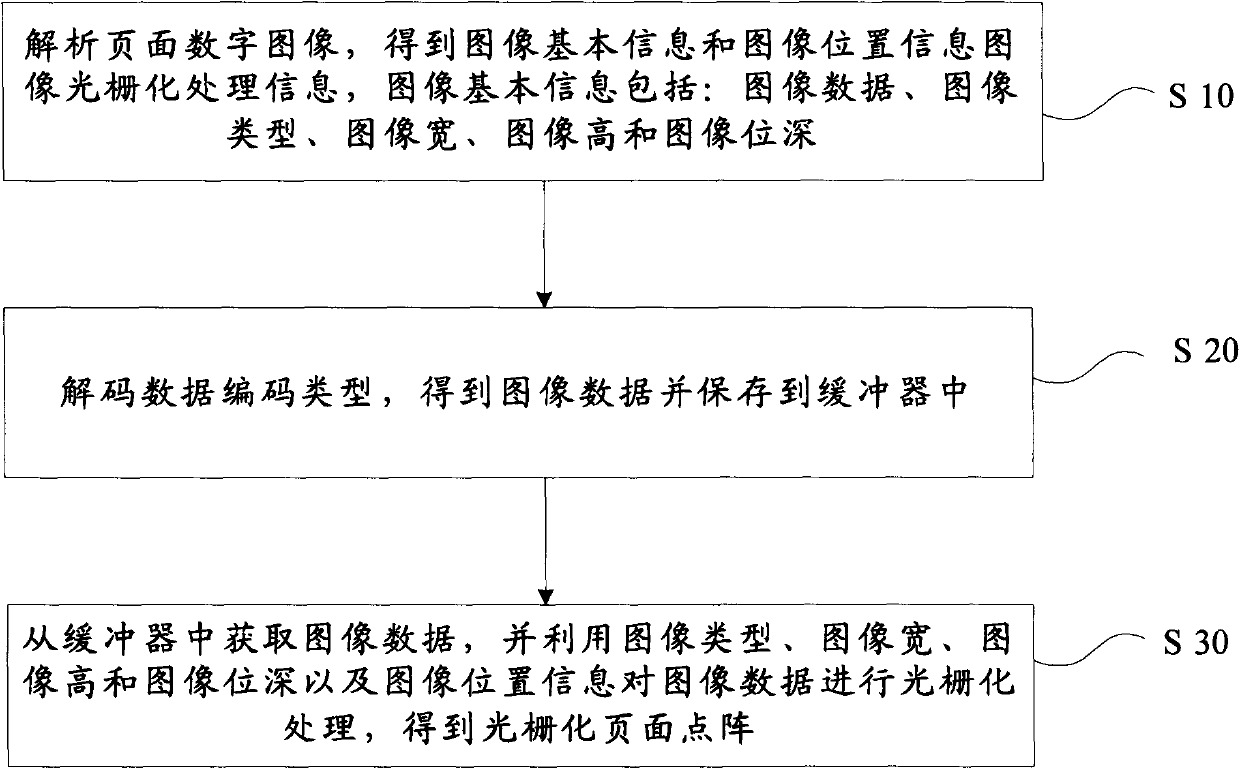

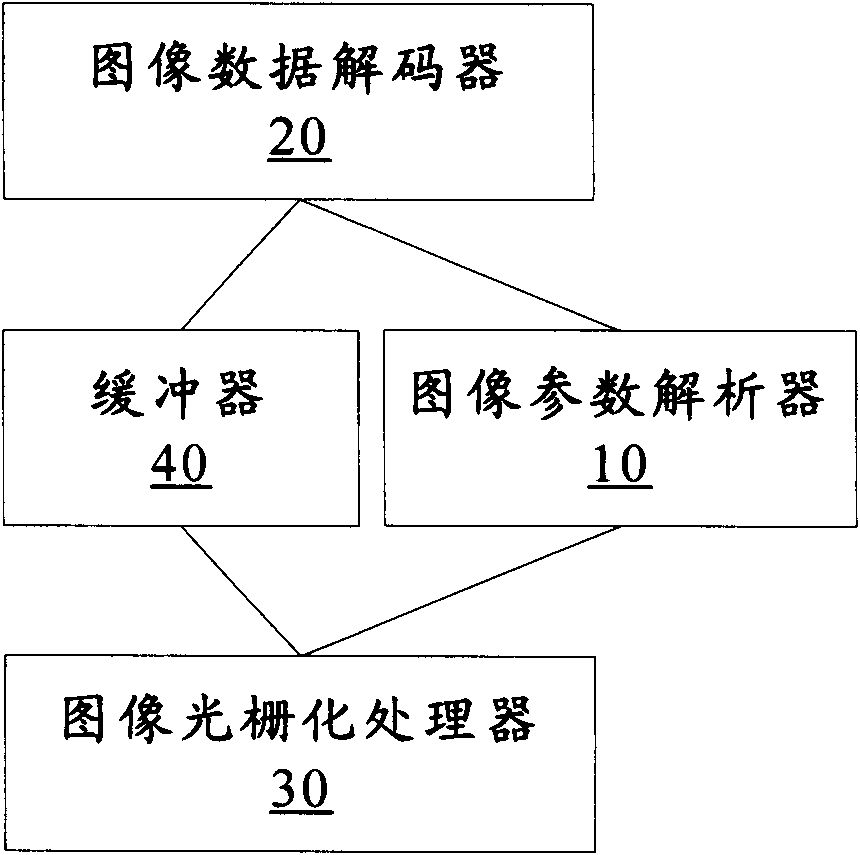

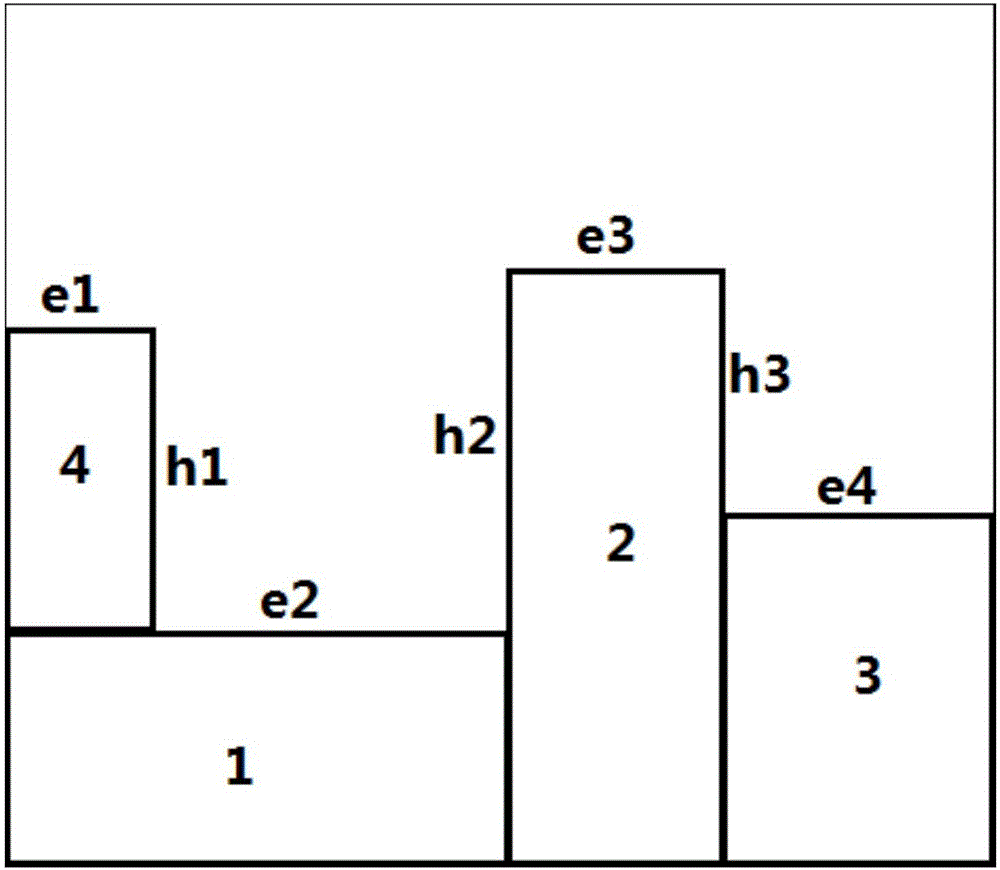

Method and device for rasterization treatment of page digital image

ActiveCN102567945AReduce read and write operationsSolve the problem of low efficiency of frequent disk readingImage memory managementVisual presentationDot matrixData file

The invention provides a method for rasterization treatment of a page digital image, which comprises resolving the page digital image to obtain image rasterization treatment information of image positional information and image essential information comprising image data, image types, image width, image height and image bit depth; decoding data coding types to obtain the image data and saving the image data in a bumper; and obtaining the image data from the bumper and conducting the rasterization treatment on the image data by using the image types, the image width, the image height and the image bit depth to obtain a rasterization page dot matrix. The invention further provides a device for rasterization treatment of the page digital image. The method and the device reduce read-write operation of disc data files in a rasterization treatment process of the digital image, and substantially improve efficiency of the rasterization treatment of the digital image.

Owner:NEW FOUNDER HLDG DEV LLC +1

Method for texture combination of model data

InactiveCN106384389AA lot of solutionsSolve the problem of frequent reading and writingImage data processingPattern recognitionComputers technology

The present invention relates to the computer technology field, and discloses a method for texture combination of model data. The method comprises the following steps: (1) performing peak combination to form the model data of one node when a plurality of model data nodes on the model data construct the hierarchy of a pyramid upwards; (2) performing peak combination of the model data, performing combination of the textures corresponding to the model data, obtaining the original texture information, and obtaining the target texture information; (3) employing a texture putting strategy to put the original texture on the concrete position of the target texture according to the texture coordinate information obtained through the calculation in the step (2), and determining the matching of the width and the height; and (4) in the texture combination process, performing preprocessing of the original texture, wherein the target texture putting rule is that the target textures are putted in from left to right until the combination is completed. According to the invention, the problems are solved that the number of the files is big and the reading and writing are frequent, and the scheduling and drawing cost is reduced.

Owner:ZHEJIANG KELAN INFORMATION TECH CO LTD

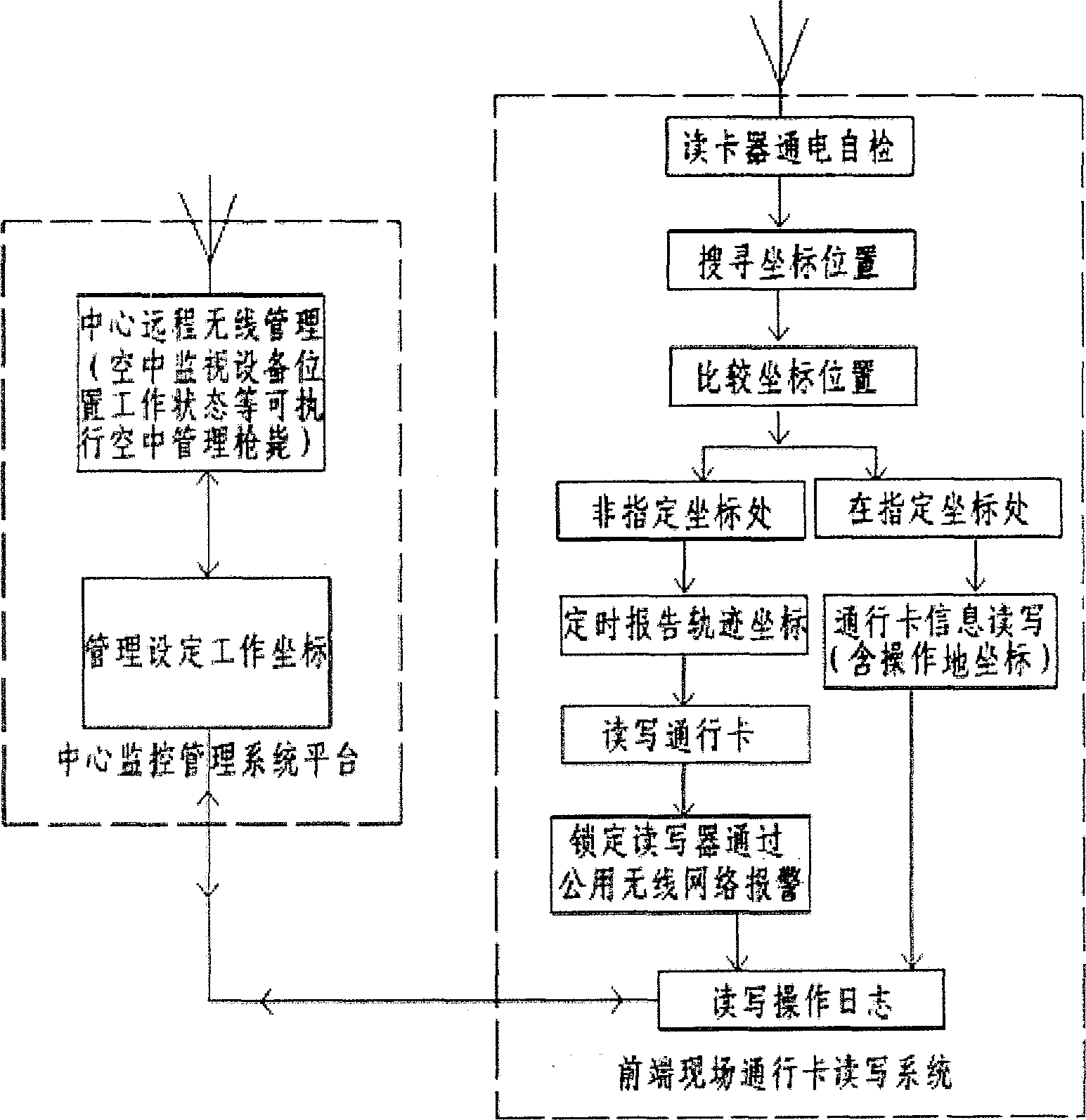

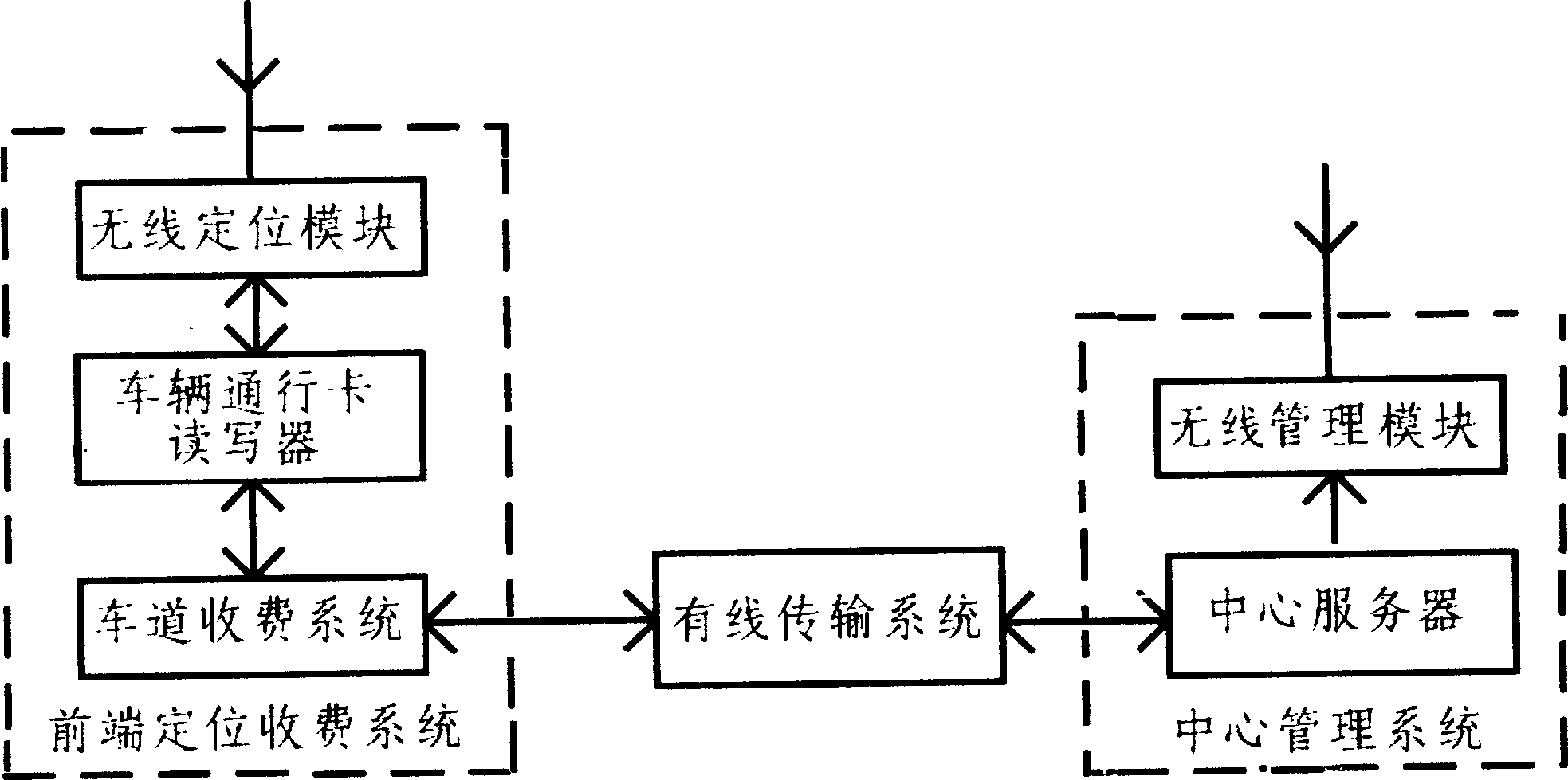

Intelligent road passing RFID (radio frequency identification device) card reader-writer

InactiveCN103236090AImprove fee management functionsReduce read and write operationsTicket-issuing apparatusPoint of entryReader writer

The invention discloses an intelligent road passing RFID (radio frequency identification device) card reader-writer. The card reader-writer comprises a wireless positioning module, a vehicle passing card reader-writer and a lane charging system. The vehicle passing card reader-writer is provided with a microprocessor, a built-in power module, a toll station information read-write module, a path identification module, a positioning and managing module and a communication module inside. Compared with the existing highway passing card reader-writer, the card reader-writer is provided with the vehicle passing card reader-writer and the lane charging system, the reader-writer can only be used in specific positions by locking read-write of the reader-writer, specific position coordinates are automatically overlapped during each read-write, updating of the existing reader-writer for management is achieved, by the intelligent card reader-writer, charging can be performed to specific coordinates at an entrance and an exit, a charging managing function is improved, passing card read-write outside a toll station can be reduced or prevented, and toll avoidance can be reduced.

Owner:CHENGDU YINLIANAN SCI & TECH

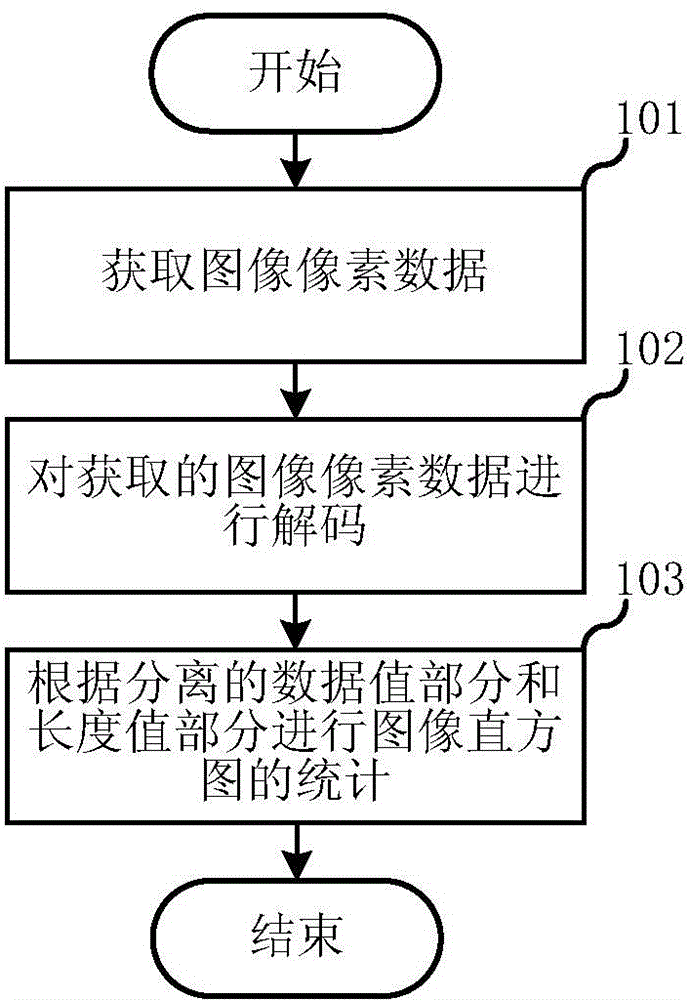

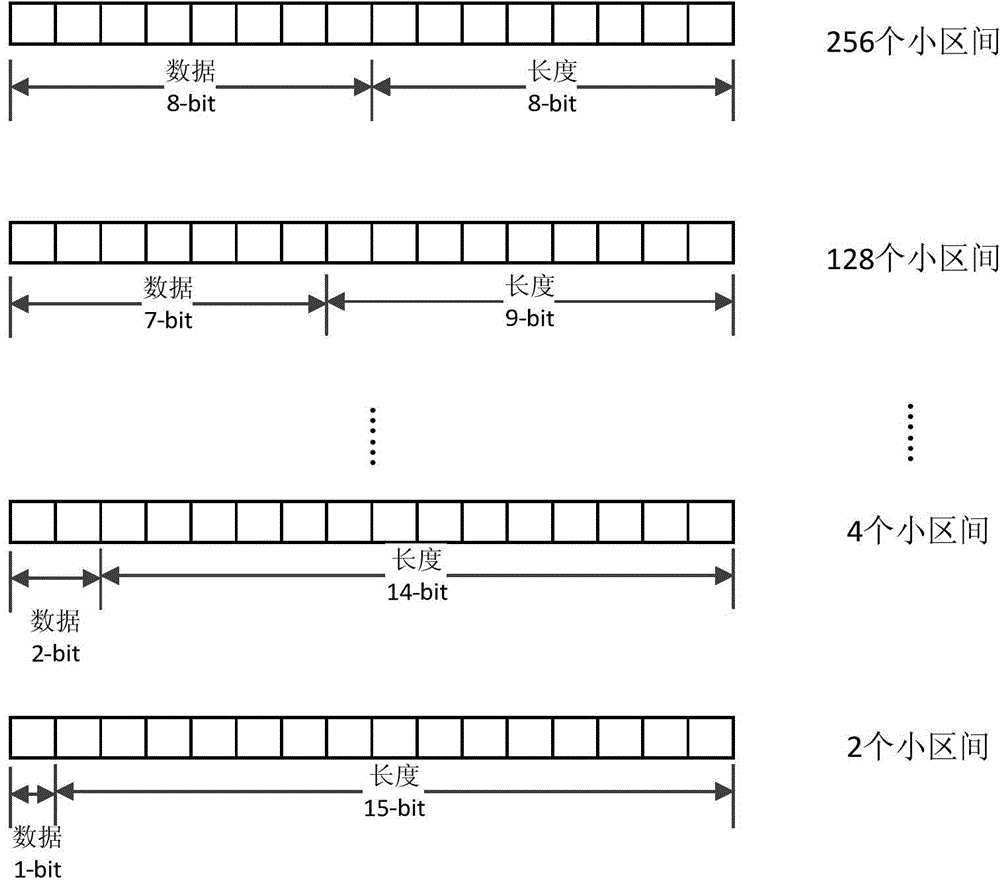

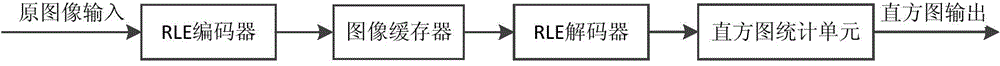

Statistical method of image histogram and system thereof

ActiveCN104809747AReduce read and write operationsShorten the timeImage analysisImage codingImaging processingMethod of images

The invention relates to an image processing technology, and discloses a statistical method of an image histogram and a system thereof. In the method and the system, identical continuous pixels are compressed in advance by means of run length encoding according to the characteristic that the identical continuous pixels exist in original image pixel data, histogram statistics of the identical continuous pixels can be finished in every operation, and the reading and writing operation steps of histogram statistics are reduced, so that the time and power consumption of histogram statistics are reduced greatly. Moreover, run length encoding is performed during acquisition of the original image pixel data, so that idle resources of a system can be utilized fully.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

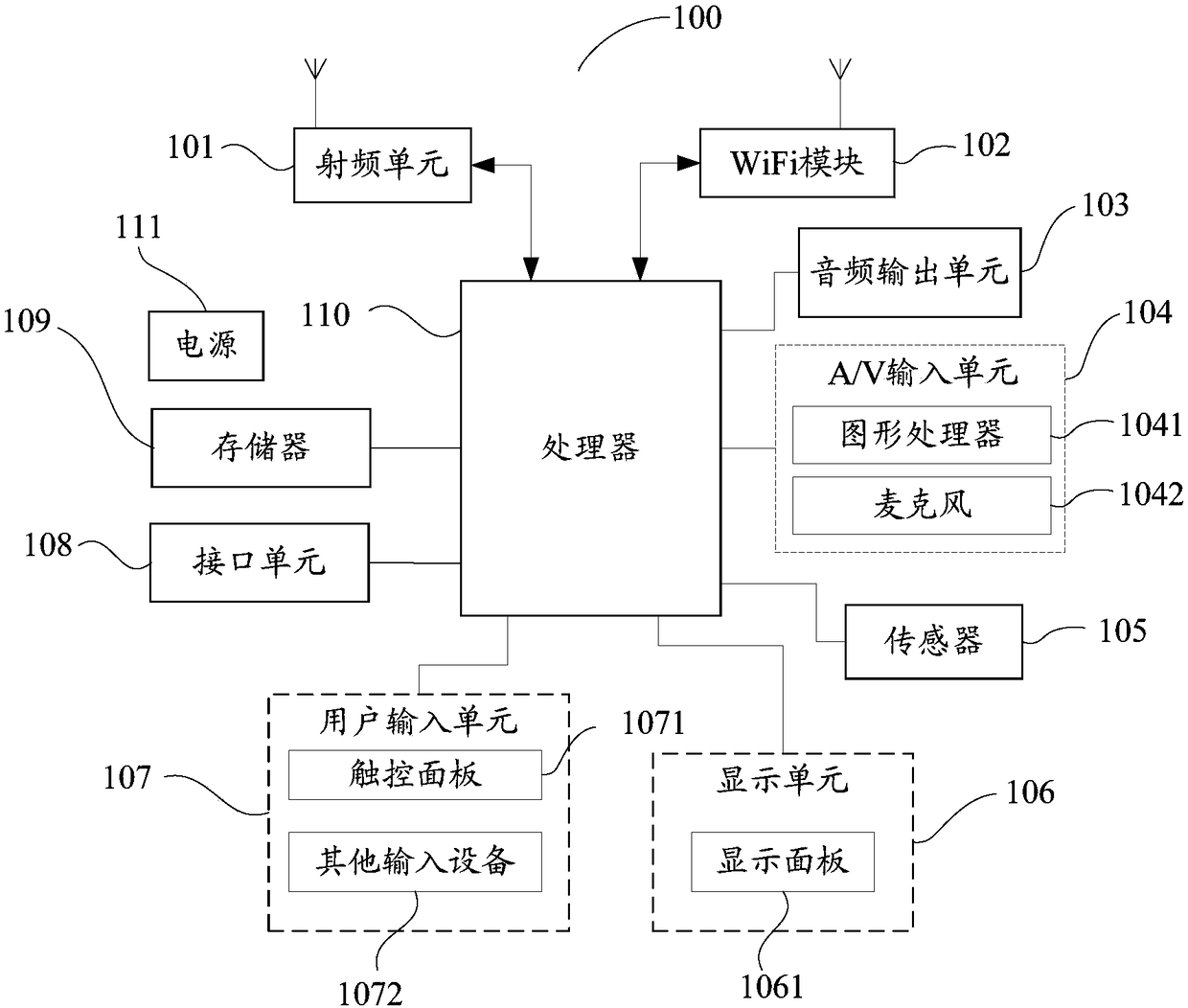

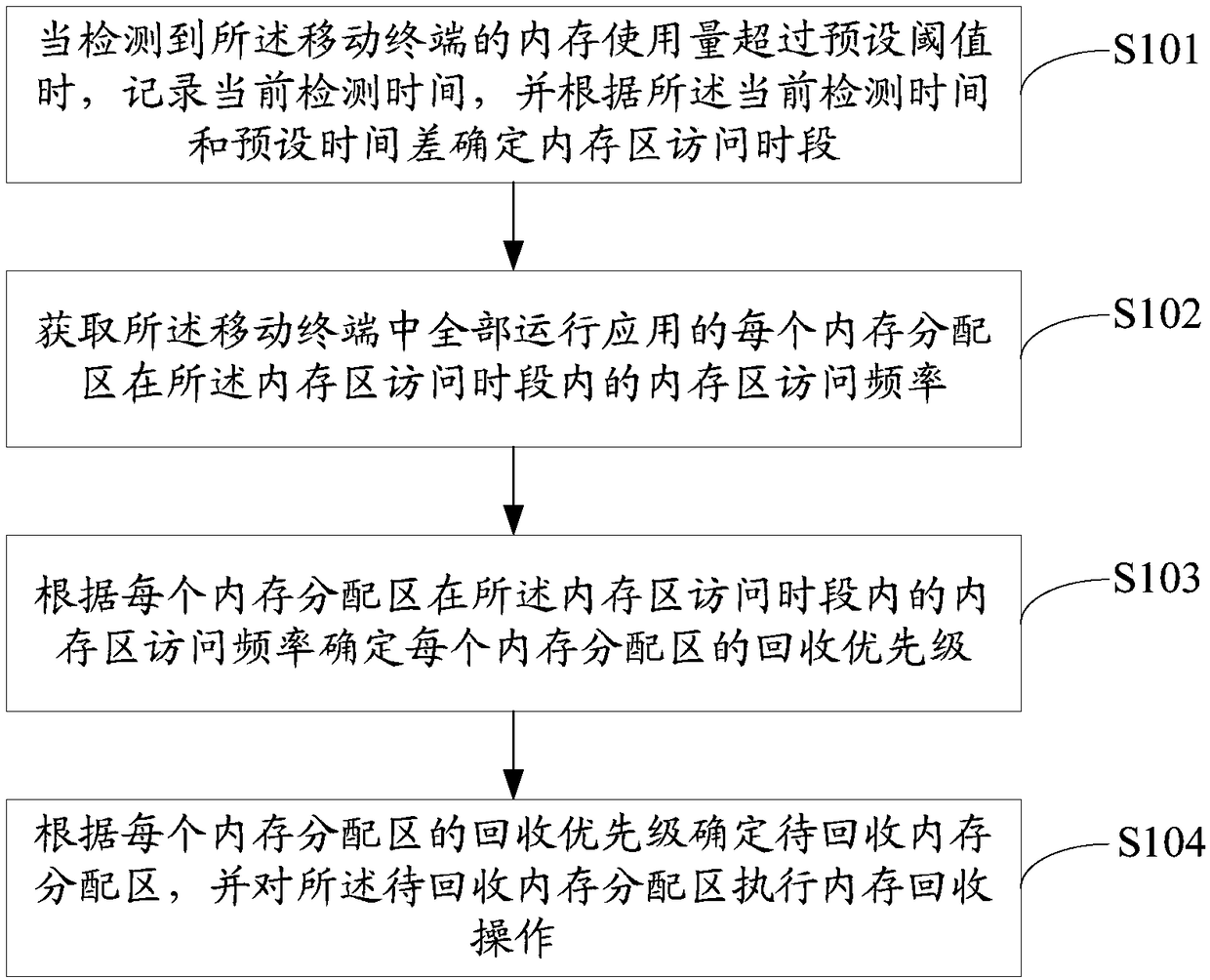

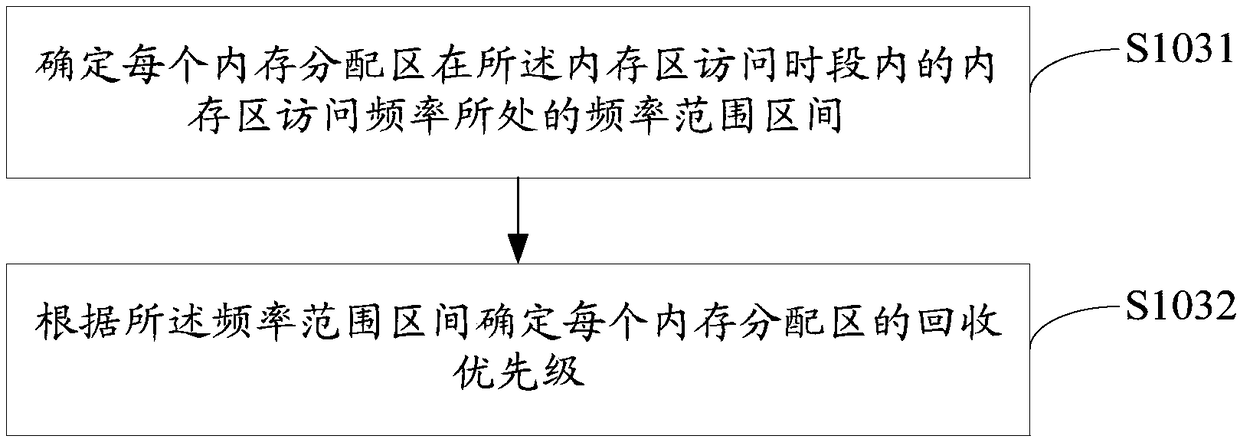

Memory recovery method, mobile terminal and computer readable storage medium

ActiveCN108073458AAccurately determineReduce read and write operationsResource allocationMemory adressing/allocation/relocationRecovery methodAccess frequency

The invention discloses a memory recovery method, a mobile terminal and a computer readable storage medium. The memory usage amount of the mobile terminal is detected; when the current memory usage amount exceeds a preset threshold, current detection time is recorded, a memory area access period is determined according to the difference between the current detection time and preset time; the memory area access frequency of each memory distribution area of all running applications in the memory area access period in the mobile terminal is obtained, the recovery priority of each memory distribution area is determined according to the memory area access frequency of each access distribution area in the memory area access period, finally a to-be-recovered memory distribution area is determinedaccording to the recovery priority of each memory distribution area, memory recovery operation is executed on the to-be-recovered memory distribution area, so that to-be-recovered memory data can bedetermined accurately, the disk read-write operation is effectively reduced, and the system performance is improved.

Owner:NUBIA TECHNOLOGY CO LTD

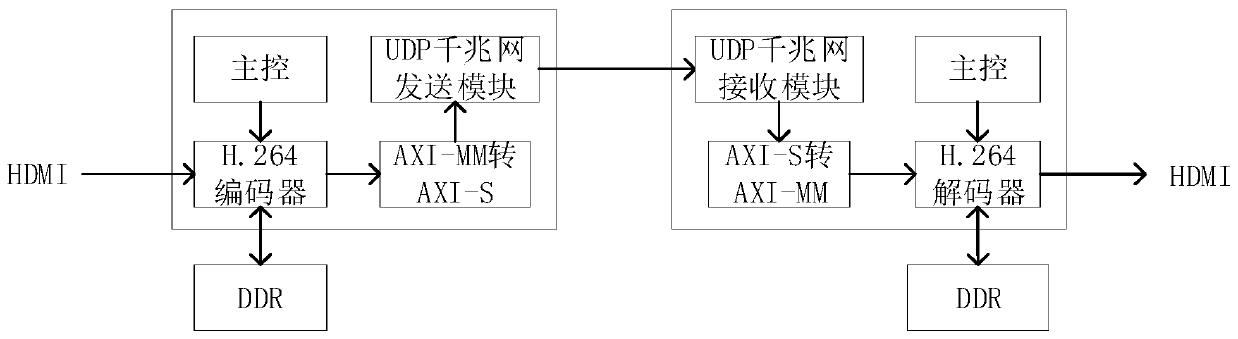

FPGA-based H.264 video encoding end, decoding end, transmission device and transmission method

PendingCN110971908ALower latencyReduce bandwidth requirementsDigital video signal modificationData packWireless image transmission

The invention provides an FPGA-based H.264 video coding end, an H.264 video decoding end, a transmission device and a transmission method. The method comprises steps that H.264 video coding end videodata is sent; the H.264 video encoder receives the video data and starts encoding; each time 128-byte coded data is generated, the 128-byte coded data is sent to the AXI-MM-to-AXI-S module in real time, the AXI-MM-to-AXI-S module processes the coded data and then sends the coded data to the UDP Ethernet sending module, and the UDP Ethernet sending module starts sending every 128-byte data; after receiving the compressed code stream data packet, a UDP Ethernet receiving module of the H.264 video decoding end transmits the compressed code stream data packet to an RAM in an AXI-S-to-AXI-MM modulefor caching; after the AXI-S to AXI-MM module detects a data frame header, the AXI-S to AXI-MM module delays for 3ms and sends a decoding start interrupt to the decoding end main control module; andthe decoding end main control module controls the H.264 video decoder to start decoding, and the H.264 video decoder reads data from the RAM in the AXI-S-to-AXI-MM conversion module and decodes and outputs a video. The overall delay of a coding and decoding system is remarkably reduced, and the method is very suitable for low-bandwidth transmission modes such as wireless image transmission.

Owner:HUNAN JUNHAN INFORMATION TECH CO LTD

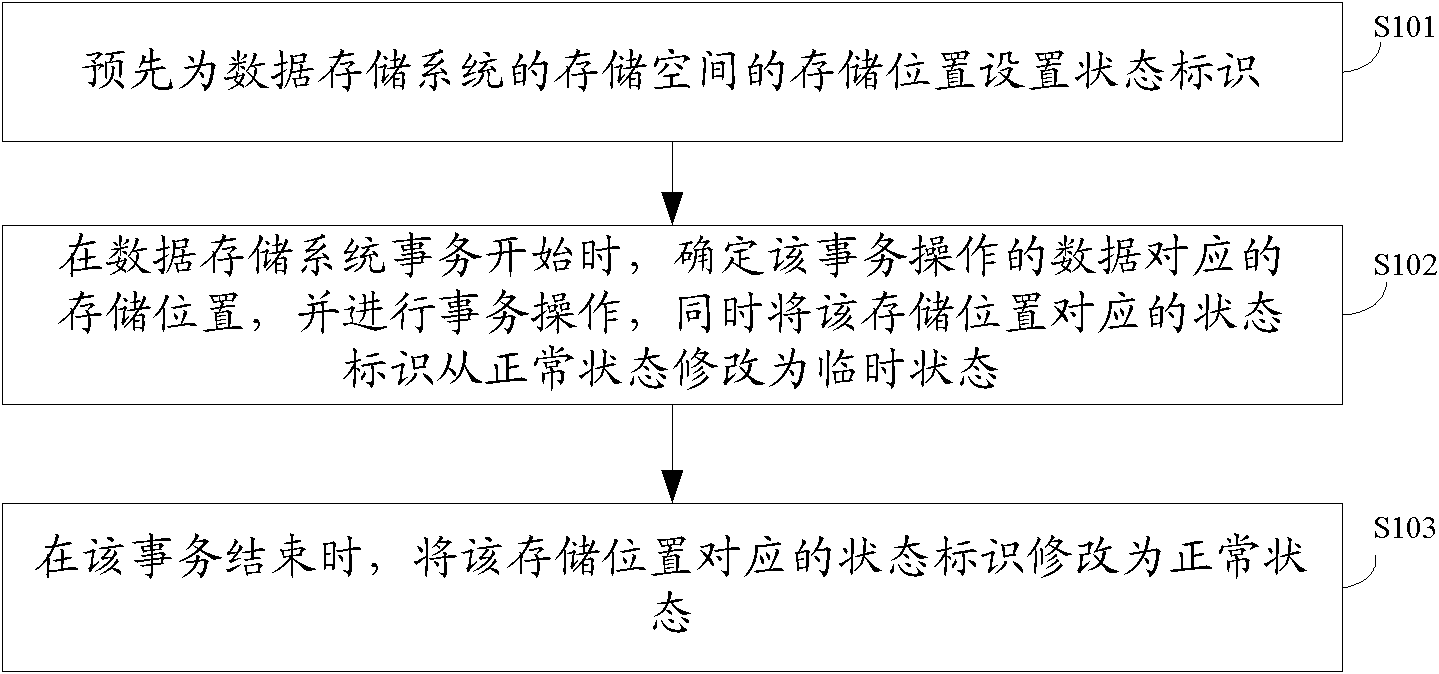

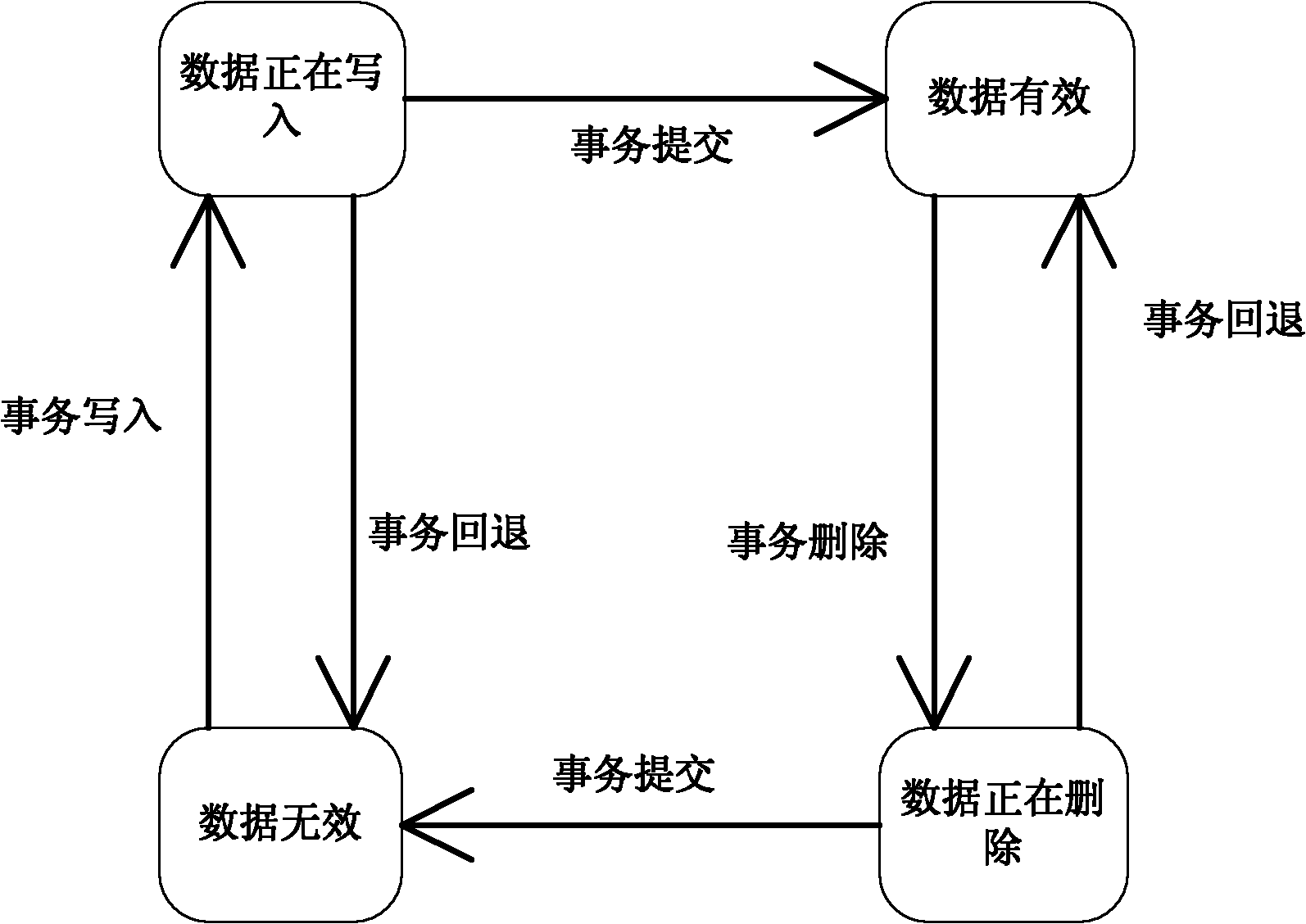

Method and device for realizing transaction of data storage system

InactiveCN102024052AImprove processing efficiencyReduce read and write operationsSpecial data processing applicationsData storage systemOperating system

The invention relates to the field of data management, and discloses a method and a device for realizing the transaction of a data storage system, which can reduce the reading and writing operations of a memory, increase the space utilization rate of the memory and improve the transaction processing efficiency. The method provided by the invention comprises the following steps of: at the transaction begin of the data storage system, determining the storage position of data corresponding to a transaction operation, executing the transaction operation, and simultaneously modifying a state identifier corresponding to the storage position from a normal state to a temporary state; and at the end of the transaction, modifying the state identifier corresponding to the storage position from the temporary state to the normal state, wherein the storage position is in a memory space and used for storing data; and the state identifier is used for identifying the state information of the data at the storage position.

Owner:BEIJING WATCH DATA SYST

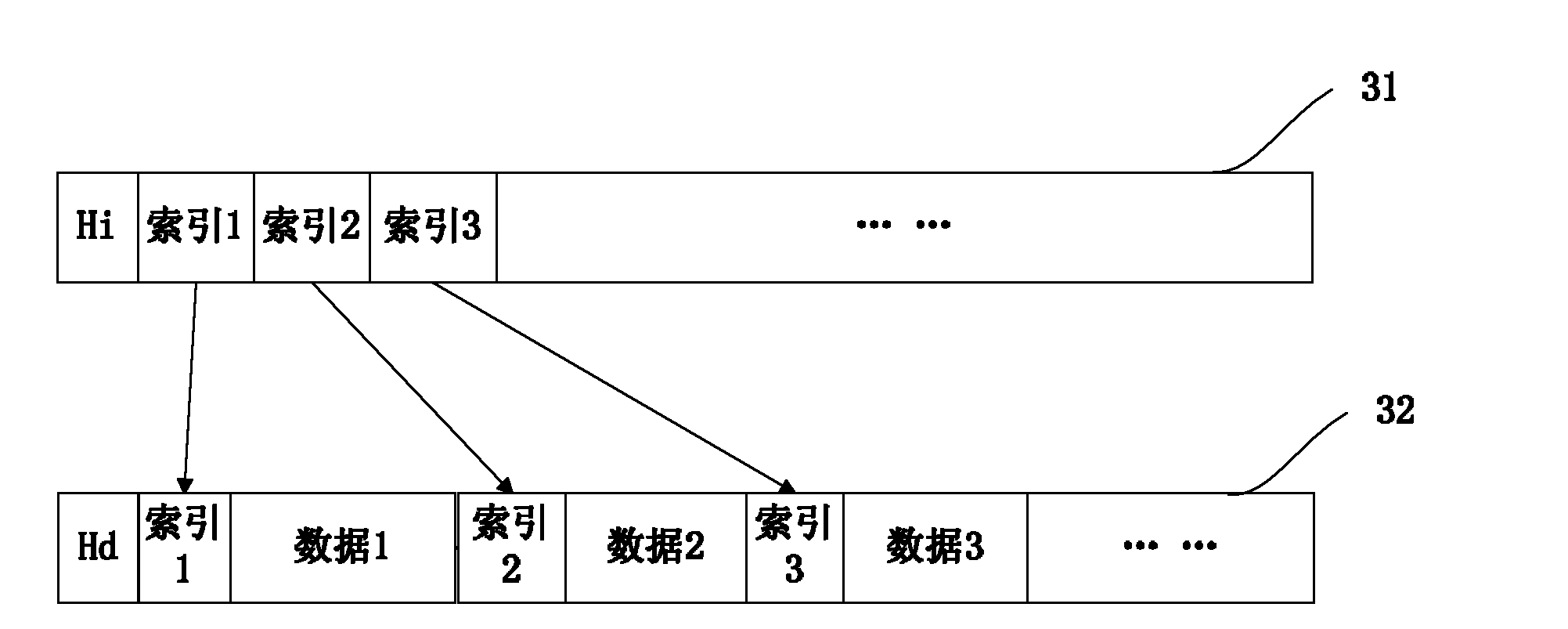

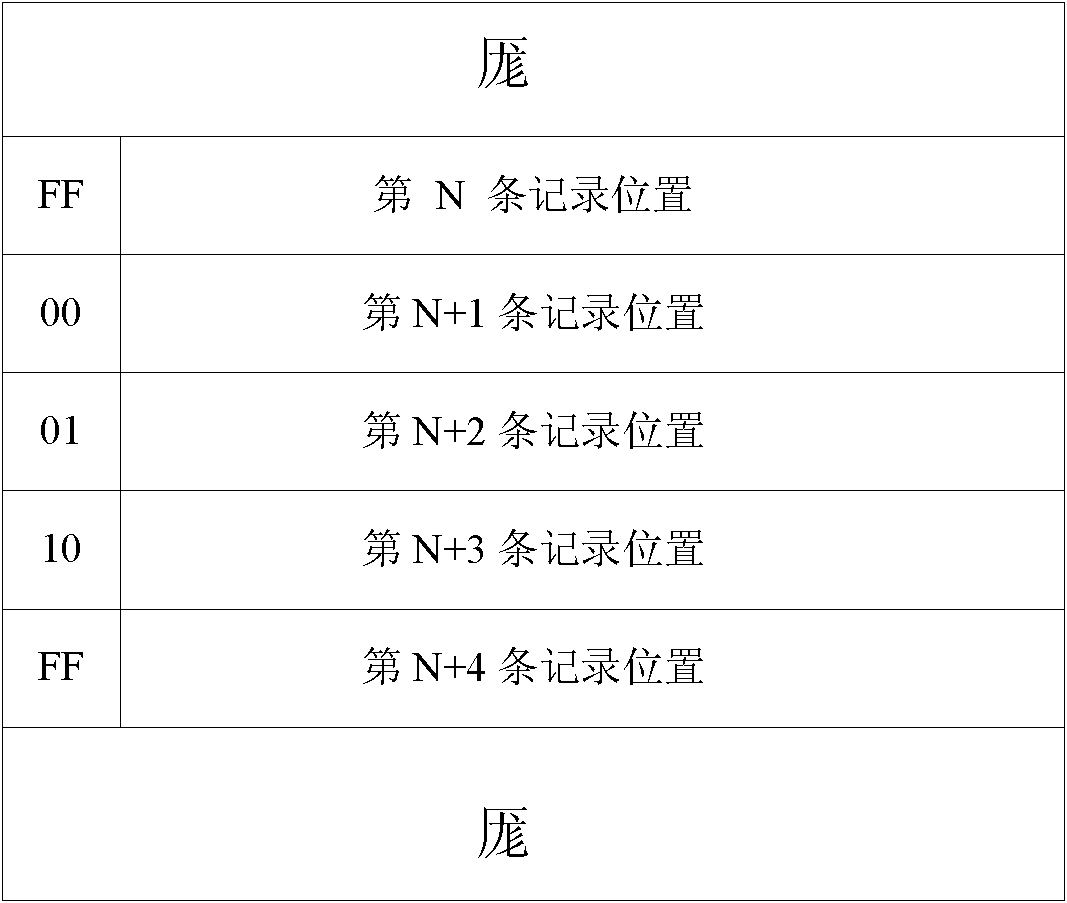

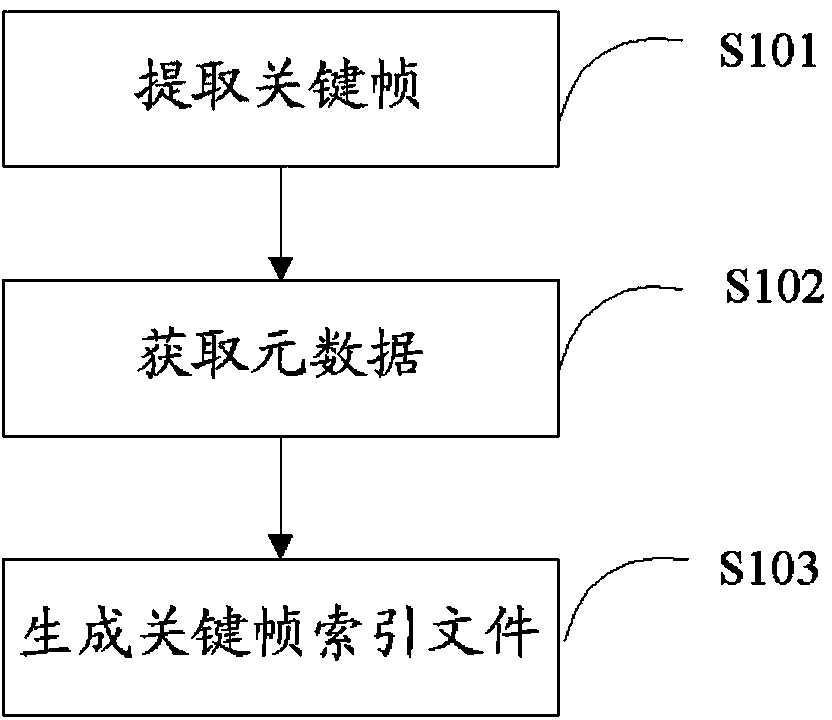

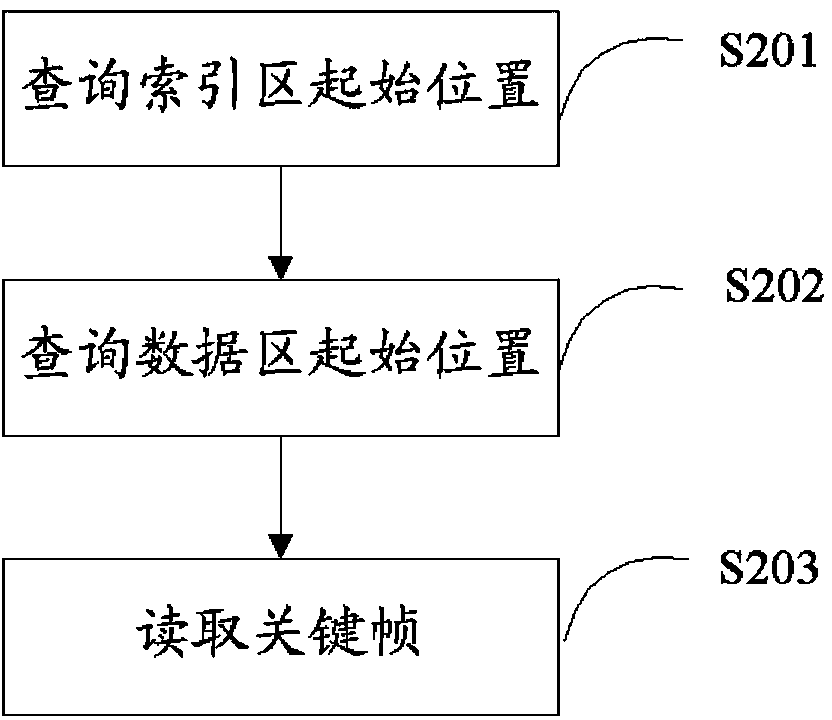

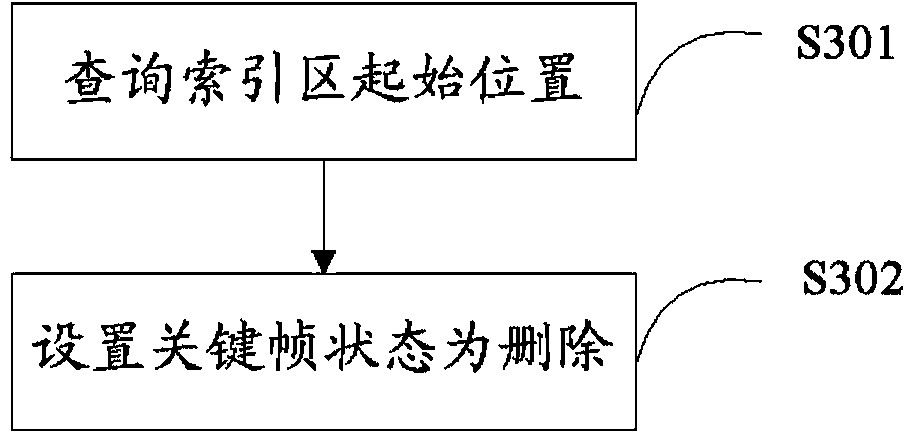

Key frame processing method and system

ActiveCN103905694AEasy to manageEasy backupTelevision system detailsColor television detailsComputer hardwareKey frame

The invention provides a key frame processing method. The key frame processing method comprises the steps that a key frame is extracted from a video file; metadata of the key frame are obtained; a key frame index file is generated in a preset file storage format by the utilization of the key frame and the metadata of the key frame. In addition, the invention provides a key frame processing system. According to the key frame processing method and system, the multiple key frame data and the related metadata are stored to be the single file with the index information, and therefore read-write operation of the system storage is reduced, the system performance is improved, the file is managed and backed up conveniently, and the efficiency of obtaining the key frame information is ensured.

Owner:CHINA CENTRAL TELEVISION +1

Magnetic random access memory with error correction and compression circuit

ActiveCN110660421AReduce read and write operationsTroubleshoot data errorsDigital storageMemory cellRandom access memory

The invention provides a magnetic random access memory with an error correction and compression circuit. The magnetic random access memory comprises a memory cell array, an error detection and correction circuit, a compression and decompression circuit, a control circuit, a status bit cache and a data cache, the reading operation steps of the chip are as follows: obtaining first compressed data inthe memory cell array, processing the first compressed data through the error detection and correction circuit, decompressing the processed first compressed data through the compression and decompression circuit to obtain first data, and outputting the first data; and the chip performs the following writing operation steps: compressing second data to be written through the compression and decompression circuit to obtain second compressed data, processing the second compressed data through the error detection and correction circuit, and writing the processed second compressed data into the memory cell array.

Owner:SHANGHAI CIYU INFORMATION TECH

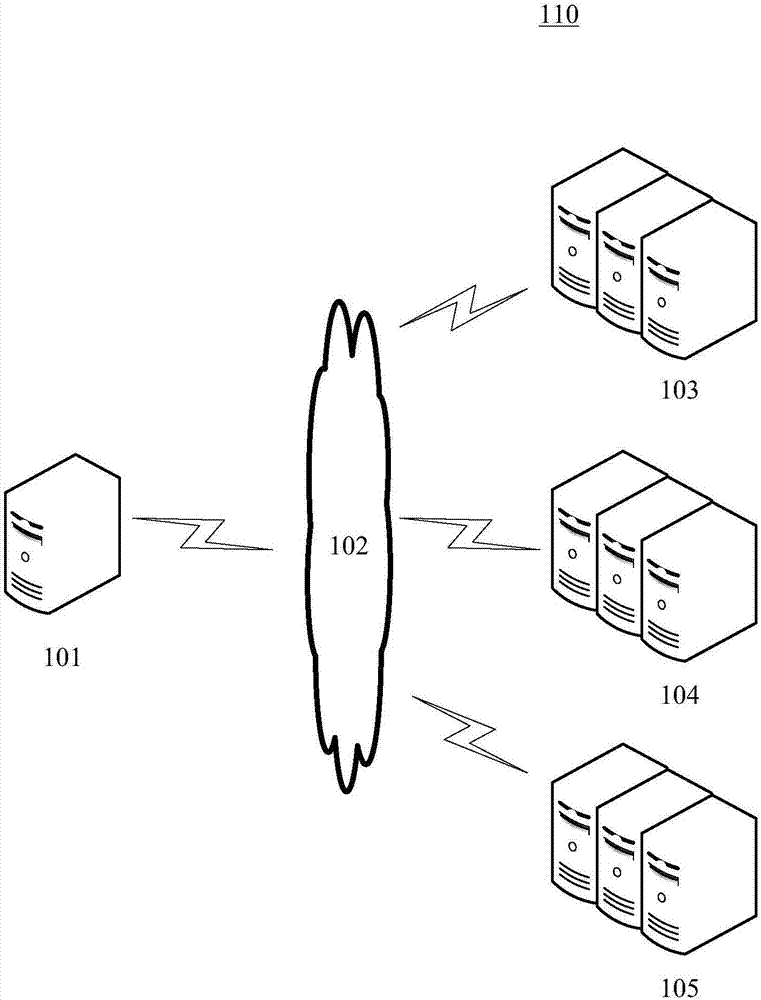

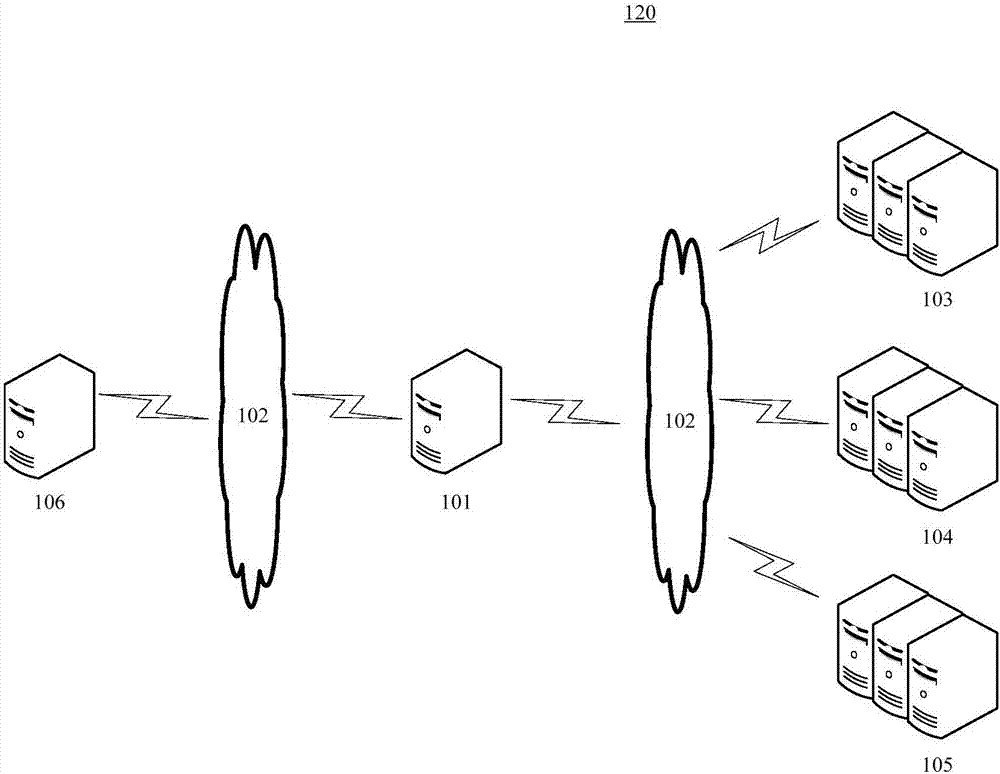

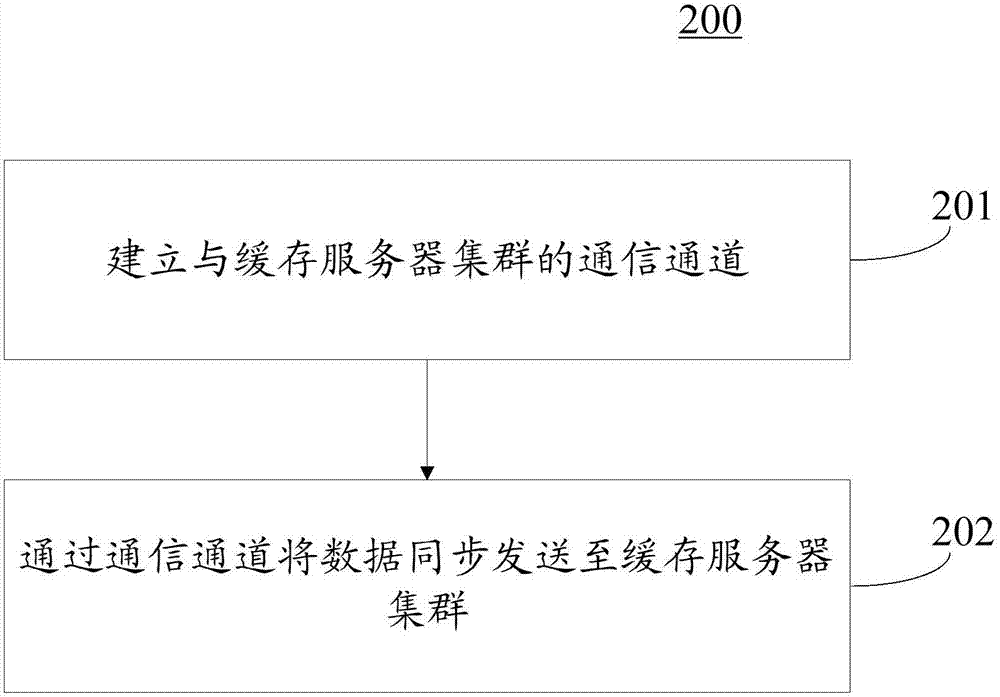

Distributed cache system and data cache method and apparatus thereof

ActiveCN107979629AReduce read and write operationsImprove operational efficiencyTransmissionData synchronizationApplication server

The invention discloses a distributed cache system and a data cache method and apparatus thereof. A specific embodiment of the system comprises an application server and a cache server cluster establishing a communication channel with the application server, wherein the cache server cluster comprises at least one of the following: a first cache server cluster located in a machine room where the application server is located, and at least one second cache server cluster located in other machine rooms different from the machine room; the application server is used for synchronously sending datato the cache server cluster through the communication channel; and the cache server cluster is used for receiving and caching the data sent by the application server through the communication channel.By adoption of the distributed cache system provided by the embodiment, the operation efficiency of the distributed cache system is improved.

Owner:BEIJING JINGDONG SHANGKE INFORMATION TECH CO LTD +1

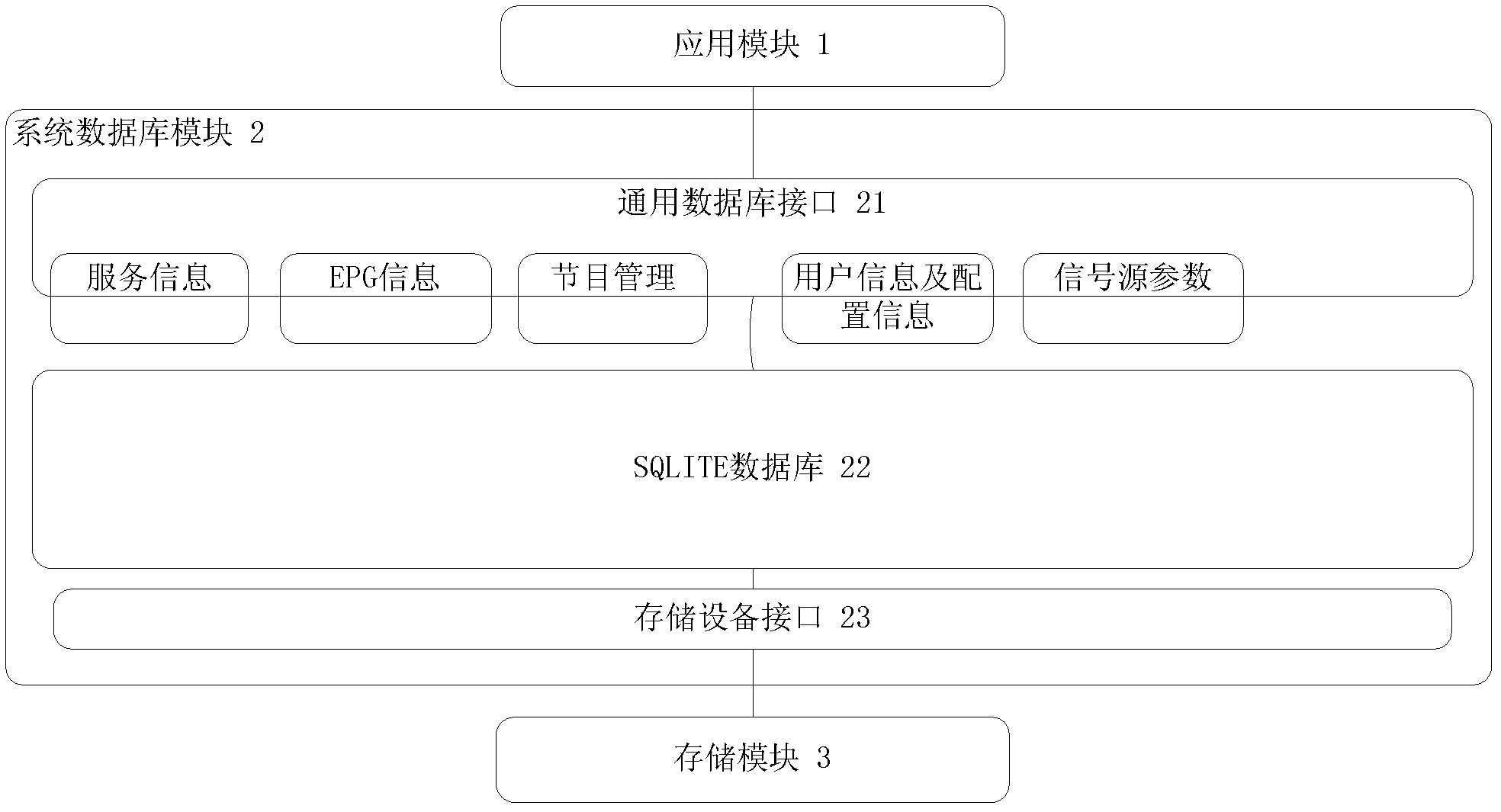

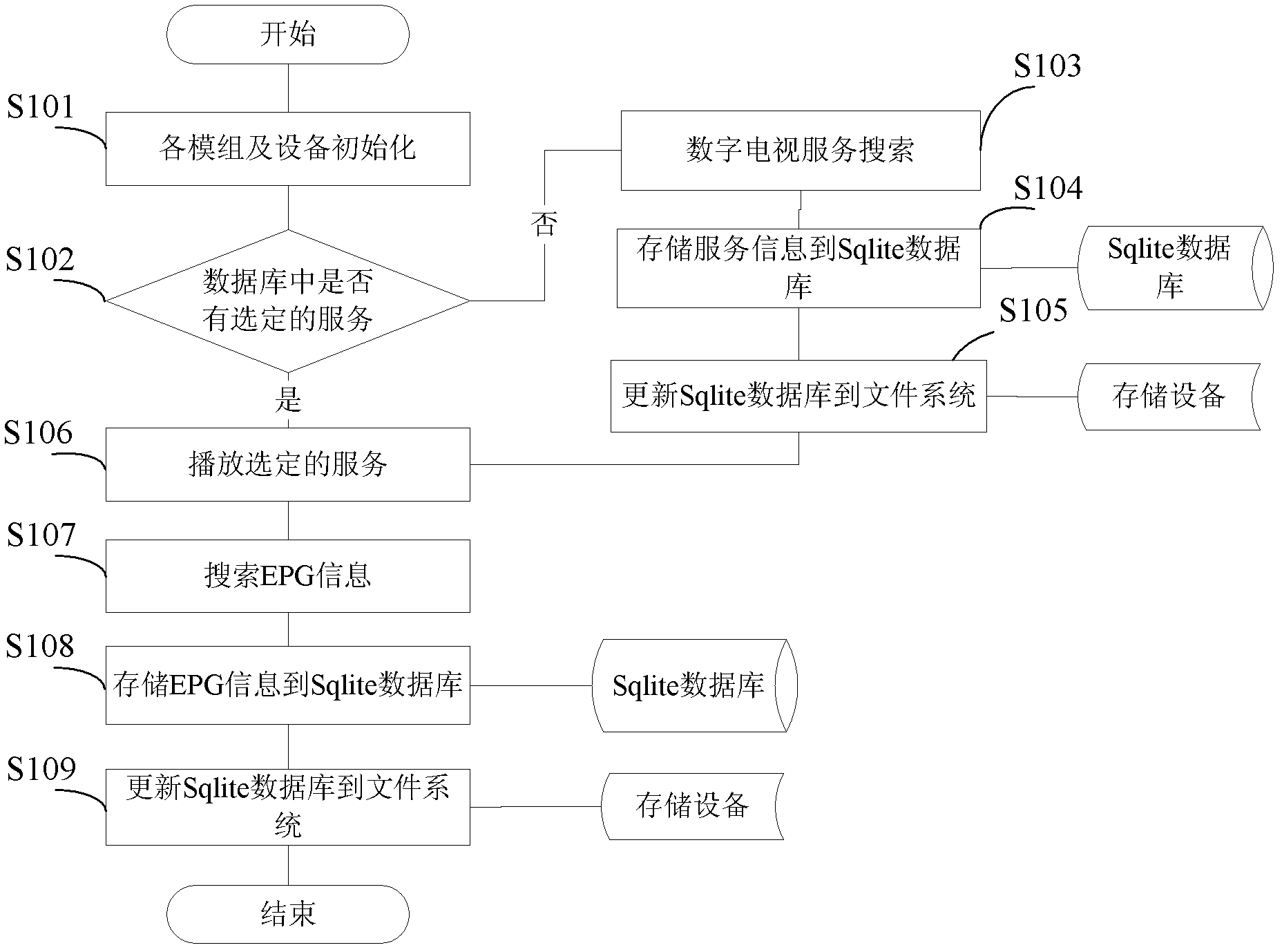

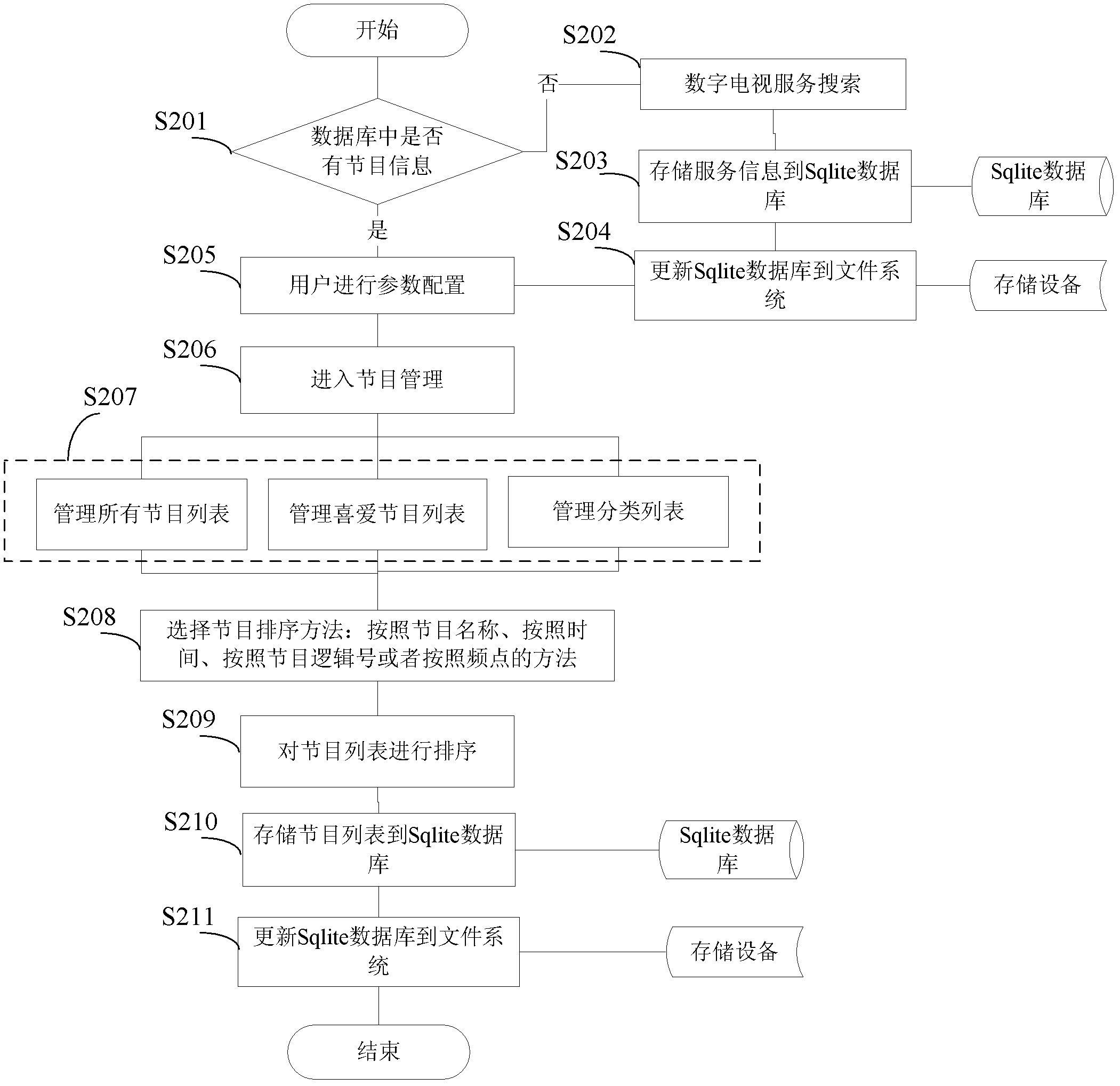

Information management method and system of digital television

InactiveCN103136216AReduce read and write operationsImprove data access efficiencySelective content distributionSpecial data processing applicationsDatabase interfaceData access

The invention provides an information management method and a system of a digital television. The method includes that a system data base is built and comprises a universal data base port, an SQLITE data base and a storage device port, and information of the digital television is stored in the SQLITE data base; the SQLITE data base is managed by calling the universal data base port and structured query language (SQL) statements of the universal data base port; and the SQLITE data base is stored through the storage device port. The information management method and the system can improve data access efficiency and reduce writing and reading operation of a storage device.

Owner:SHENZHEN KAIFA TECH

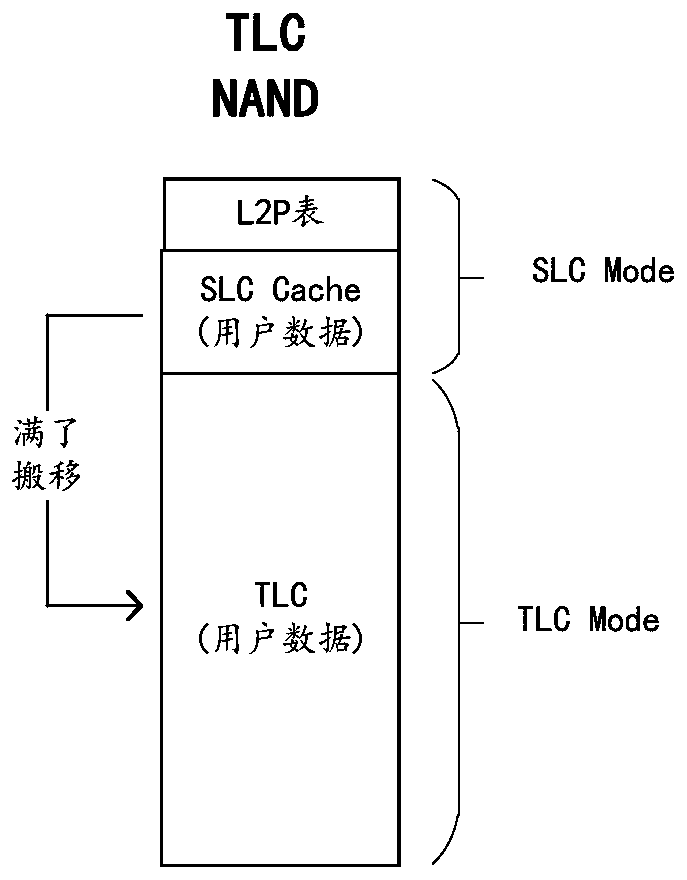

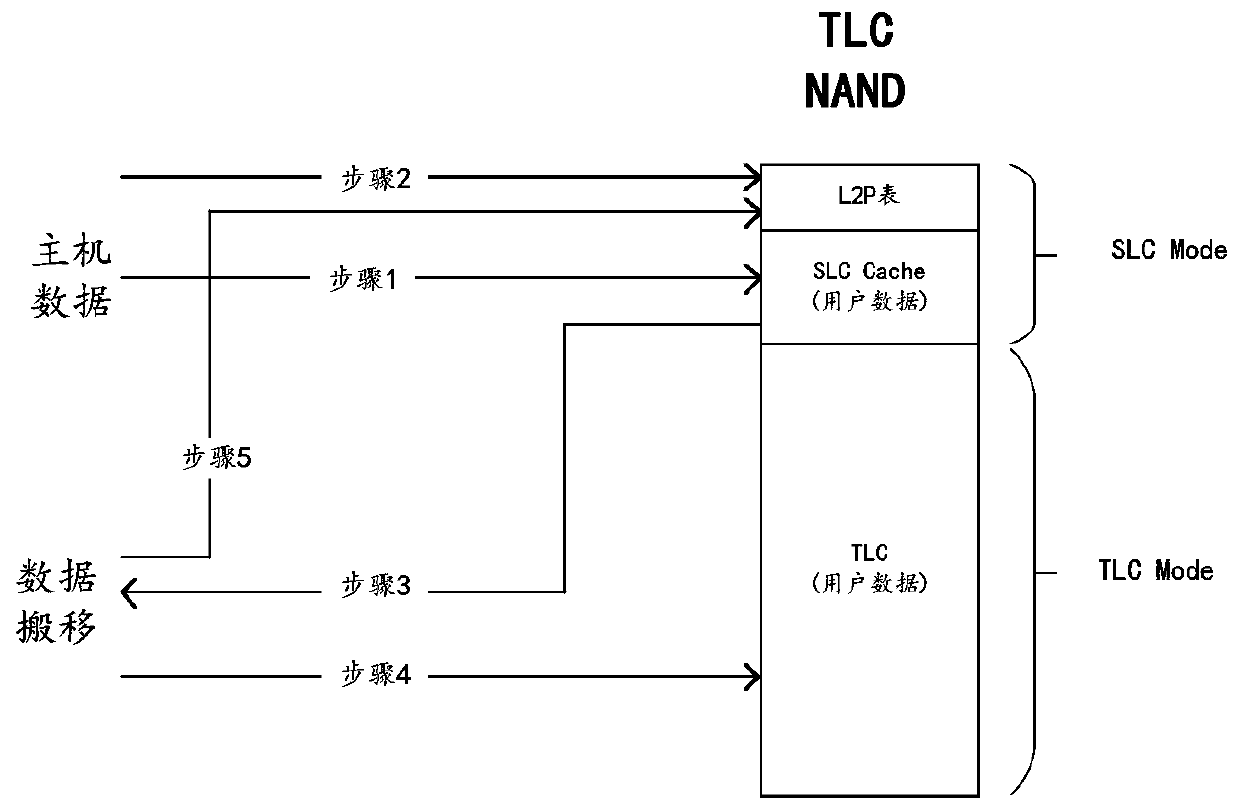

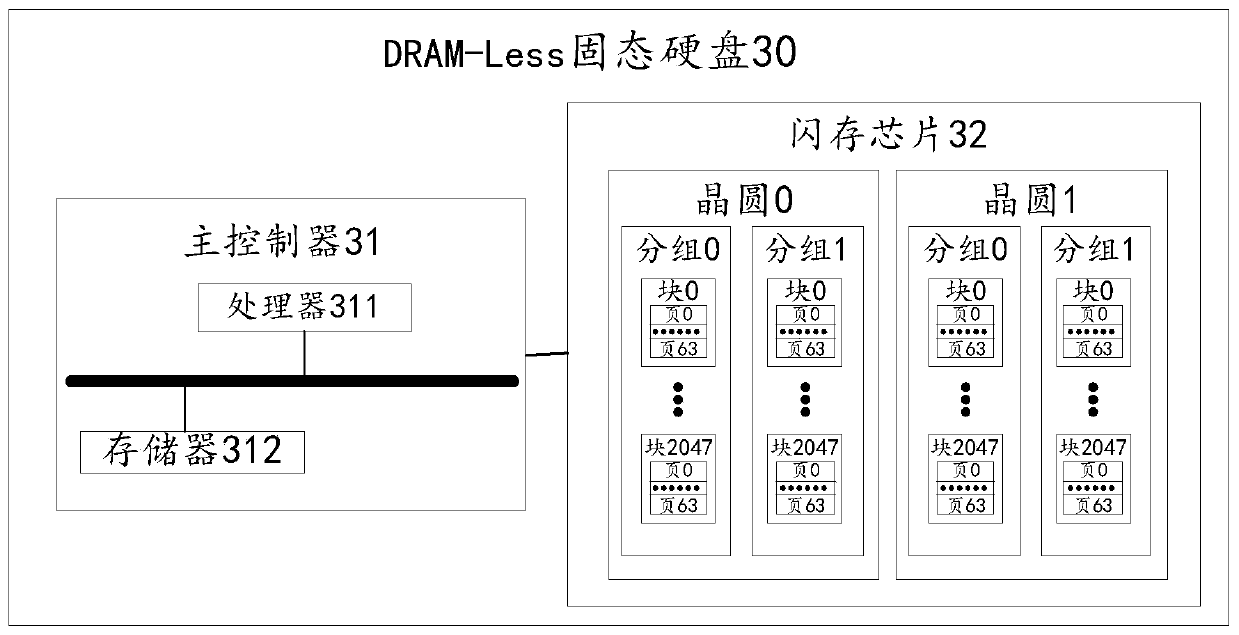

Data random writing method and device of DRAM-Less solid state disk and DRAM-Less solid state disk

ActiveCN110531928AImprove random write performanceIncrease write speedInput/output to record carriersEnergy efficient computingSolid-state driveComputer science

The embodiment of the invention relates to the field of solid state disk application, and discloses a random data writing method and device of a DRAM-Less solid state disk and the DRAM-Less solid state disk. The data random writing method of the DRAM-Less solid state disk comprises the following steps: configuring at least one SLC physical block for a group, and establishing a binding relationshipbetween each SLC physical block and a non-SLC physical block in the group; and receiving data sent by a Host end through the SLC physical block, and when the memory of the SLC physical block is full,copying data of all physical pages of the SLC physical block to a bound non-SLC physical block according to the binding relationship. By means of the mode, read-write operation on the flash memory can be effectively reduced in a random write scene, and the random write performance and the write speed of the DRAM-Less solid state disk are improved.

Owner:SHENZHEN DAPU MICROELECTRONICS CO LTD

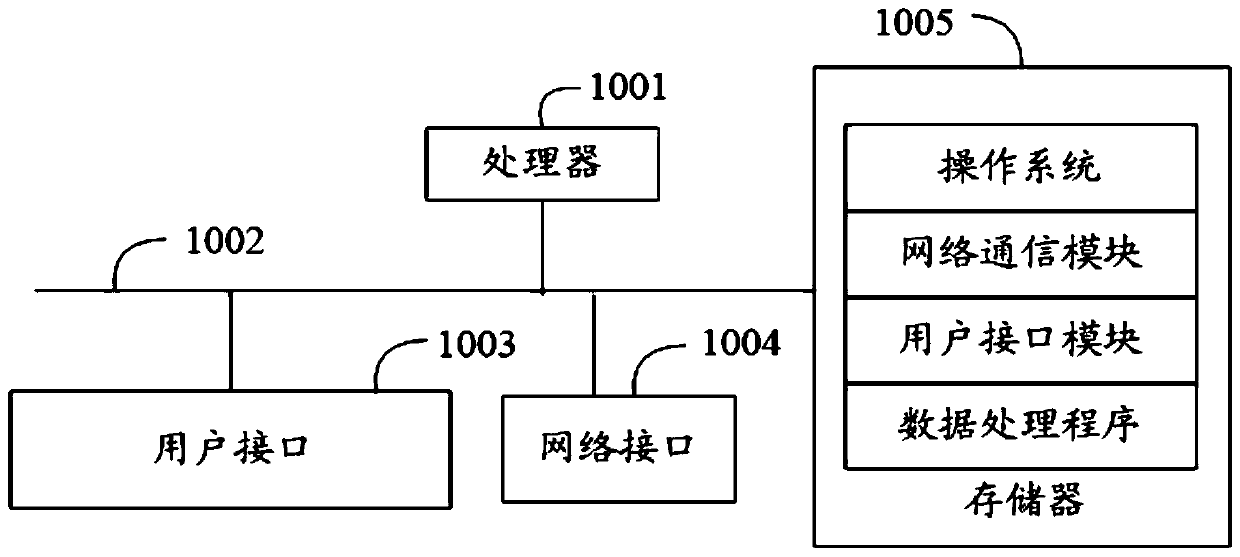

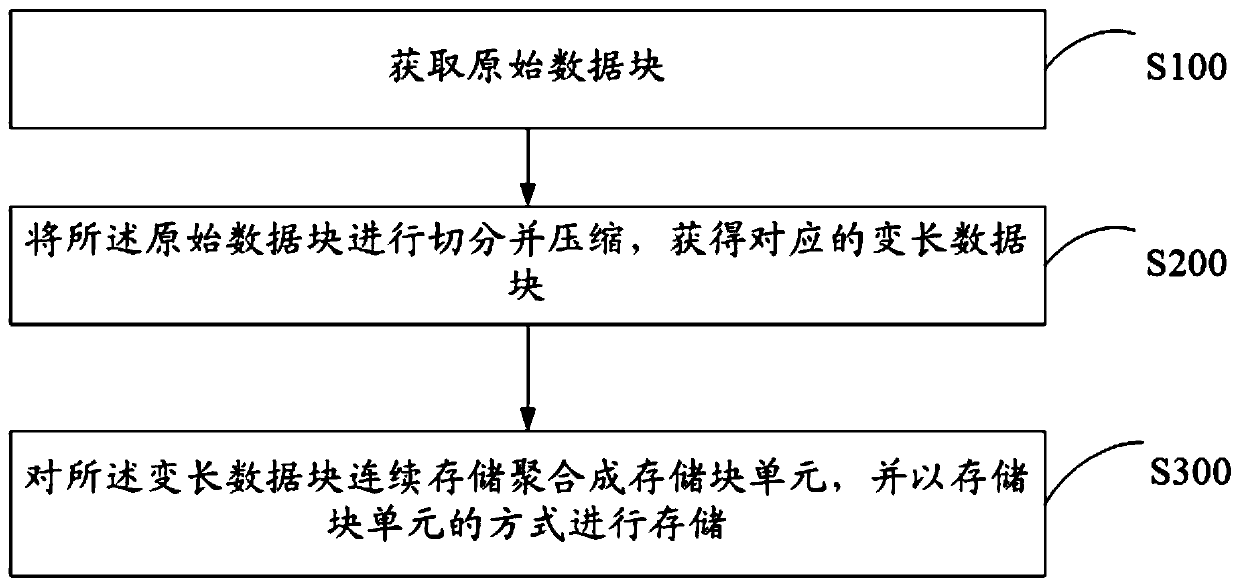

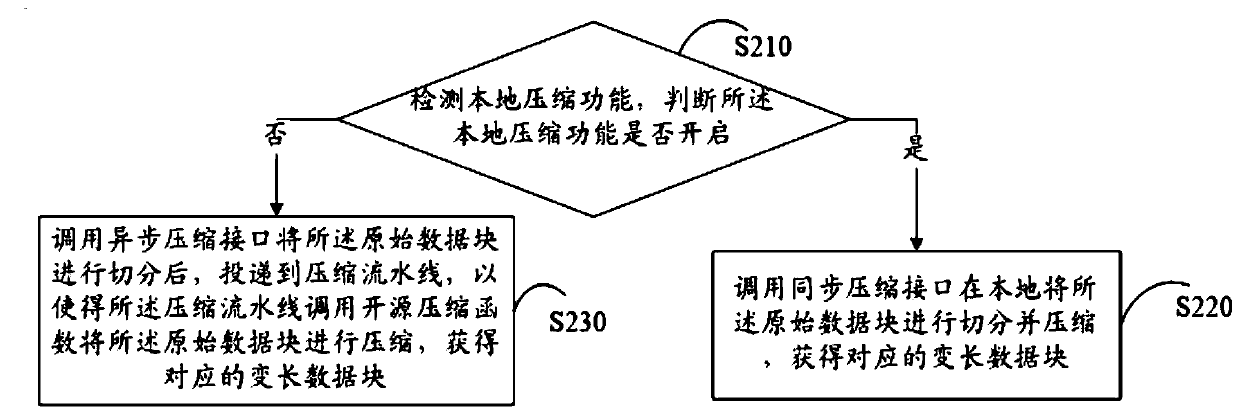

Data processing method, virtual device, equipment and storage medium

PendingCN111159202AImprove read and write performanceReduce read and write operationsDatabase updatingSpecial data processing applicationsData processingMemory block

The invention discloses a data processing method. The method comprises the steps of obtaining an original data block, segmenting and compressing the original data block to obtain a corresponding variable-length data block, continuously storing and aggregating the variable-length data blocks into a storage block unit, and storing the variable-length data blocks in the form of the storage block unit. The invention further discloses data processing equipment and a computer readable storage medium. According to the invention, the use efficiency of the storage space can be improved, so that the storage space required for data storage is reduced.

Owner:SANGFOR TECH INC