Method for interlacing rate matching and de-interlacing off-rate matching

A matching method and interleaving rate technology, applied in network traffic/resource management, digital transmission systems, electrical components, etc., can solve problems such as many buffer read and write operations, difficult resource sharing, and difficult resource sharing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

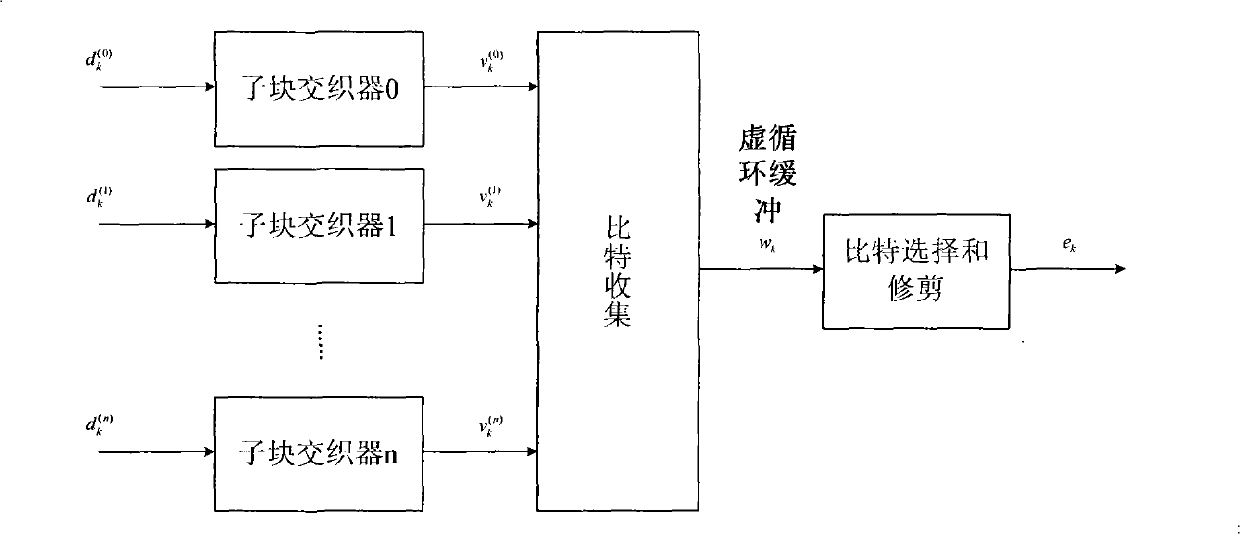

[0108] In this embodiment, a mask matrix is introduced to record the effectiveness of each bit in the sub-block interleaving matrix, and after the sub-block interleaving process is performed by using the interleaving operator, the bits to be output are directly processed according to the redundancy version number Interleave processing, and write the interleaved bit stream directly into the code block cascade buffer to achieve rate matching.

[0109] Specifically, the flow of the rate matching method in this embodiment includes:

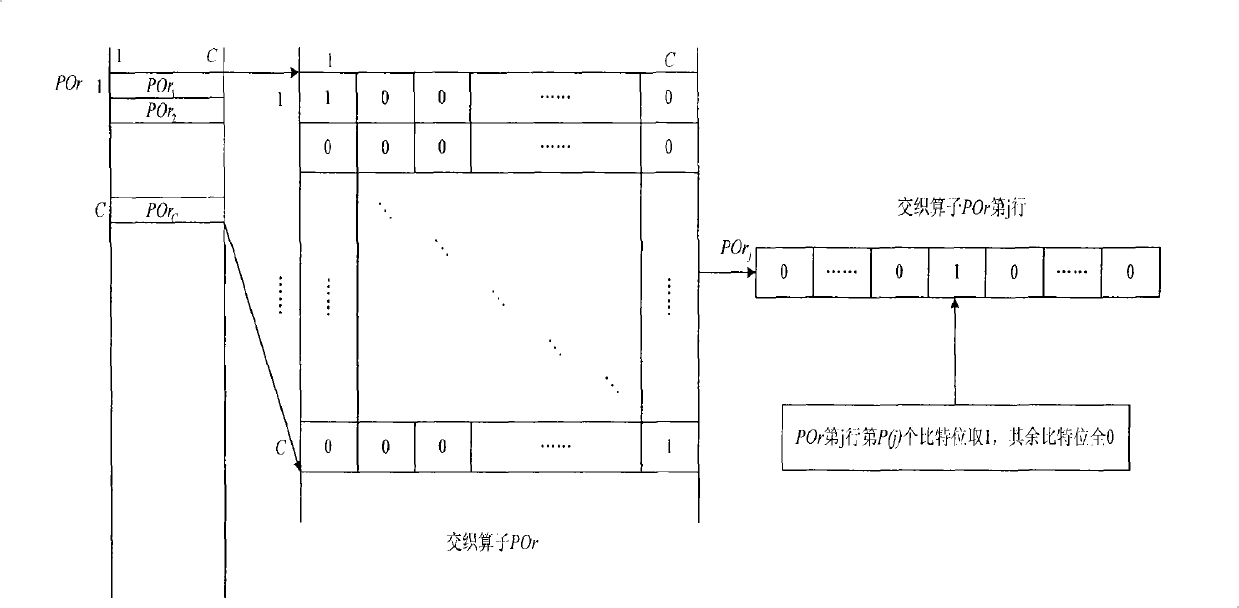

[0110] Step 101, generating an interleaving operator according to a column interleaving mode.

[0111] The specific method of generating the interleaving operator is as described above, that is, the interleaving operator POr is a C subblock TC ×C subblock TC Matrix, where the value of the jth row and column P(j) of POr is 1, and all other elements in the jth row are 0, and the values of j are 0, 1, ... C subblock TC .

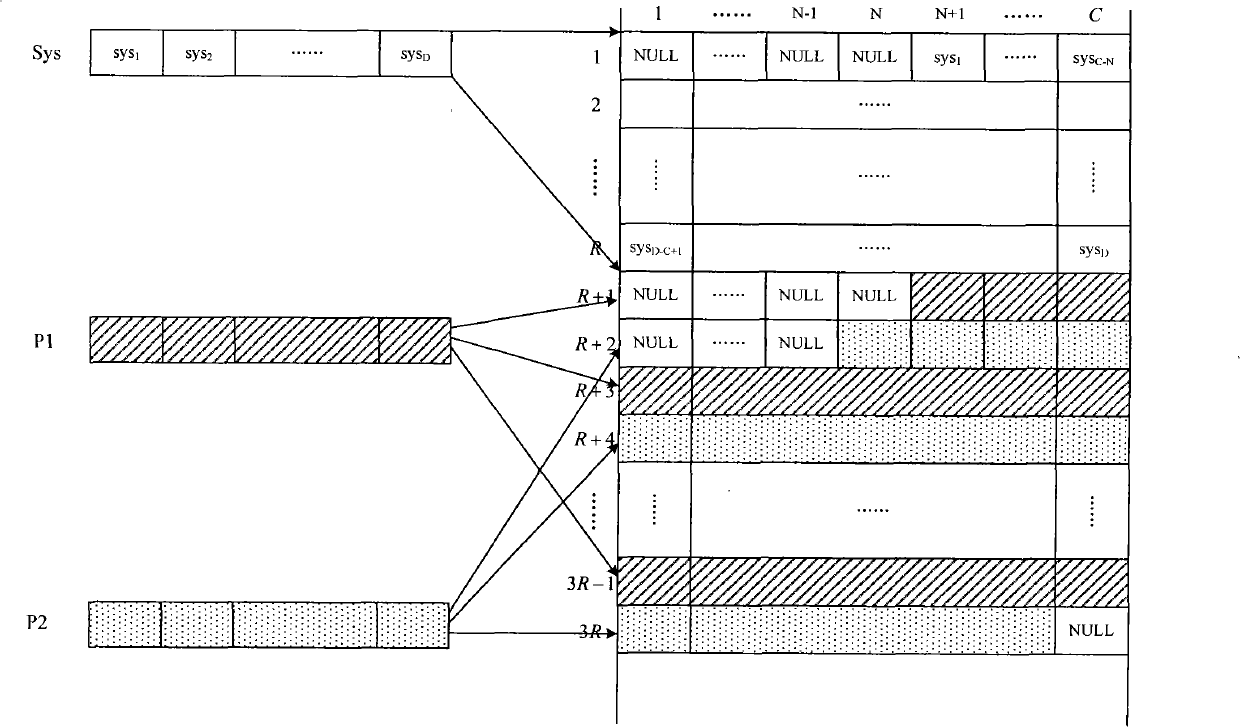

[0112] Step 102, wri...

Embodiment 2

[0176] In this embodiment, the padding bits of the sub-block interleaving matrix are directly determined according to the encoding parameters, and the mask matrix is no longer needed, further saving the buffer. At the same time, when using the interleaving operator to perform sub-block interleaving processing, all bits are interleaved and output to the circular buffer in the manner specified in the protocol, and then output from the circular buffer according to the redundancy version number to meet the rate matching The number of bits requested.

[0177] Specifically, the flow of the rate matching method in this embodiment includes:

[0178] Step 301, generating an interleaving operator according to a column interleaving mode.

[0179] Step 302, write the encoded output bit stream into the information sub-block interleaving matrix and each syndrome sub-block interleaving matrix, perform bit filling, and arrange all sub-block interleaving matrices according to the or...

Embodiment 3

[0209] In this embodiment, on the one hand, the filling bit position of the sub-block interleaving matrix is determined directly according to the encoding parameters, without introducing a mask matrix; on the other hand, when performing interleaving processing, only the bits to be output are Interleaving.

[0210] Specifically, the flow of the rate matching method in this embodiment includes:

[0211] Step 501, generate an interleaving operator according to the column interleaving mode.

[0212] The operation of this step is the same as the operation of step 101 in the first embodiment, and will not be repeated here.

[0213] Step 502, write the coded output bit stream into each sub-block interleaving matrix, perform bit stuffing, and arrange all sub-block interleaving matrices according to the system protocol.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More