FPGA-based H.264 video encoding end, decoding end, transmission device and transmission method

A video encoding and video encoder technology, applied in the field of FPGA image encoding and decoding, to achieve the effect of reducing resource consumption, reducing read and write operations, and reducing peak transmission bandwidth requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

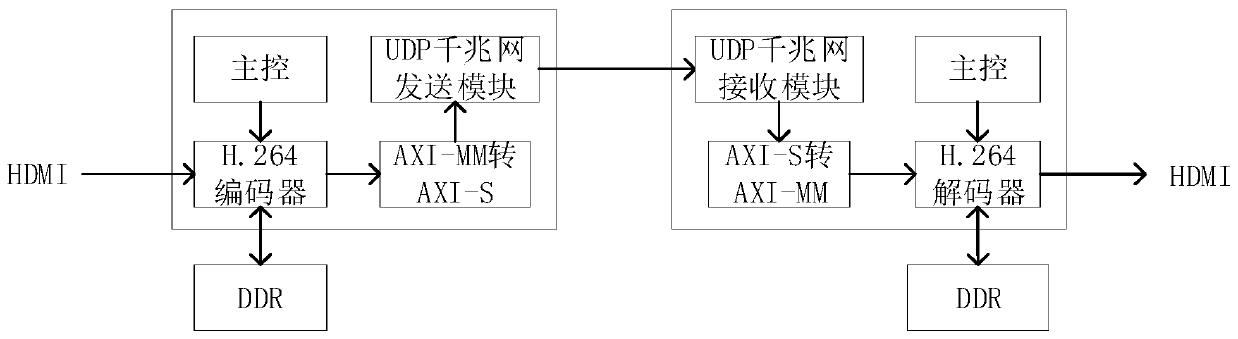

[0031] refer to figure 1 , this embodiment provides an FPGA-based H.264 video encoding end-to-decoding end device for real-time data transmission, including an FPGA-based H.264 video encoding end and an FPGA-based H.264 video decoding end.

[0032] The FPGA-based H.264 video coding end includes:

[0033] Encoder main control module, using MB (Microblaze) processor soft core or ARM processor hard core in FPGA to initialize H.264 video encoder, including configuring video size, encoding compression rate and other parameters, and controlling H.264 Video encoder for encoding.

[0034] The H.264 video encoder encodes the video data under the control of the main control module of the encoding end, and every time 128 bytes of encoded data is generated, it is sent to the AXI-MM to AXI-S module in real time.

[0035] Encoder DDR module, which writes / reads the read and write data of the H.264 video encoder to / from the encoder DDR.

[0036] The AXI-MM to AXI-S module converts the enco...

Embodiment 2

[0045] This embodiment provides a real-time data transmission method from an FPGA-based H.264 video encoding end to a decoding end, including:

[0046]The H.264 video encoder at the H.264 video encoding end receives the video data and starts encoding. Every time 128 bytes of encoded data are generated, it is sent to the AXI-MM to AXI-S module in real time, and the encoding is performed through the AXI-MM to AXI-S module. The data is sent to the UDP Ethernet sending module after interface and bit width conversion, and the UDP Ethernet sending module starts sending every 128 bytes of data.

[0047] The UDP Ethernet receiving module of the H.264 video decoding end receives the compressed code stream data packet and transmits it to the AXI-S to AXI-MM module for interface and bit width conversion, and then caches it in the RAM of the AXI-S to AXI-MM module. After the AXI-S to AXI-MM module detects the data frame header, it delays 3ms and sends a decoding start interrupt to the mai...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More