Patents

Literature

161 results about "Difference function" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

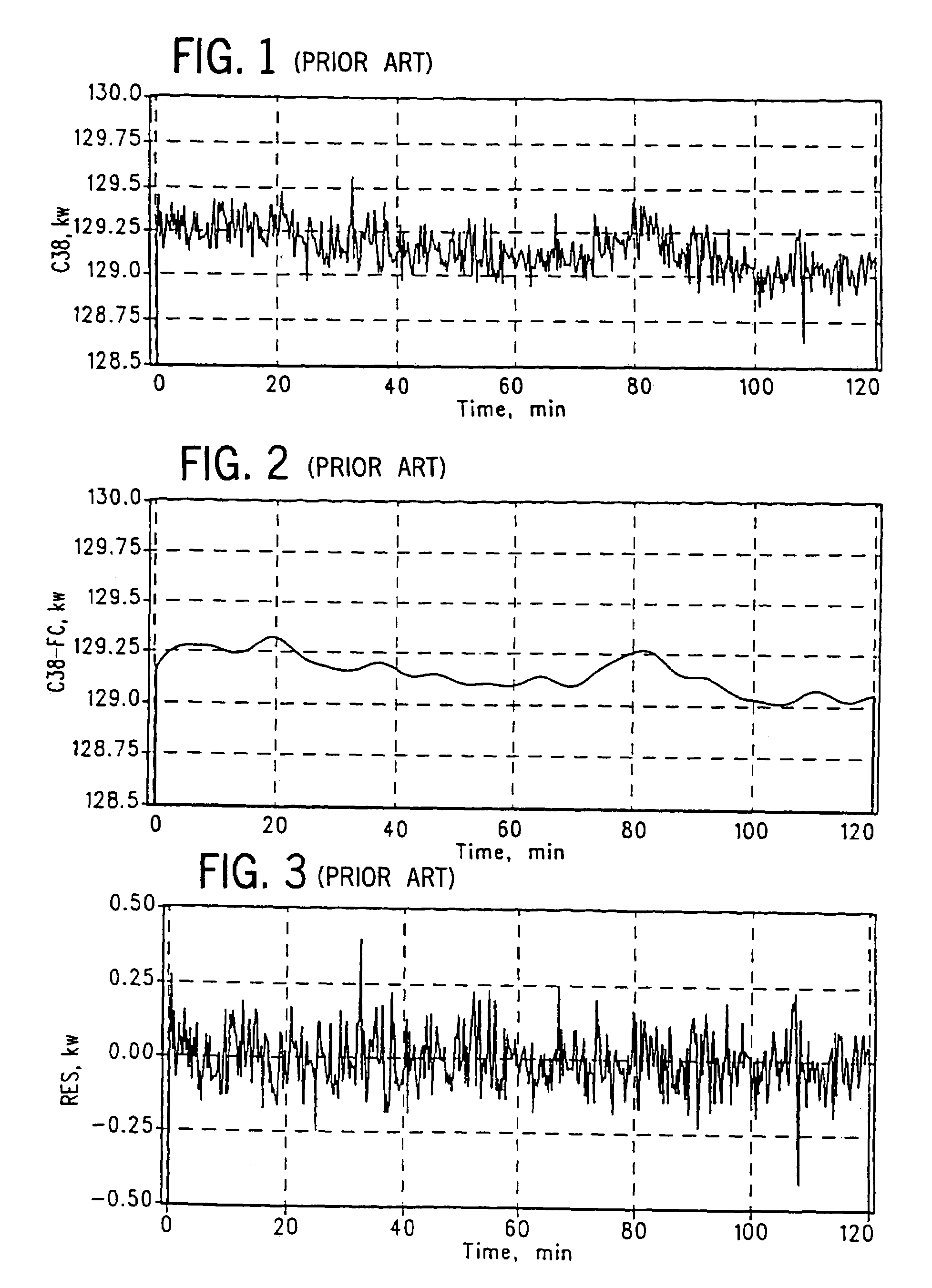

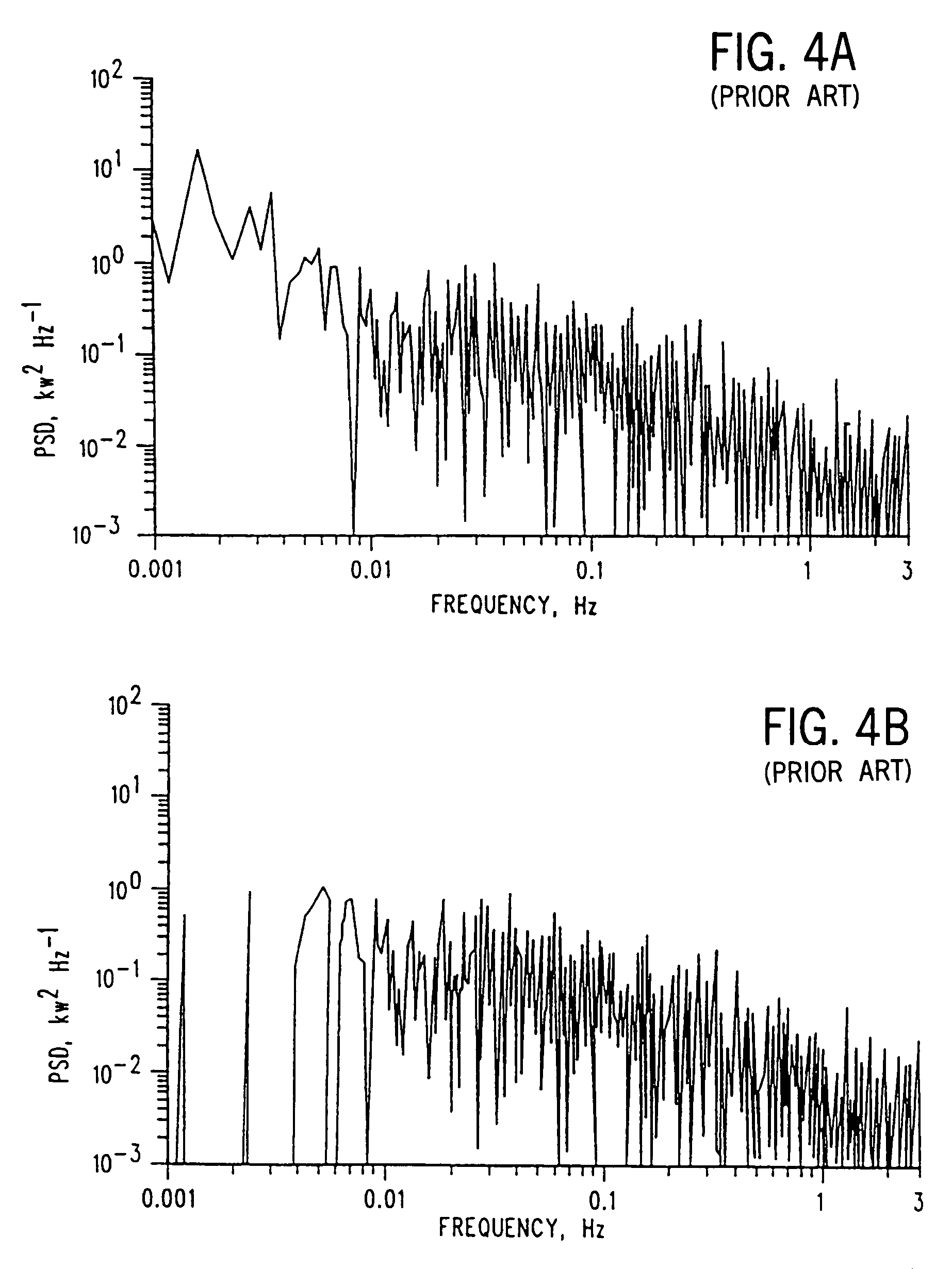

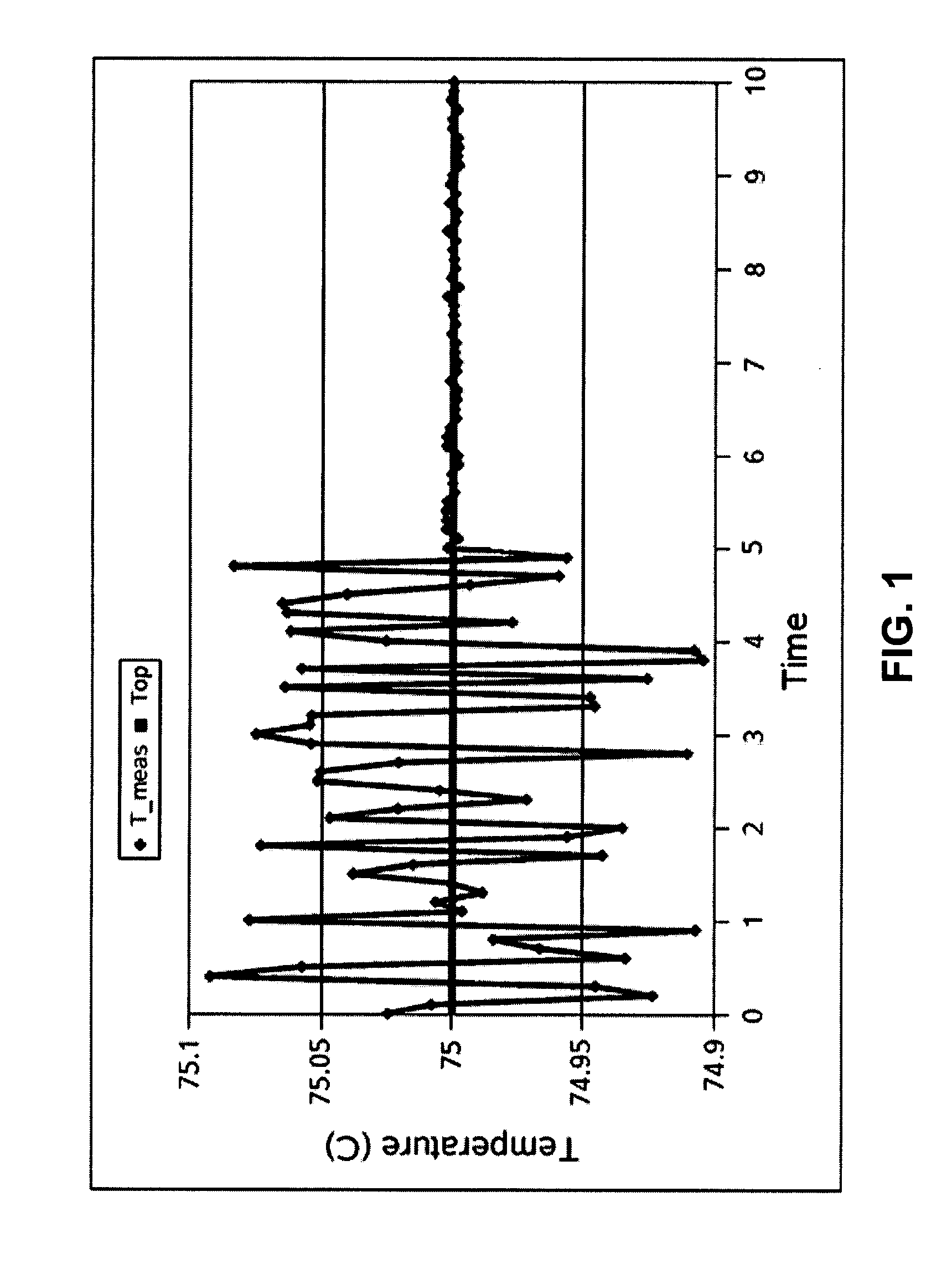

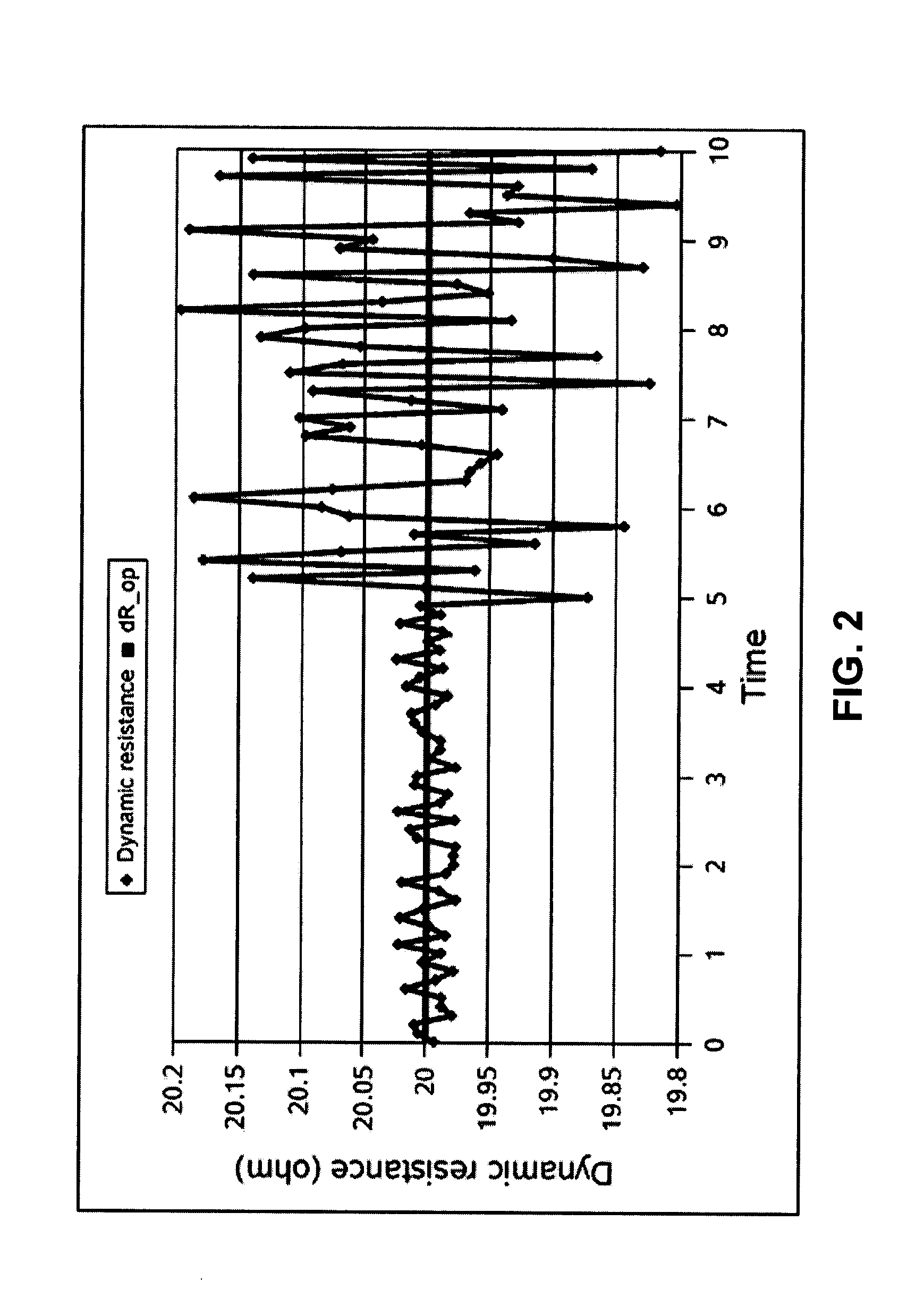

Monitoring and fault detection system and method using improved empirical model for range extrema

ActiveUS7373283B2High similarityComputation using non-denominational number representationComplex mathematical operationsData limitationsEngineering

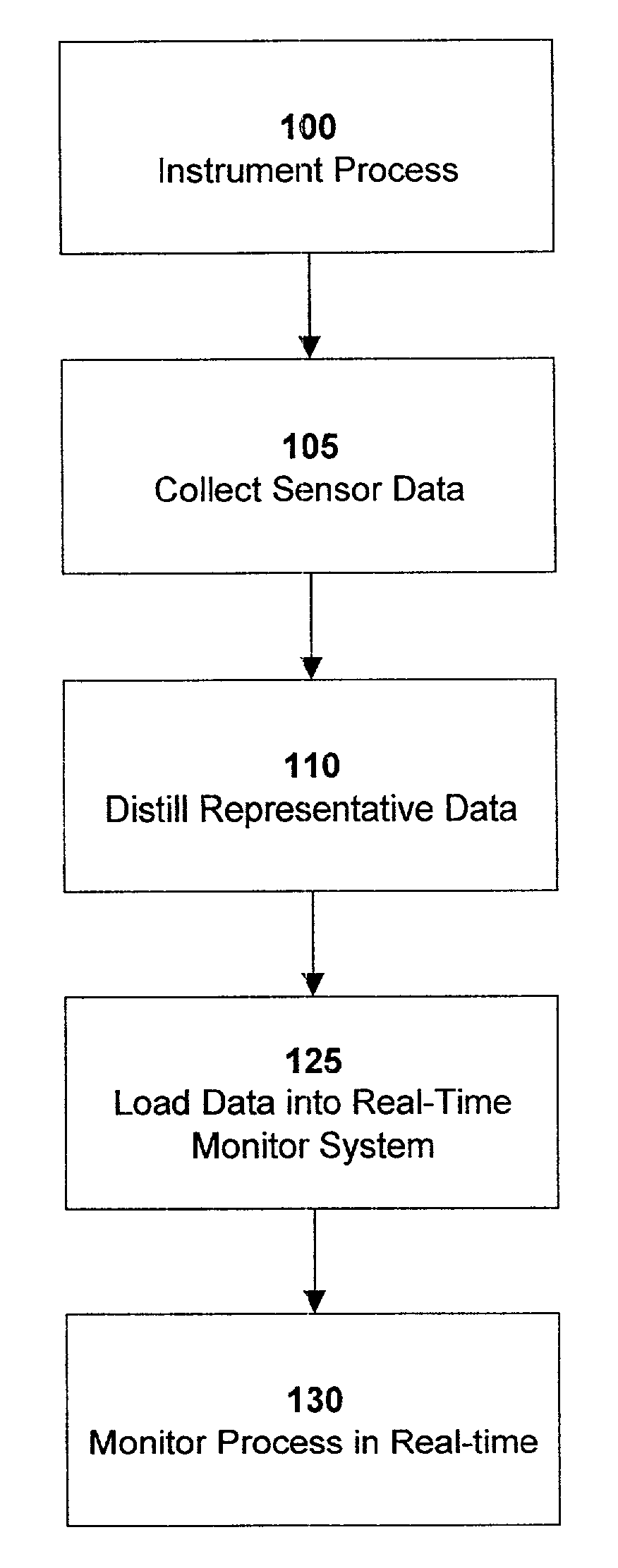

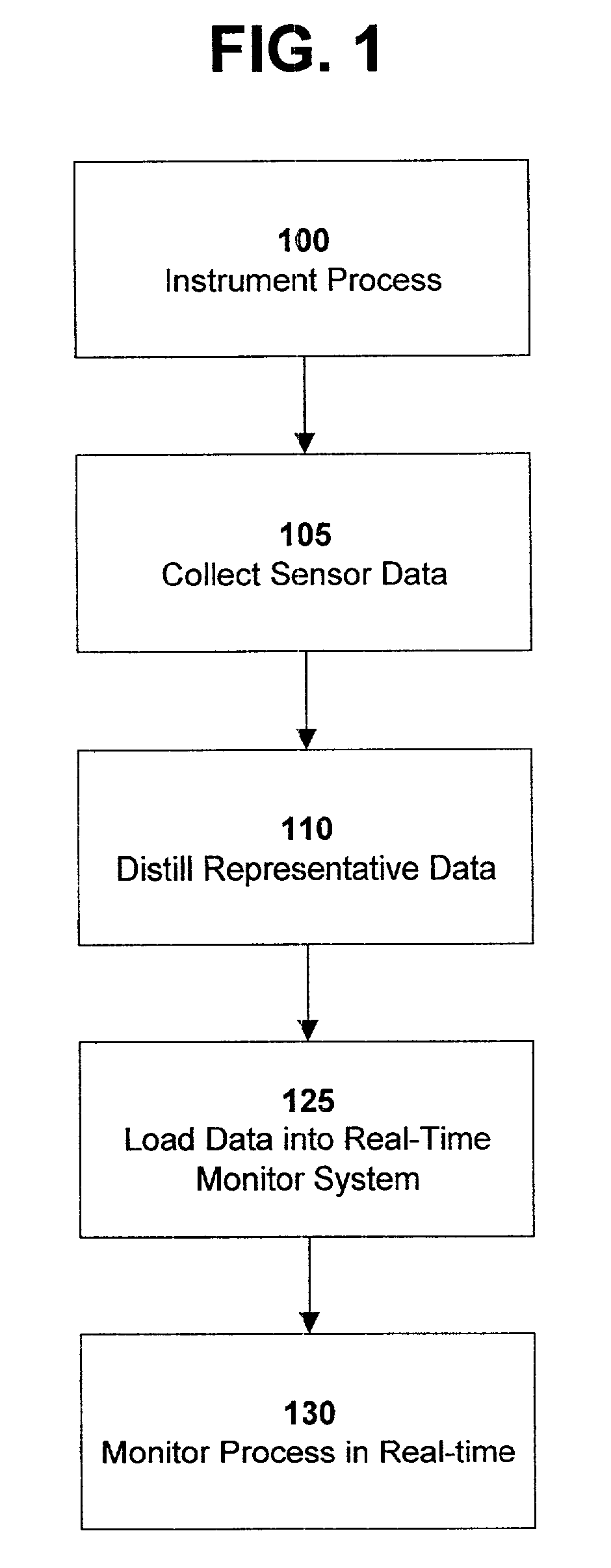

A method and apparatus for improved monitoring the operational state of instrumented systems is provided. An empirical model characterizes normal or desirable operation of the system, and real-time observations are provided to the model to generate estimates of expected sensor values. Comparison of the estimates with the real-time observations provides advanced warning of discrepancies in the operational state of the instrumented system. The invention provides for incipient failure detection, sensor failure detection and incipient process upset. An improved similarity operator provides for estimates that are not impaired by real-time observations at or beyond the limits of modeled data. The similarity operator comprises a difference function added to a constant, and the result is inverted.

Owner:SMARTSIGNAL CORP

Arc Fault Detection

ActiveUS20130226479A1Testing dielectric strengthEmergency protective arrangement detailsEngineeringDifference function

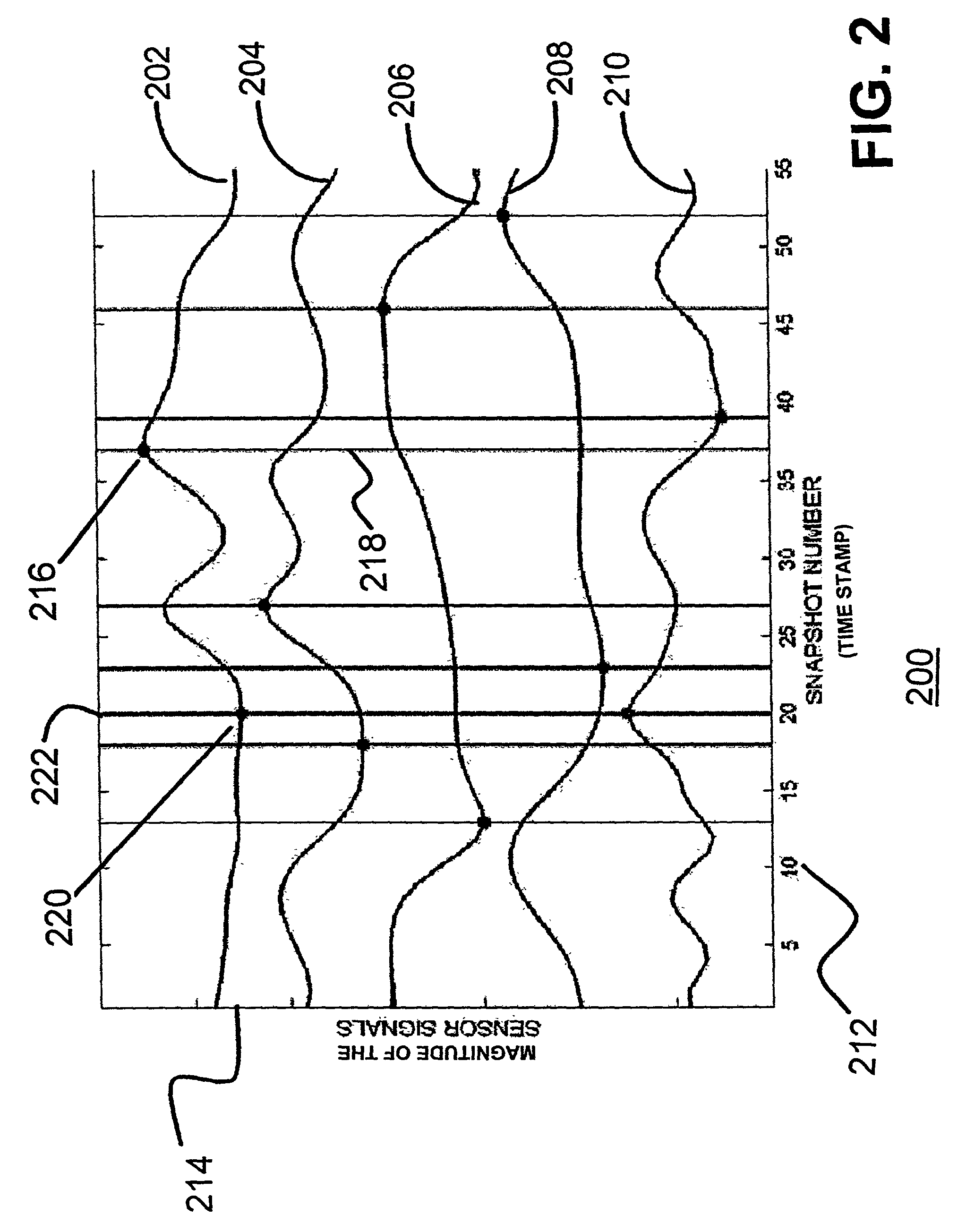

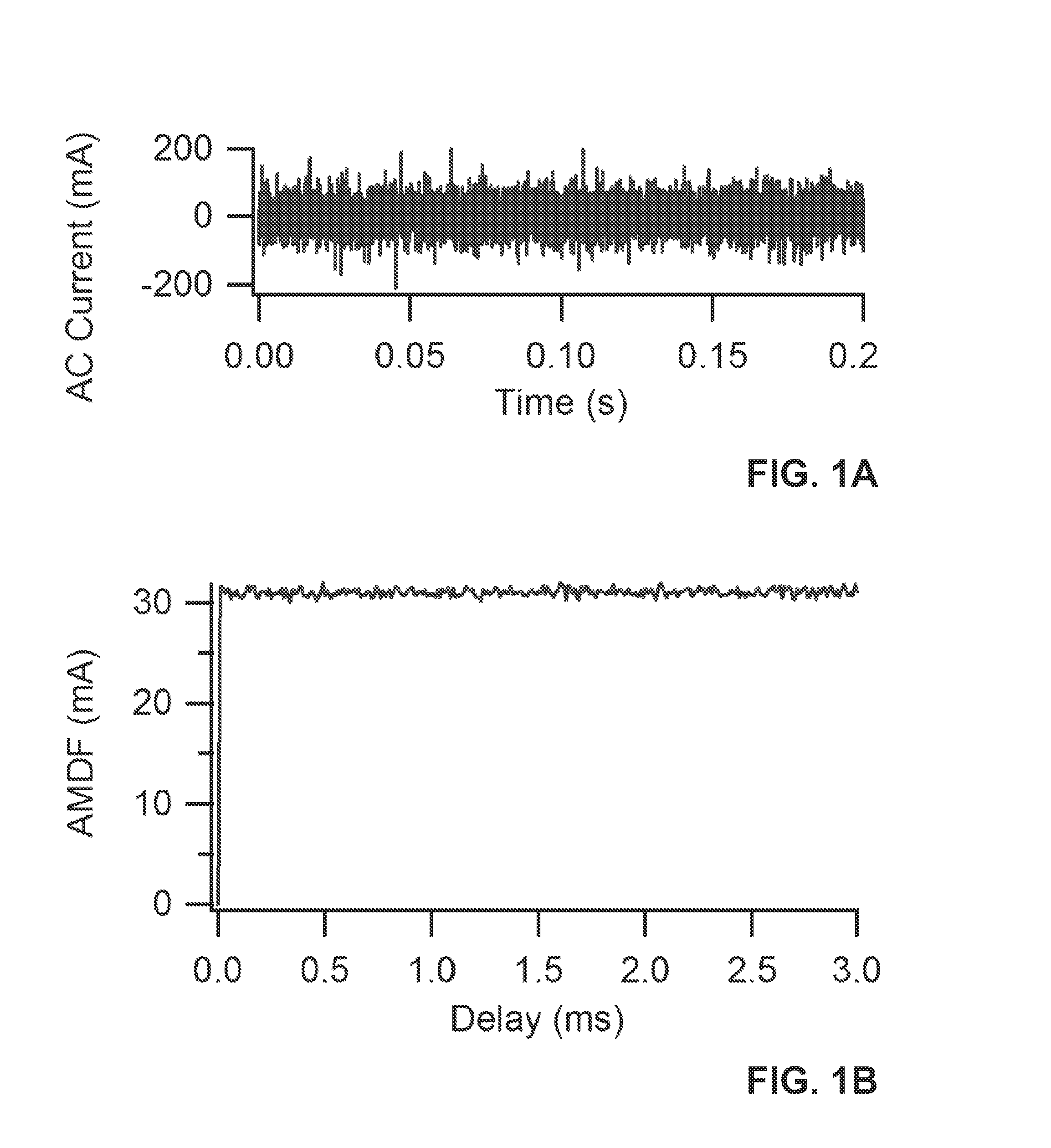

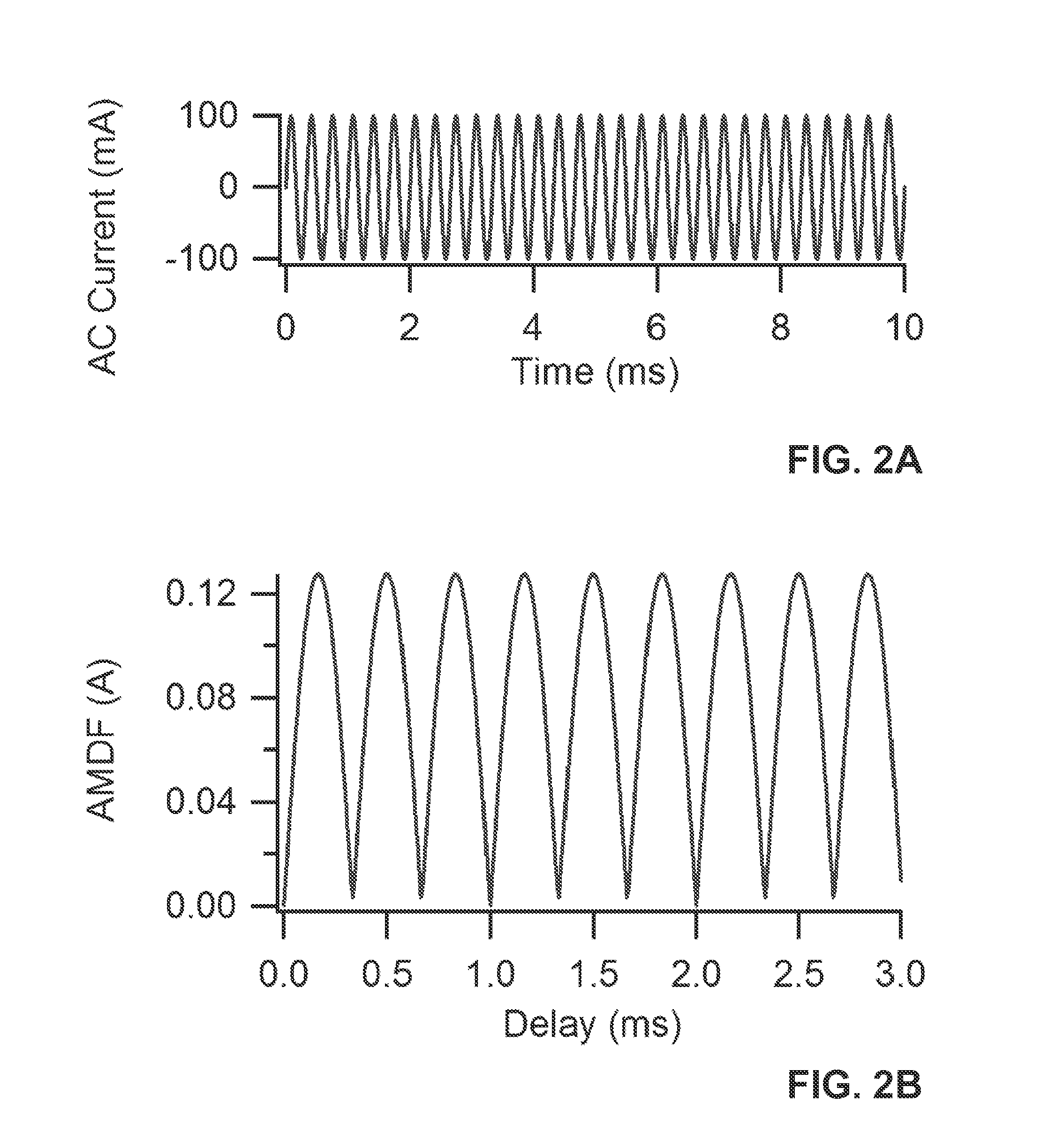

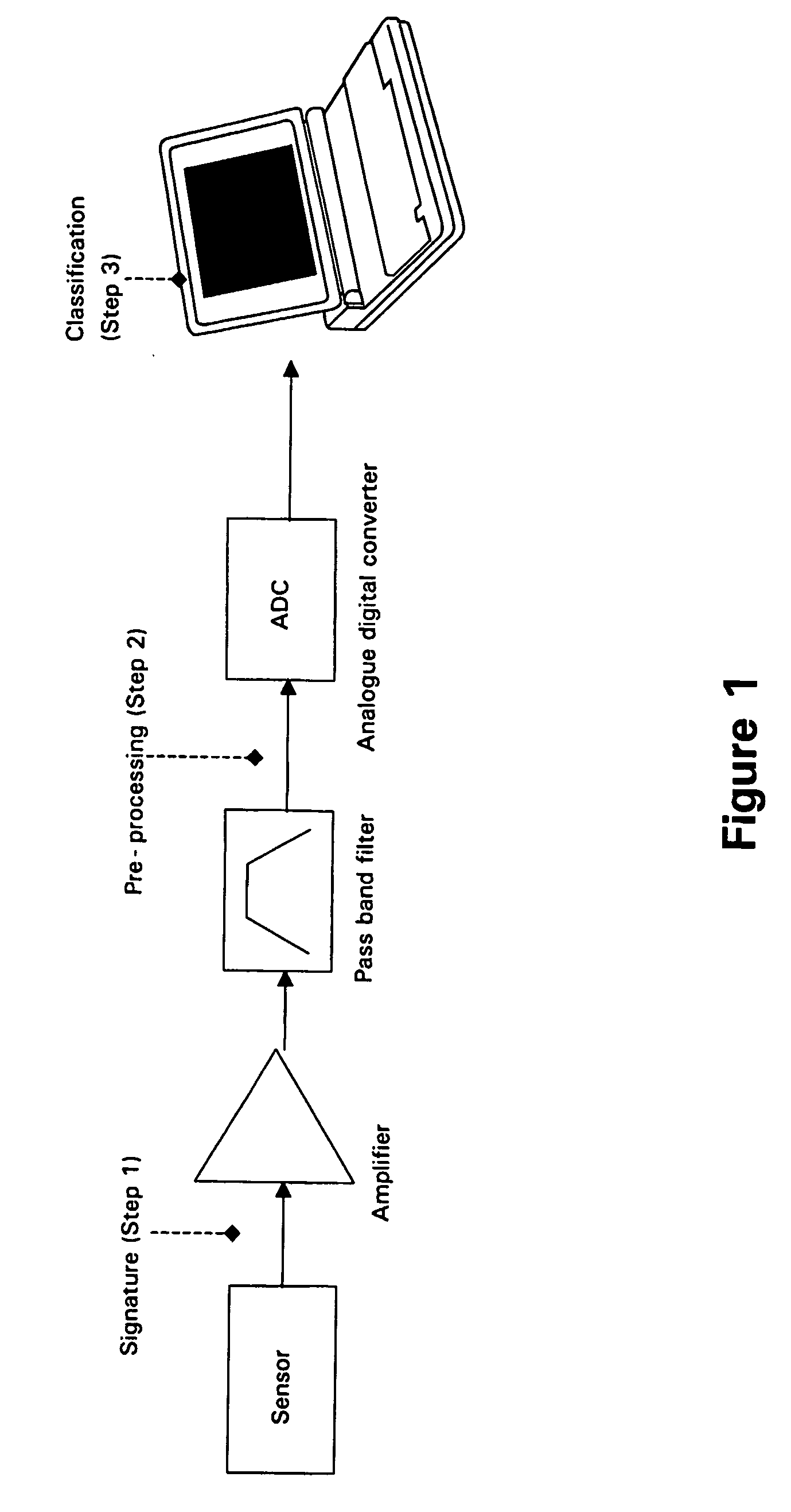

The present disclosure provides systems and methods for detecting arc faults. For some embodiments, arc faults are detected from waveforms that are acquired and processed, preferably using an Average Magnitude Difference Function (AMDF). The characteristics of the waveform provide an indication of whether or not an arcing fault occurred.

Owner:INNOVATIVE SCI SOLUTIONS

Data analysis system and method

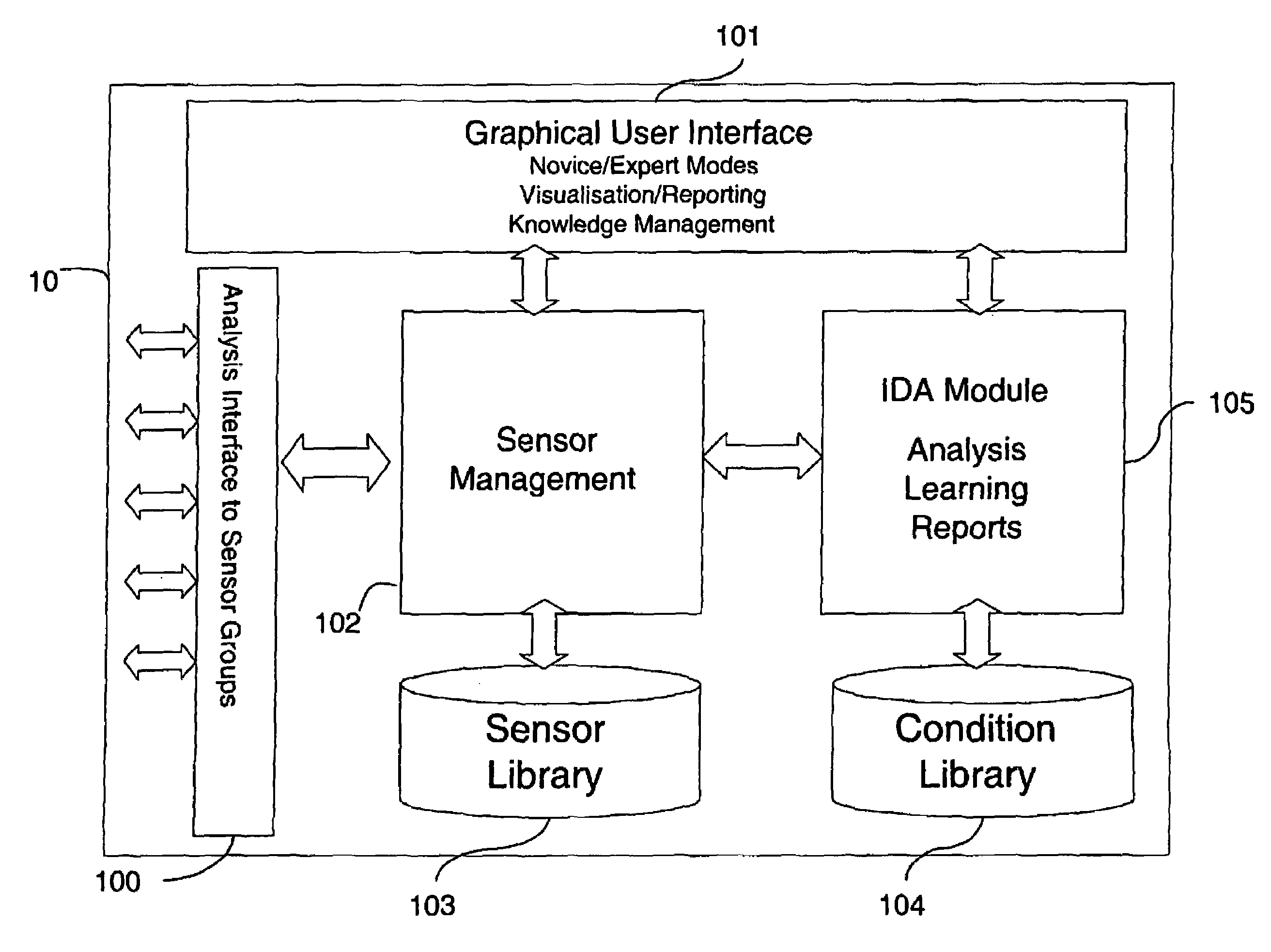

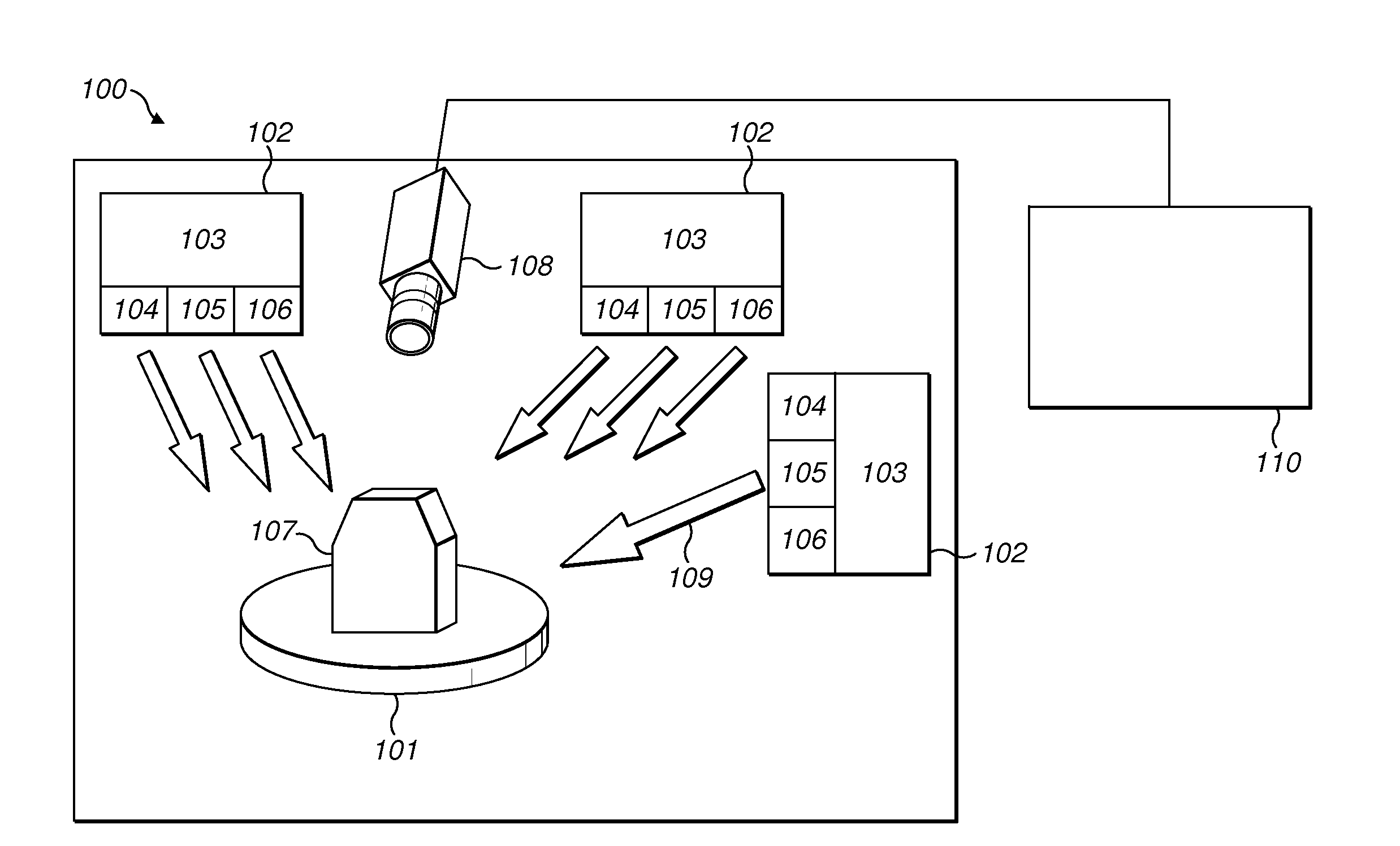

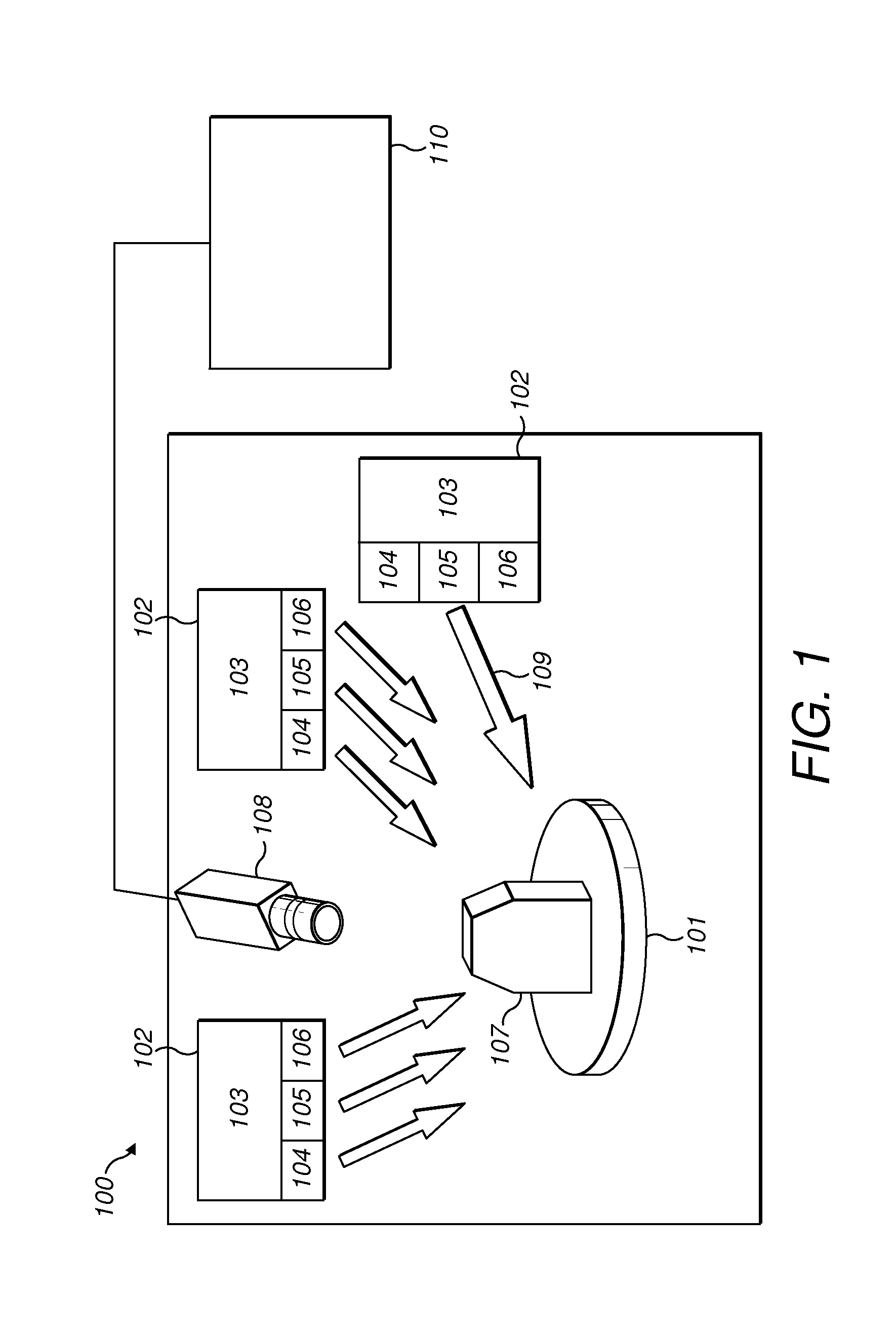

ActiveUS20060195201A1BuildImprove detection accuracyData processing applicationsSimulator controlDiscrepancy functionMonitoring system

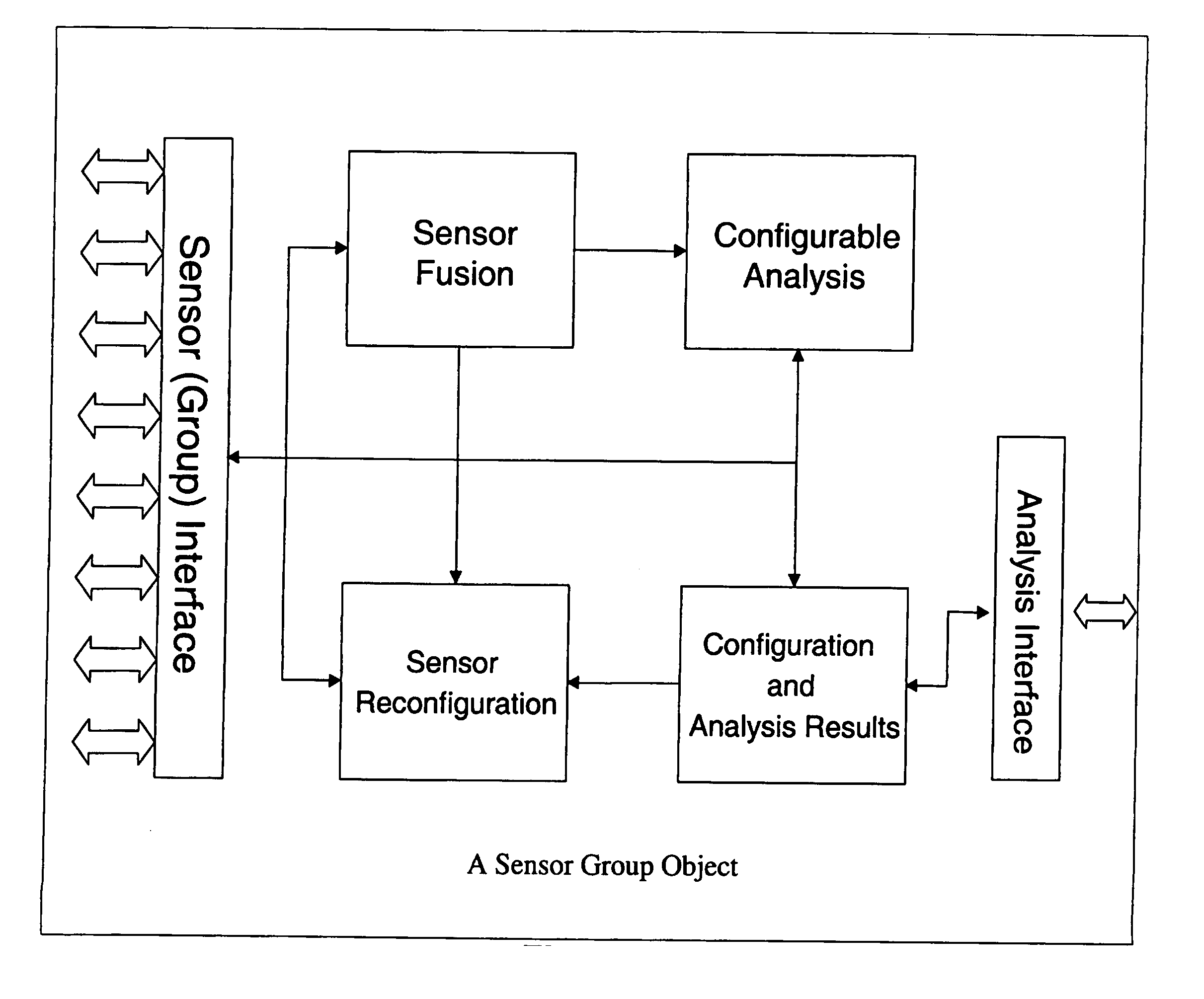

Methods and systems for analysing data from a monitoring system for monitoring characteristics of a dynamic system, said monitoring system providing characteristic data in respect of a dynamic system with at least one known normal state, the analysis system comprising: means (100) for receiving characteristic data from the monitoring system, means (101) for receiving confirmation information from an operator when the dynamic system is in a known normal state, normality modelling means (105) for deriving a normality model comprising data indicative of known normal states in response to received characteristic data and confirmation information, prediction generating means (105) for predicting future characteristic data from the normality model, difference function providing means (105) for providing a difference function indicating an acceptable difference between predicted and received characteristic data, and comparison means (105) for comparing predicted characteristic data with received characteristic data in conjunction with the difference function and producing an abnormality signal if the difference exceeds the difference function.

Owner:BRITISH TELECOMM PLC

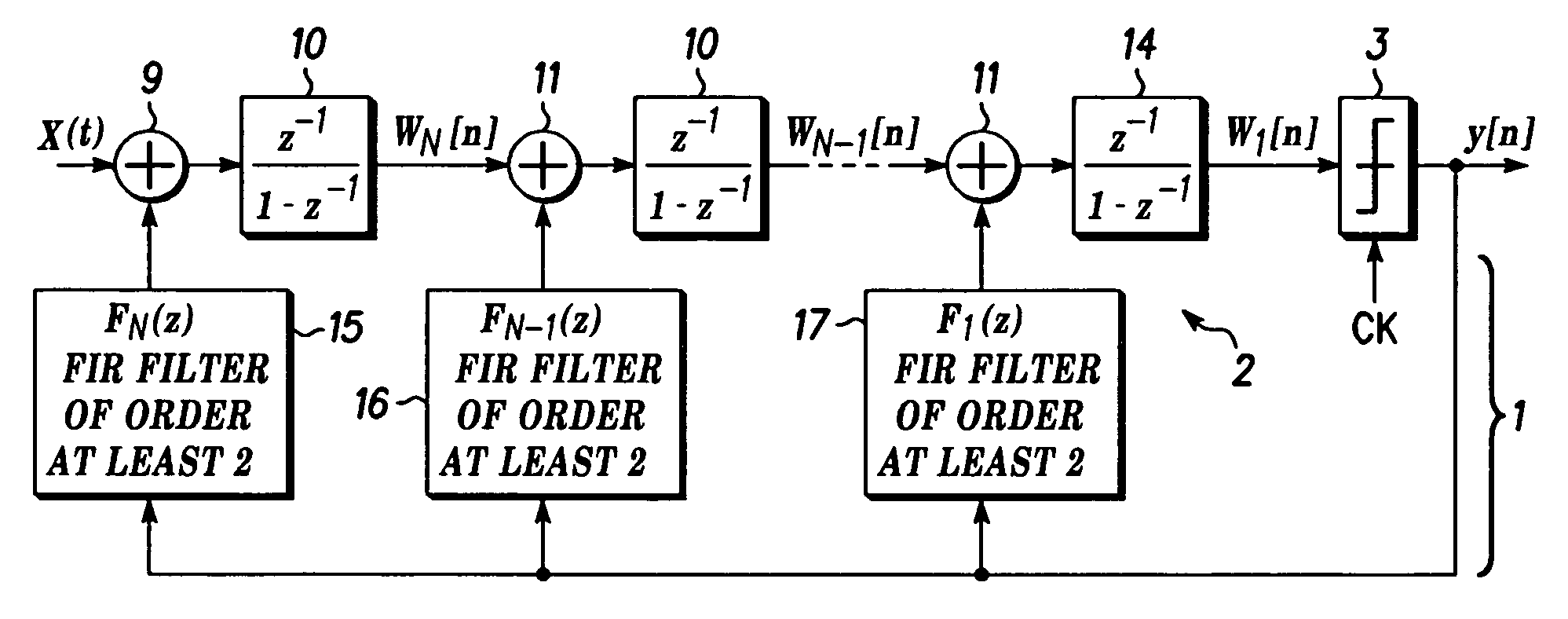

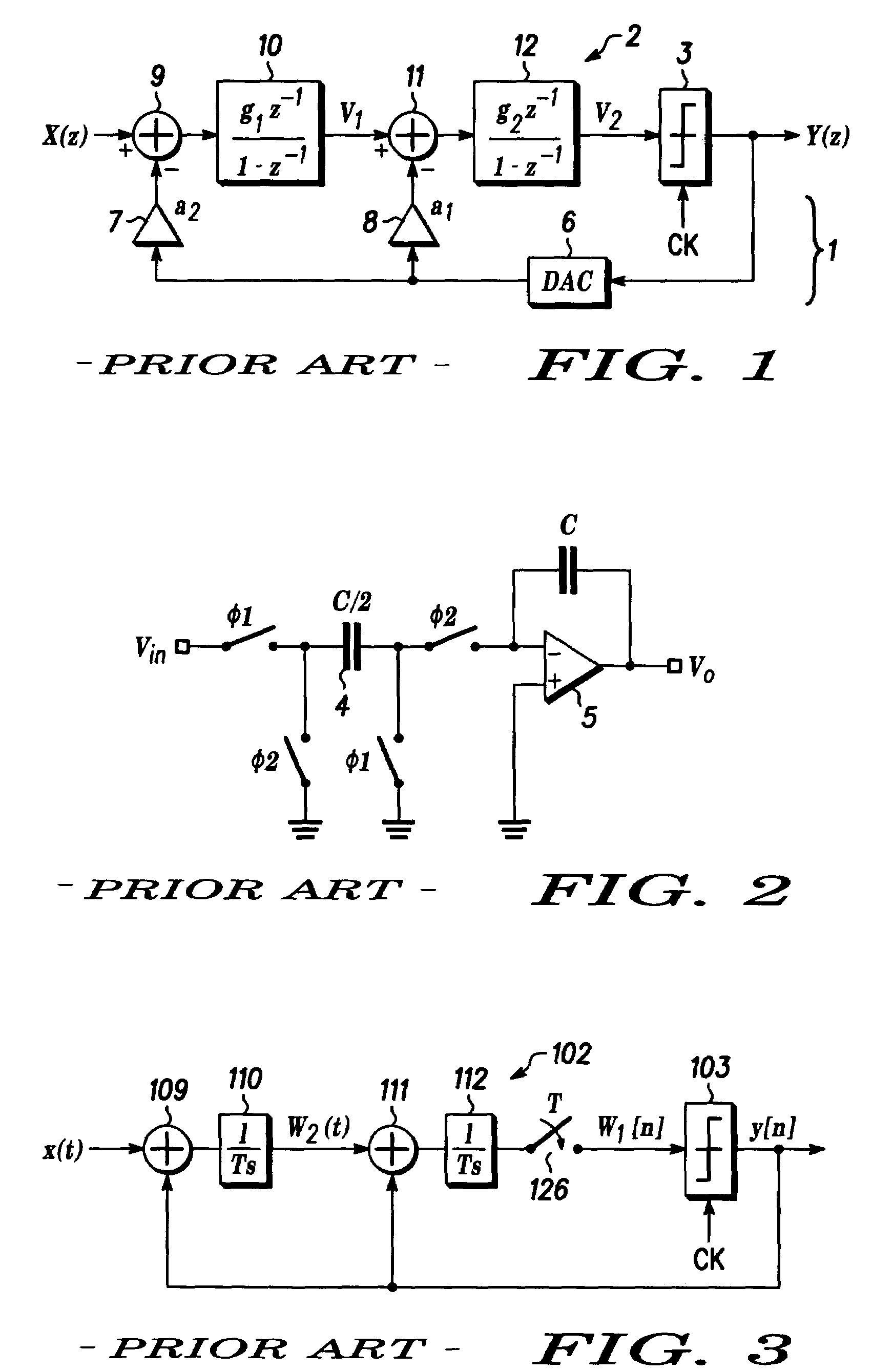

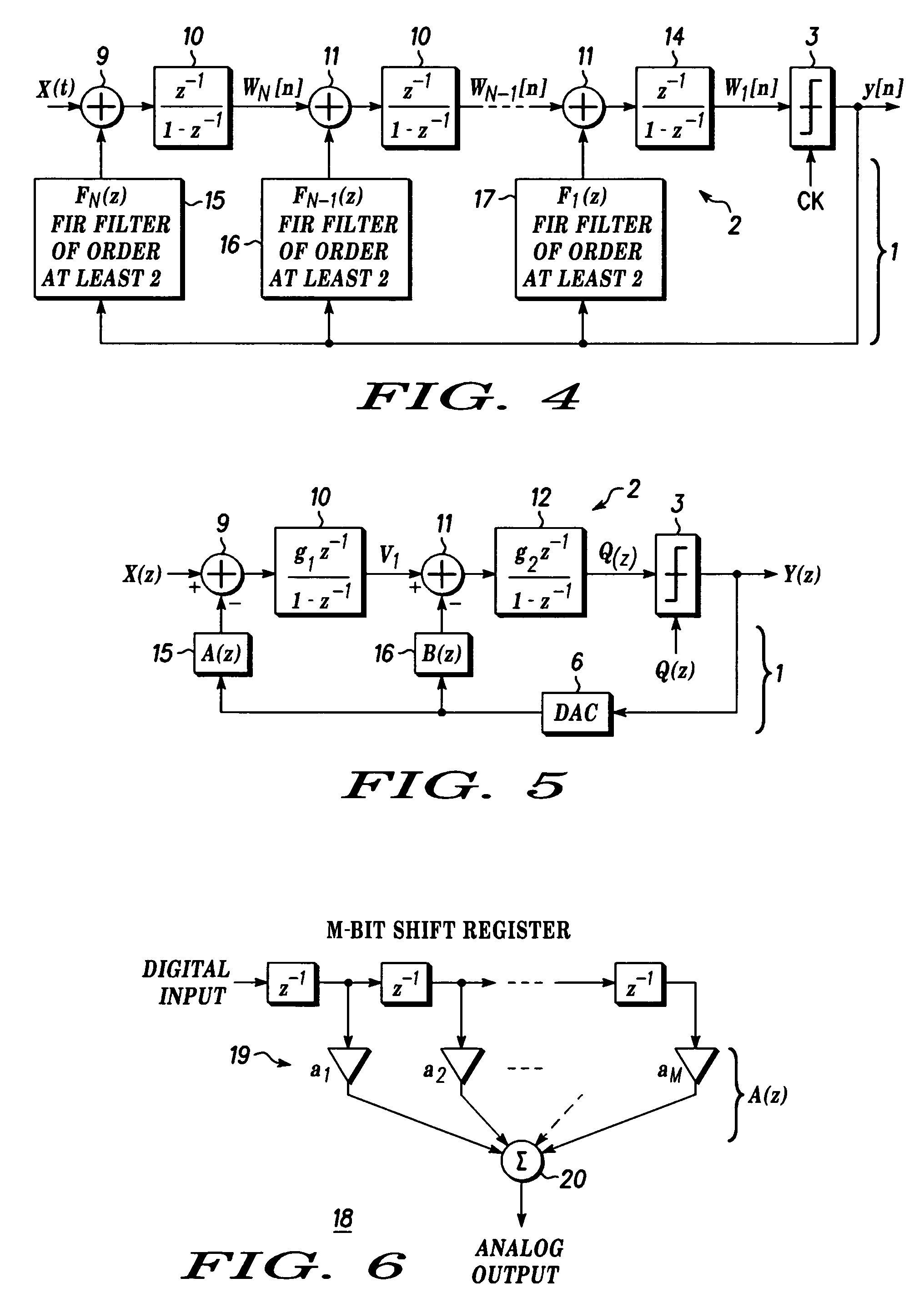

Analog-to-digital sigma-delta modulator with FIR filter feedback

InactiveUS7042377B2Electric signal transmission systemsDelta modulationFinite impulse responseIntegrator

Owner:NORTH STAR INNOVATIONS

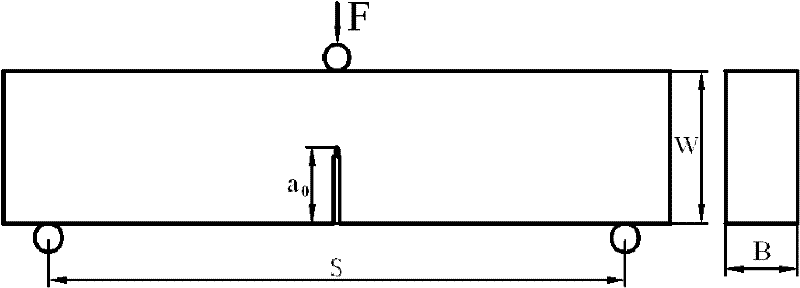

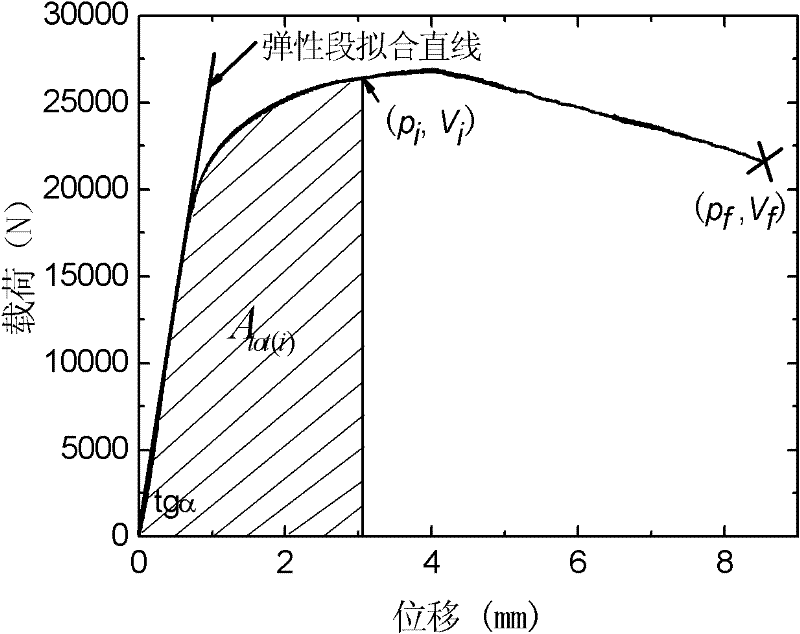

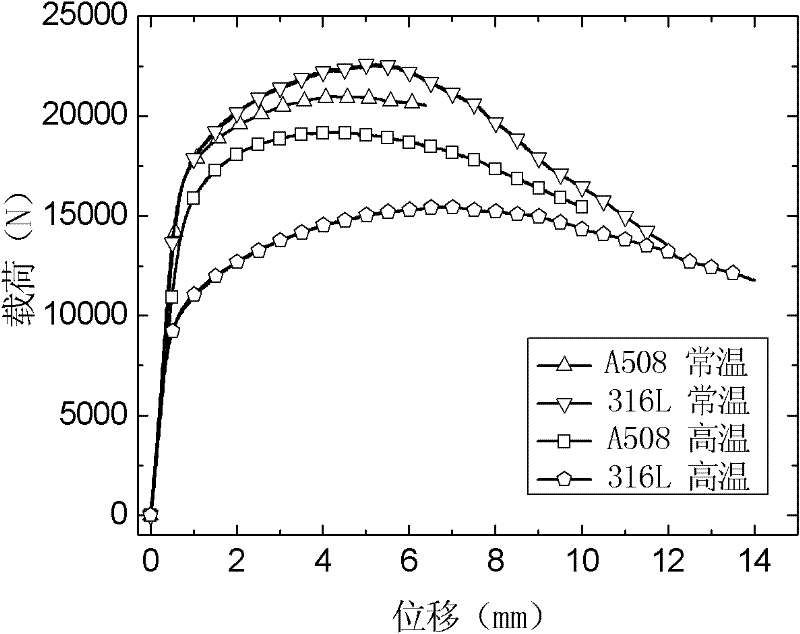

Test method for J-R resistance curve of high-toughness material

ActiveCN102353595AAvoid restrictionsMaterial strength using steady bending forcesMaterials testingLarge deformation

The invention relates to a test method for a J-R resistance curve of a high-toughness material. The method comprises the steps of sample processing, three point bending test, determination of crack length, calculation of J-integration at every load, establishment of a difference function, recursive calculation of crack length and p-V data pairs and construction of the J-R resistance curve. According to the invention, an extensometer is not employed for testing opening displacement and unloading flexibility of a crack mouth; instead, a testing machine is used for direct acquisition of deformation of a three point bending sample and a load-displacement curve in the whole process of fracture; then, the J-R resistance curve of the material is obtained through a series of calculation; therefore, the problem of restriction of testing apparatuses caused by large deformation of a sample in the testing of high-toughness materials is overcome, a J-R resistance curve in the situation of expandedlong size crack is measured, and the test method is applicable to measuring of J-R resistance curves of samples at different temperature and with different dimension.

Owner:EAST CHINA UNIV OF SCI & TECH

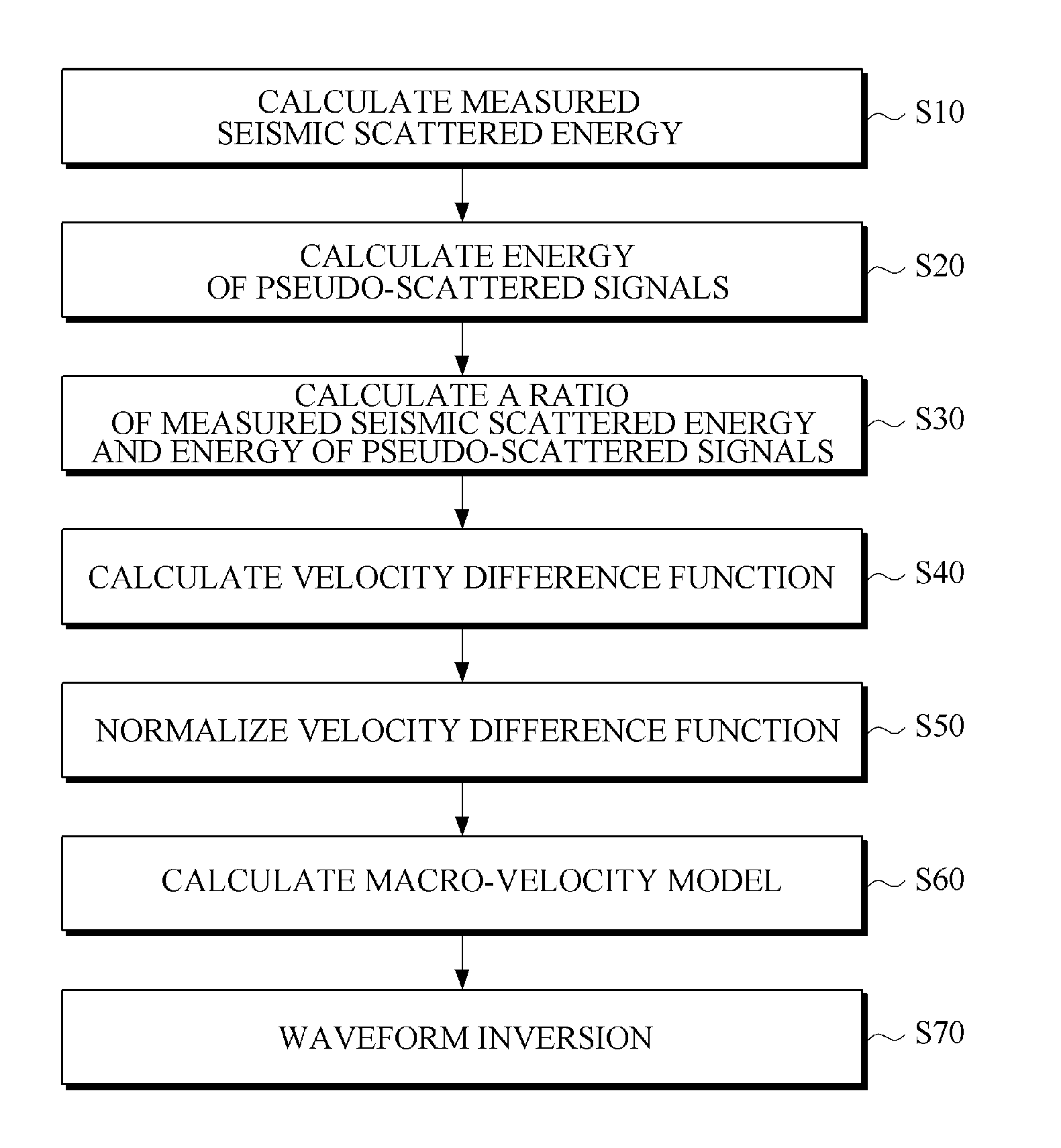

Seismic imaging apparatus utilizing macro-velocity model and method for the same

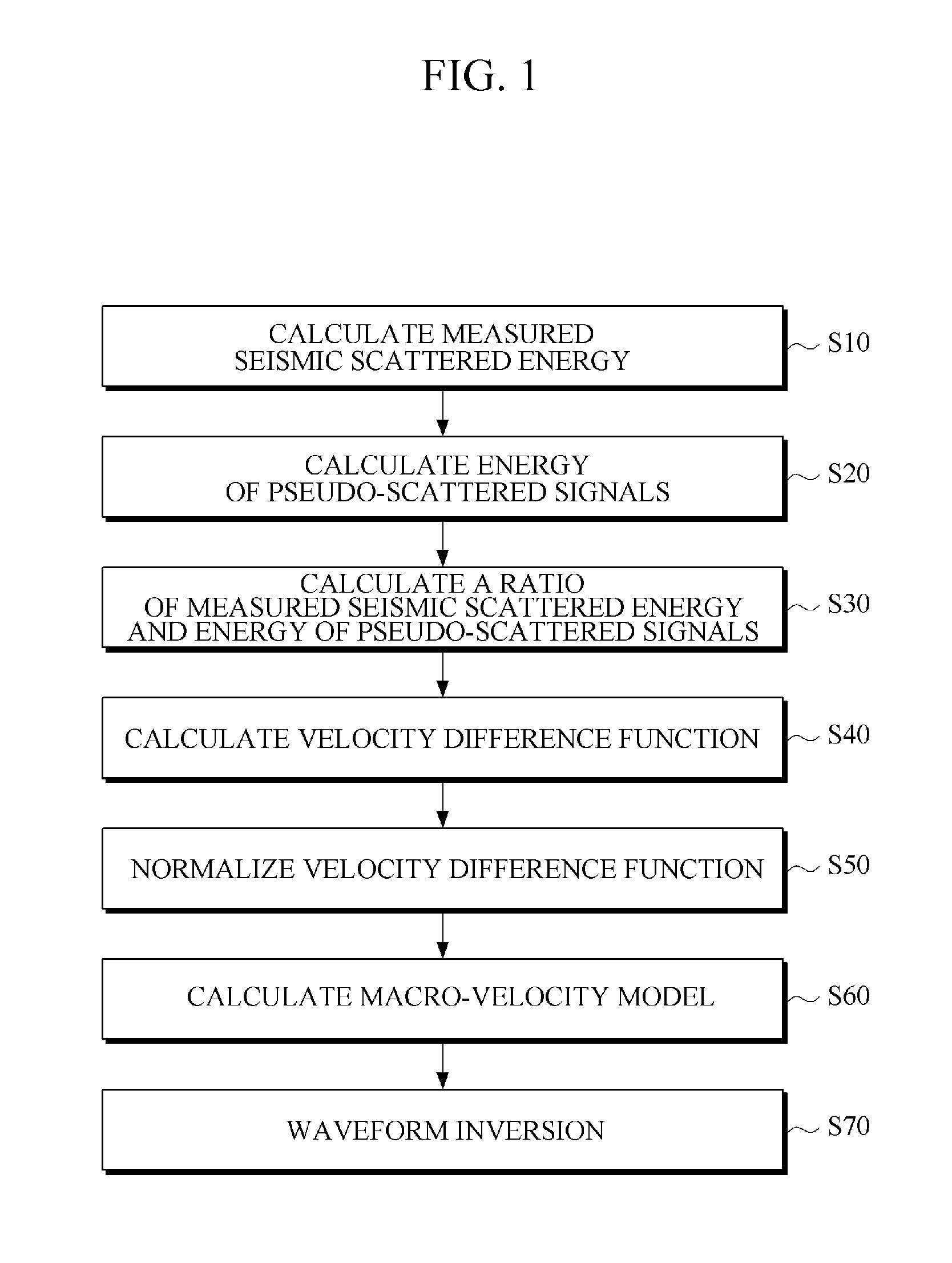

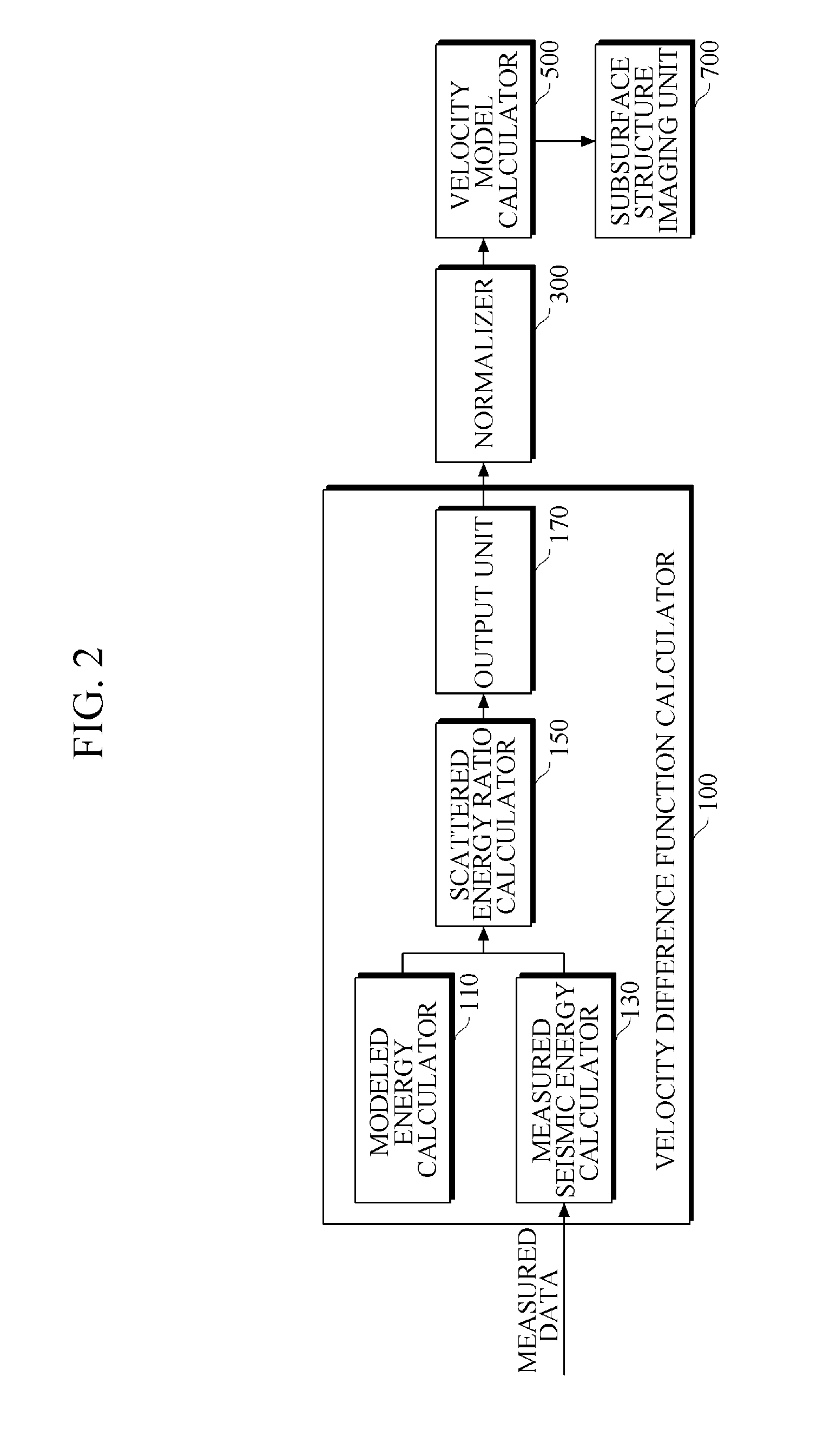

ActiveUS20120243373A1Reduce the amount of calculationHigh resolutionSeismic signal processingProcess MeasuresEnergy based

There is provided a seismic imaging technology for imaging a subsurface structure by processing measured data reflected from the subsurface structure after a wave from a source wave has been propagated to the subsurface structure. According to an aspect, there is provided a seismic imaging method for obtaining imaging data of a subsurface structure through waveform inversion using a macro-velocity model as an initial value, wherein the macro-velocity model which is used as the initial value for the waveform inversion is calculated by: calculating a velocity difference function which is a difference between a real velocity and an initial velocity model, wherein the velocity difference function is a ratio of measured seismic scattered energy and modeled scattered energy based on the initial velocity model; and calculating the macro-velocity model by updating the initial velocity model with the velocity difference function.

Owner:SEOUL NAT UNIV R&DB FOUND

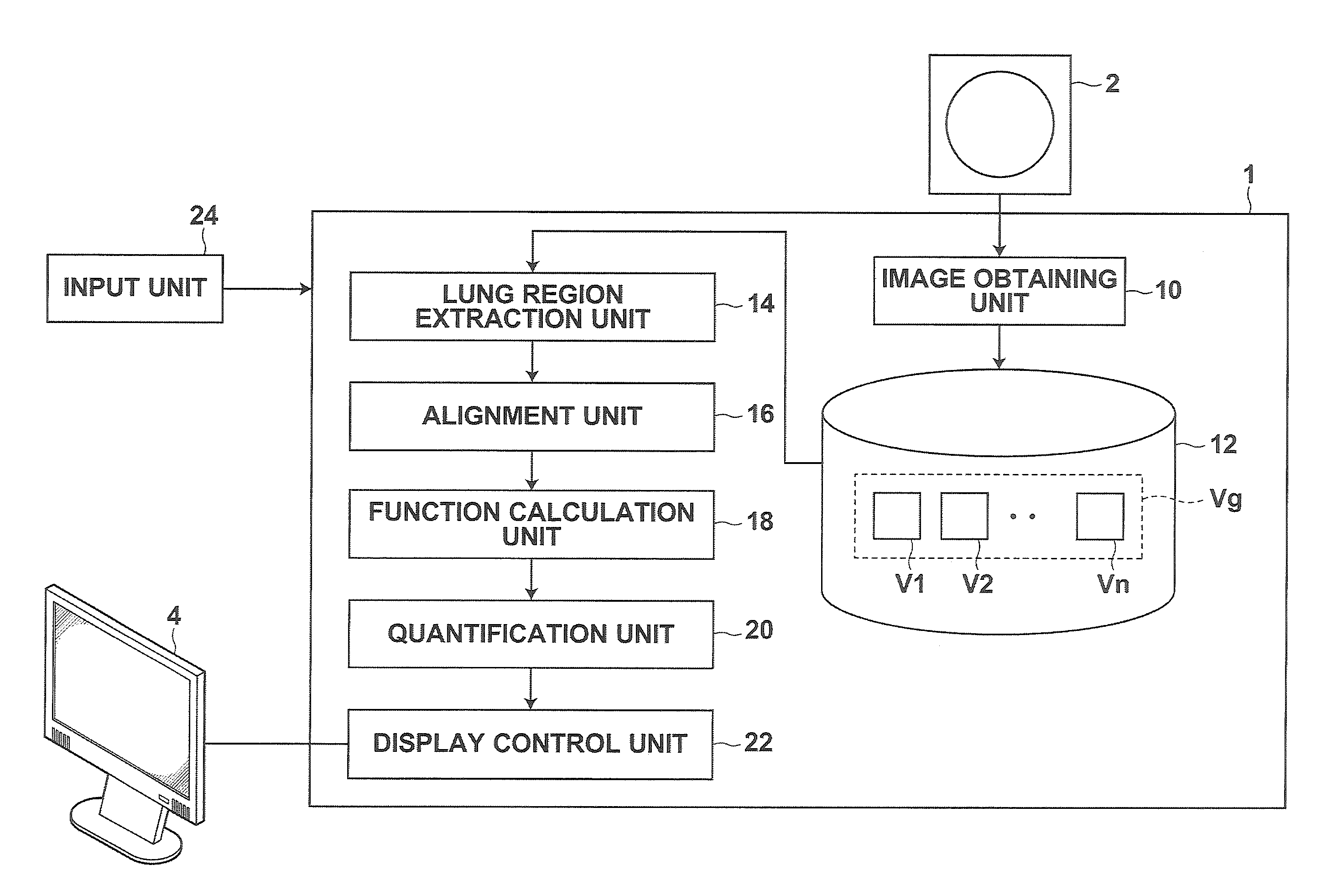

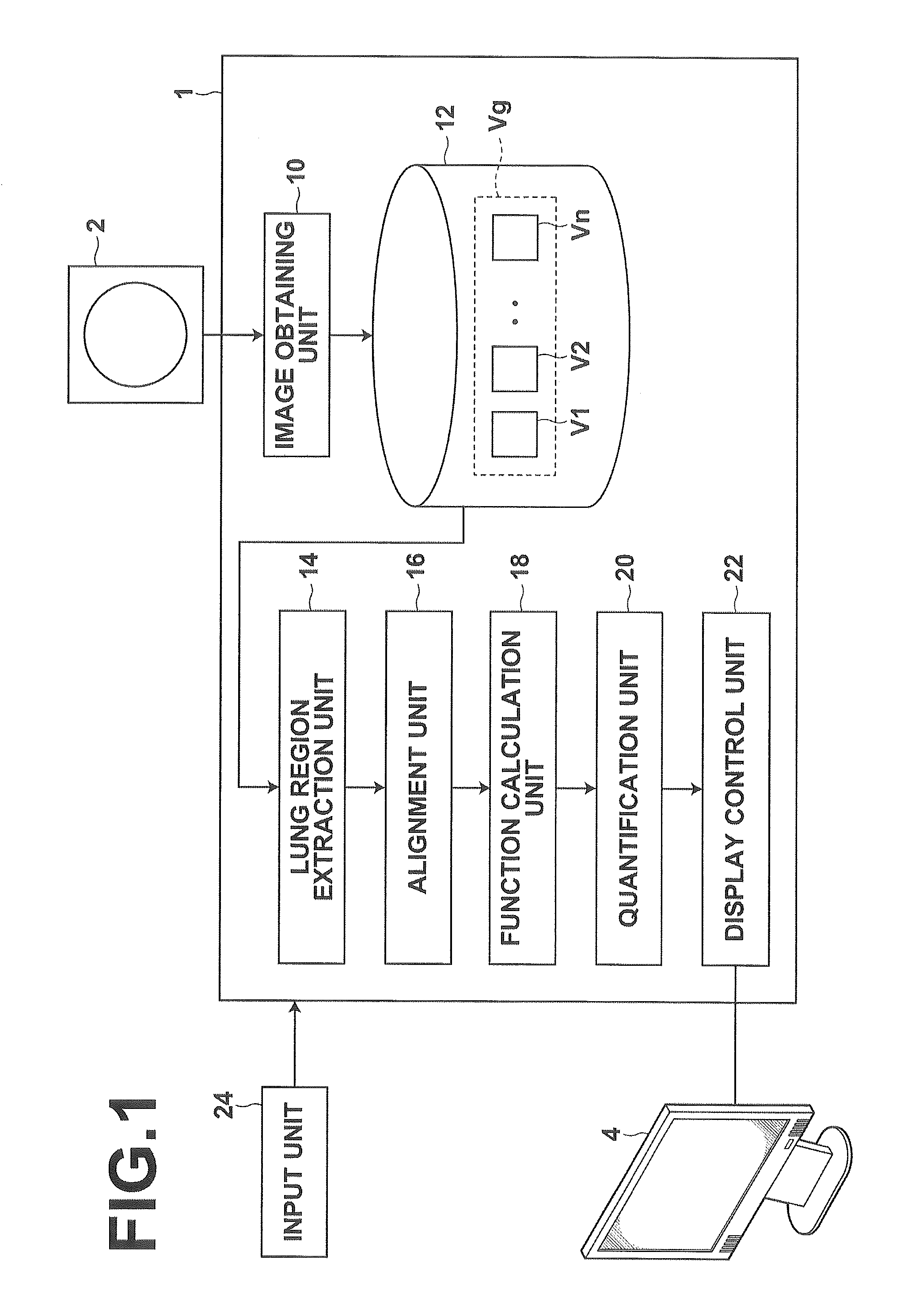

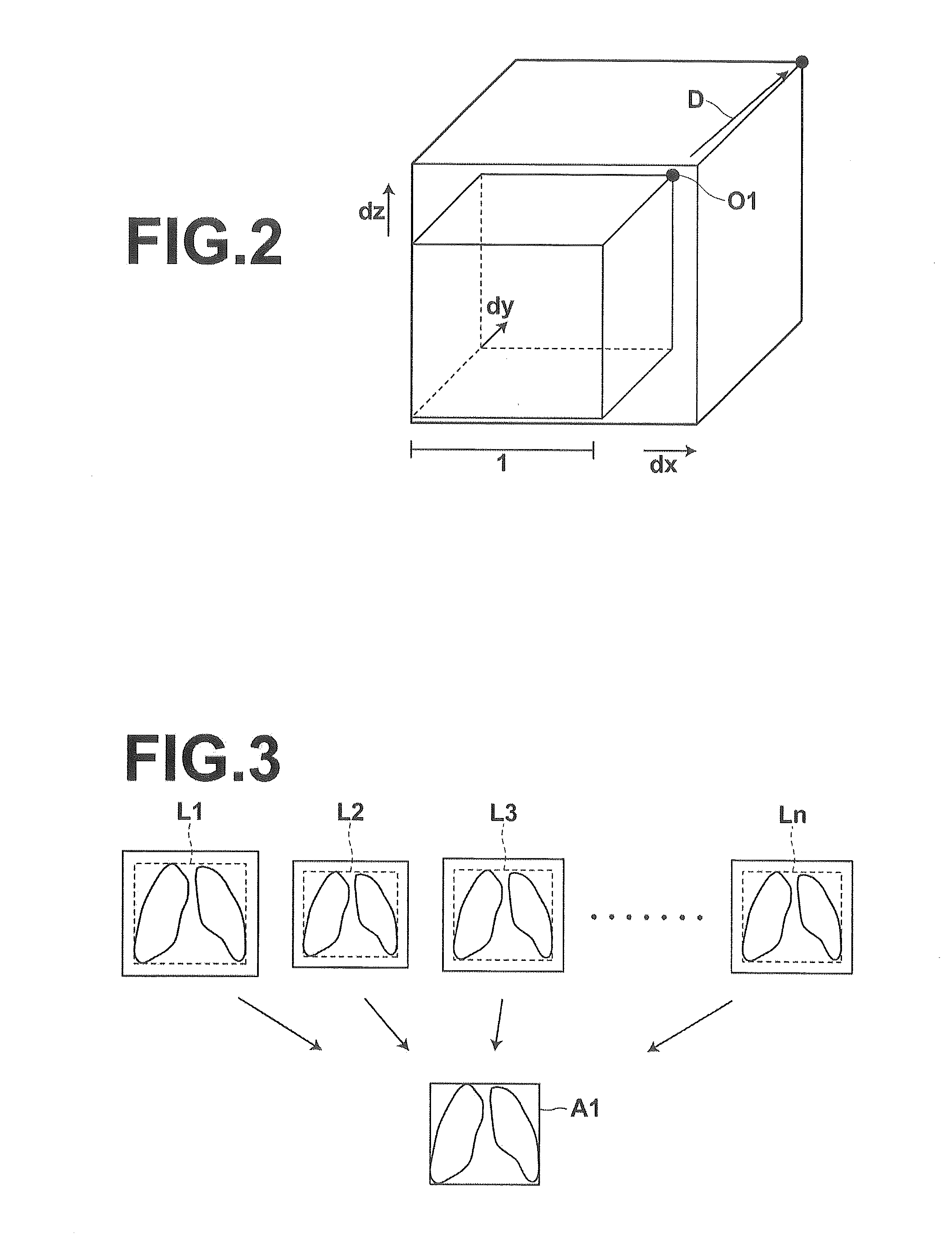

Image Analysis Apparatus, Method, and Program

ActiveUS20150005659A1Correct differenceImage enhancementImage analysisTemporal changeImaging analysis

The region extraction unit extracts lung regions from three-dimensional images of a plurality of time phases, the alignment unit aligns pixel position in the lung region extracted from each three-dimensional image between the three-dimensional images. This calculates a displacement vector field at each time phase of the three-dimensional images. The function generation unit calculates a local ventilation volume function representing a temporal change in ventilation volume at each point in the displacement vector field, and the quantification unit calculates a difference function, which is a function of difference values between the local ventilation volume function and benchmark ventilation volume function, as a quantitative value representing a difference between the local ventilation volume function and the benchmark ventilation volume function. The display control unit displays lung VR images on which the difference function is mapped on the display in time series order.

Owner:FUJIFILM CORP

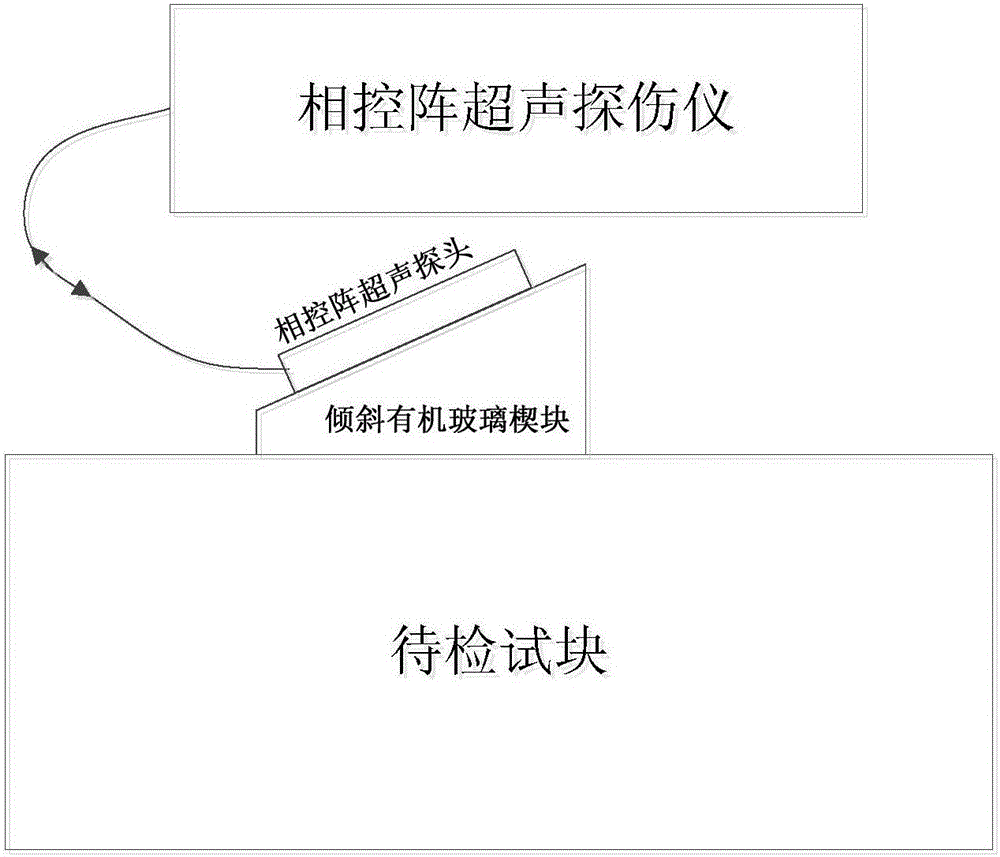

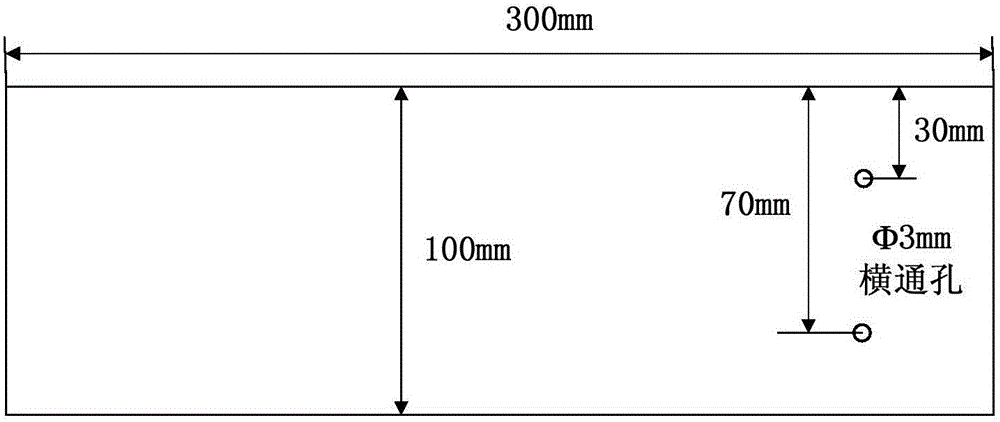

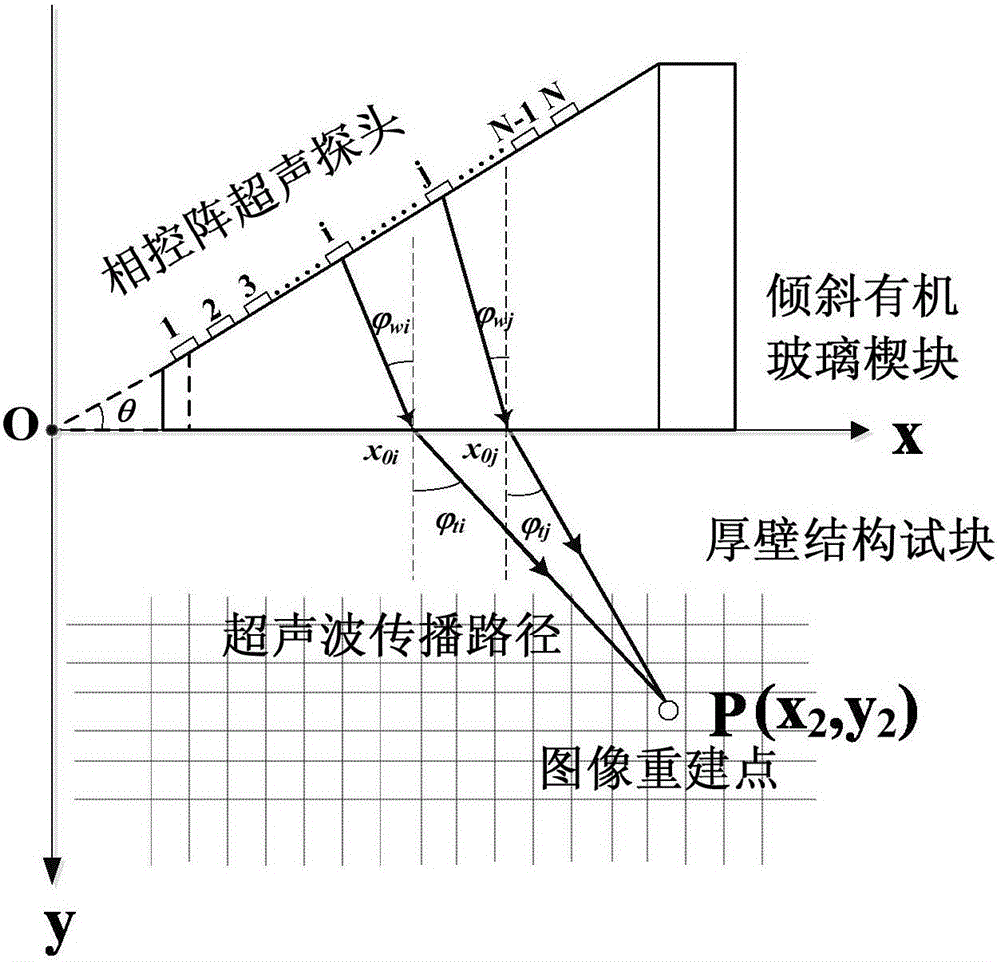

Oblique incident ultrasonic synthetic aperture focusing-based thick wall structure defect detection method

ActiveCN106093205ALarge energy coverageImprove defect detection efficiencyAnalysing solids using sonic/ultrasonic/infrasonic wavesUltrasonic attenuationThick wall

The invention discloses an oblique incident ultrasonic synthetic aperture focusing-based thick wall structure defect detection method, and belongs to the technical field of nondestructive detection. The method comprises the following steps: a thick wall structure test block is detected through using a phased array electron scanning function by using an ultrasonic detection system comprising a phased array ultrasonic flaw detector, a phased array ultrasonic probe and an oblique organic glass wedge in order to obtain the A scanning signal set of all phased array elements; the Fermat's theorem is used to solve the emission point positions of all the phased array elements and image reconstruction points in the wedge / test block interface, and all A scanning signals undergo time delaying and amplitude superposing processing; and the processed A scanning signals undergo Hilbert transformation, and a difference function is used to obtain a reconstructed ultrasonic detection B scanning image. The method has the advantages of high defect detection resolution, large detection range, detection efficiency increase, and provision of an effective solving technology for the nondestructive detection problem of the defect of a thick wall structure. The method also can be embedded to the flaw detector to realize automatic real-time imaging, and has high engineering application values.

Owner:DALIAN UNIV OF TECH

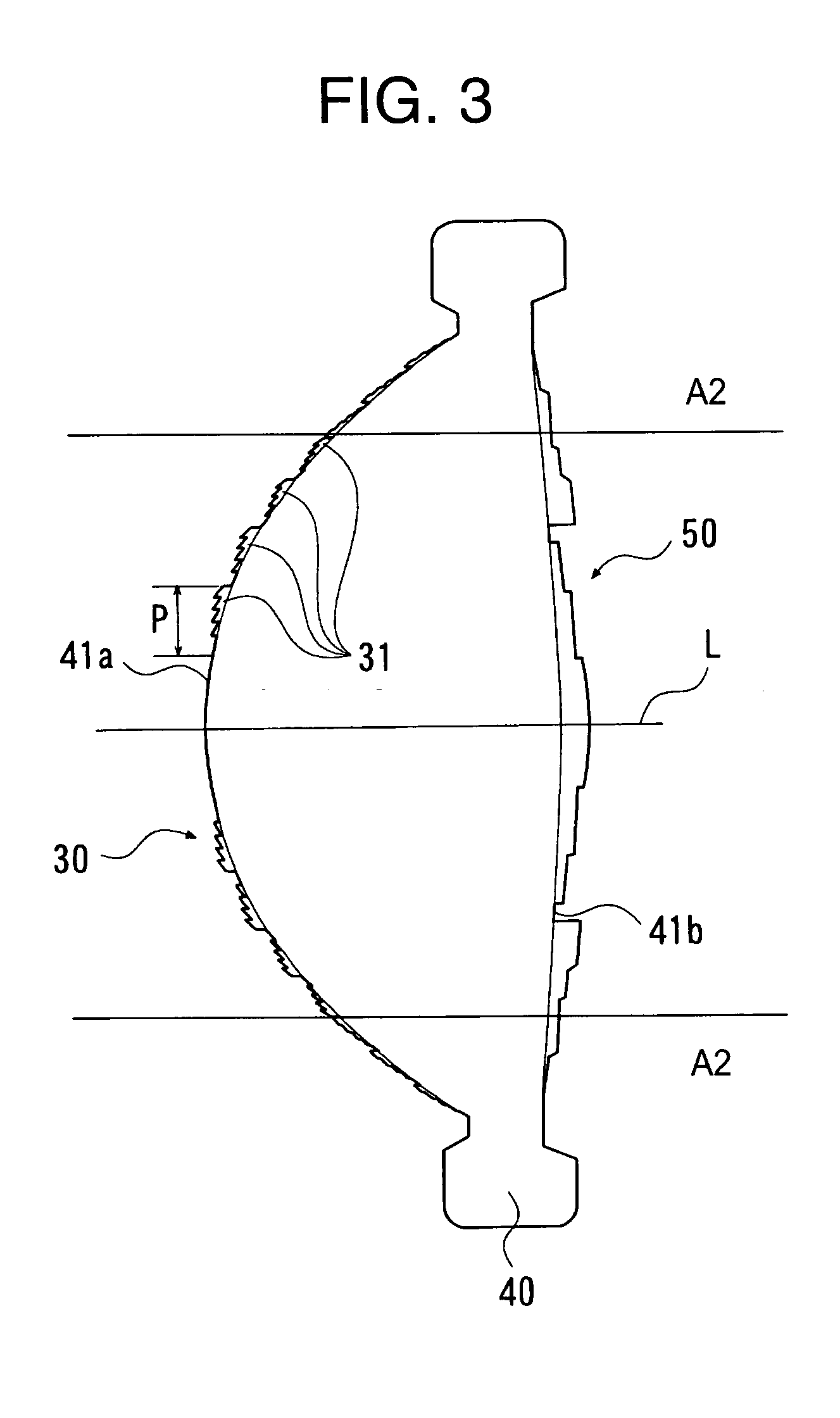

Method of optical element and objective lens

ActiveUS20060114796A1Slow changeHigh use efficiencyRecord information storageOptical beam guiding meansDiffraction orderLight beam

A method of designing an optical element to be used for an optical system in which each of a plurality of light beams having different design wavelengths passes through the optical element is provided. The method includes determining at least two types of optical path difference functions including first and second optical path difference functions in such a manner that proportion, brought by the first optical path difference function, between diffraction orders at which diffraction efficiencies of the plurality of light beams are maximized is different from proportion, brought by the second optical path difference function, between diffraction orders at which diffraction efficiencies of the plurality of light beams are maximized, and obtaining a shape defined by combining the at least two types of optical path difference functions so as to apply the obtained shape to at least one surface of surfaces of the optical element.

Owner:KONICA MINOLTA INC

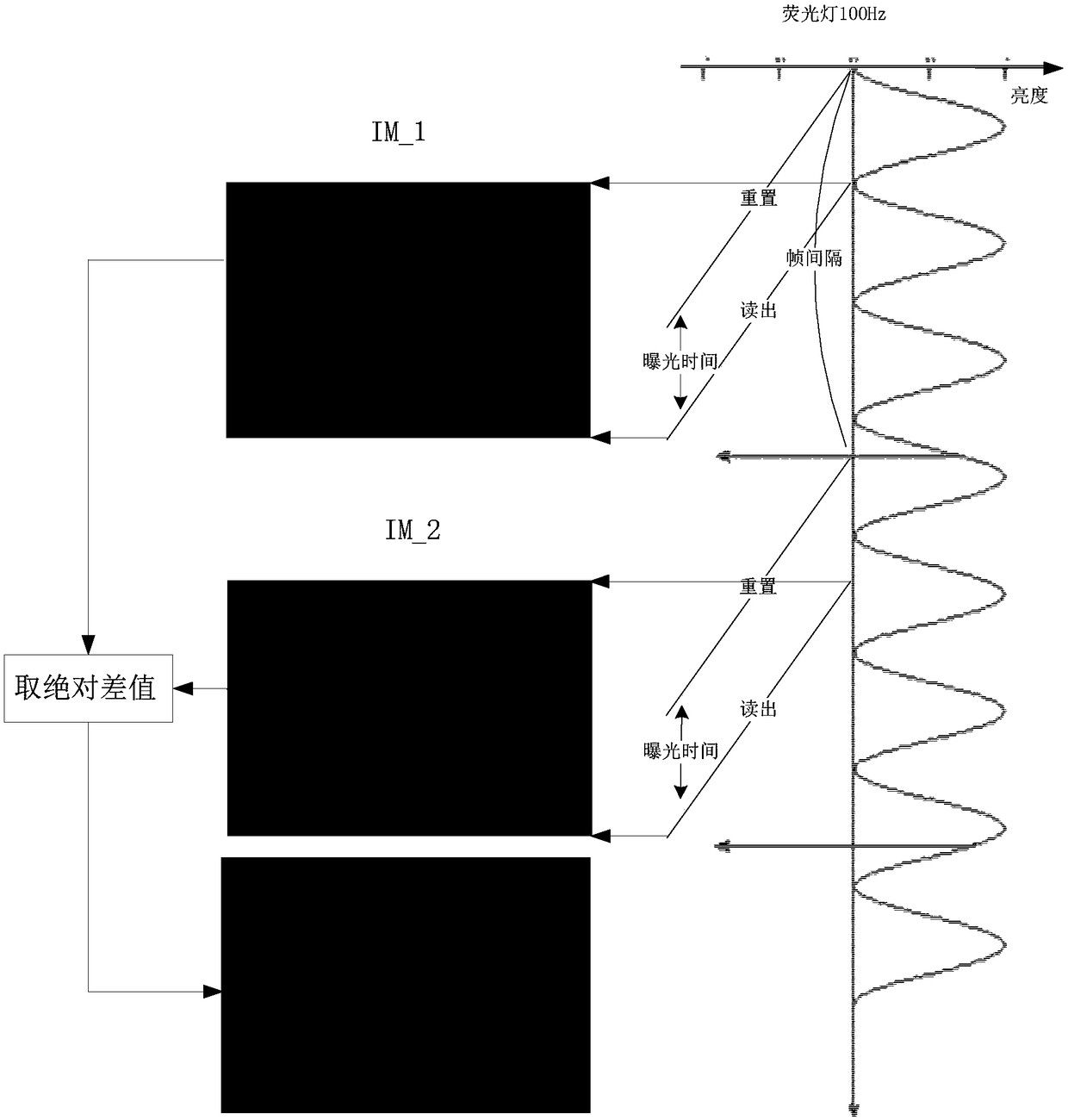

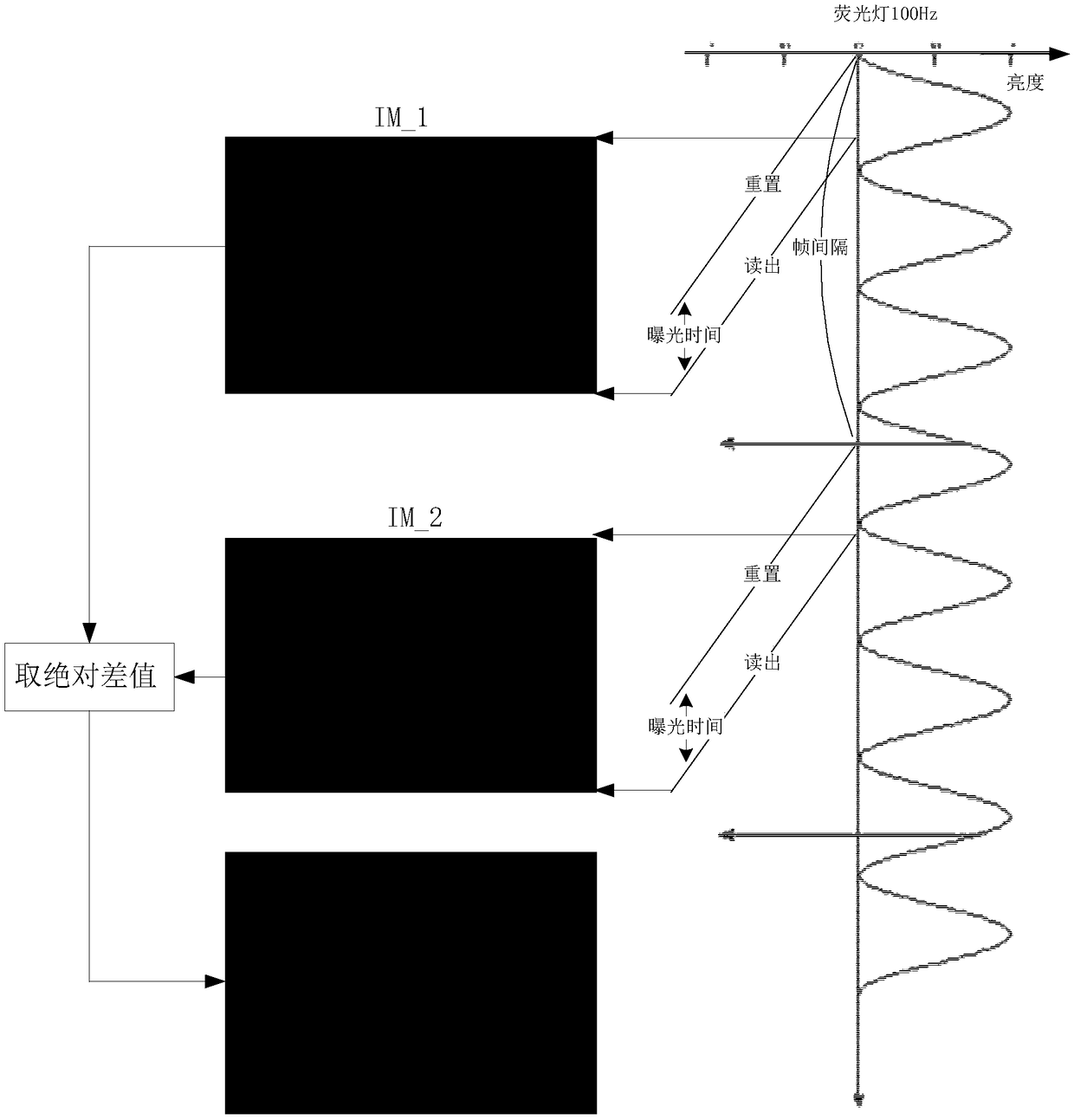

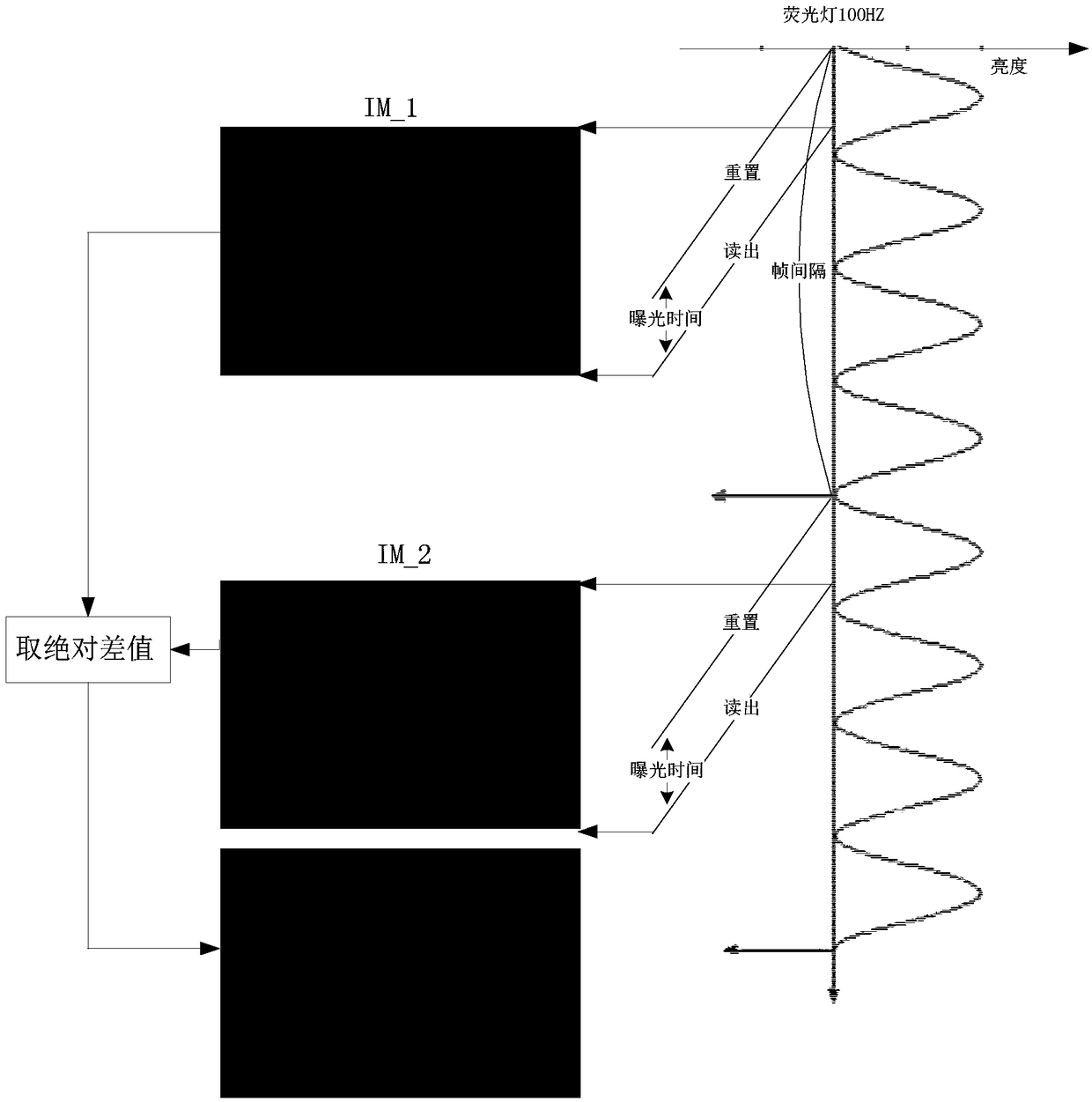

Method and device for detecting flicker of light source in video sequence and image processing apparatus

ActiveCN109274984AReduce time complexityImprove detection accuracyTelevision system detailsColor television detailsImaging processingVideo processing

Owner:ARKMICRO TECH

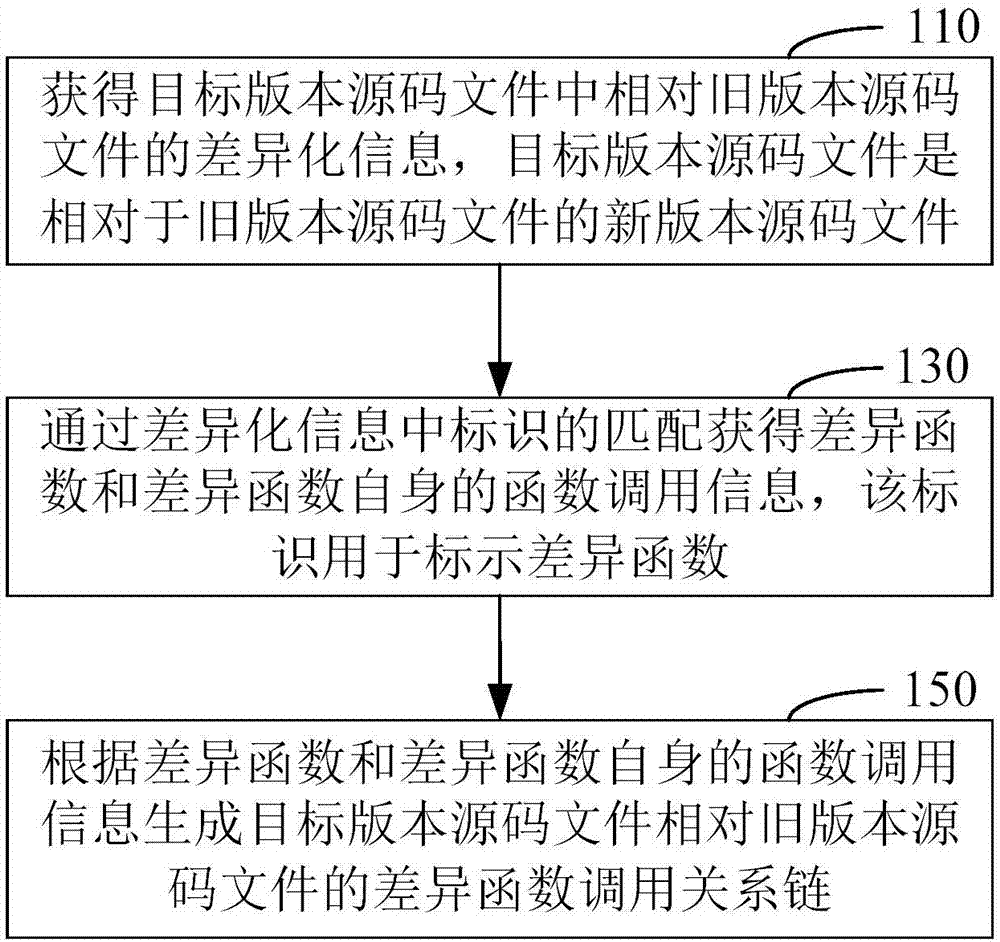

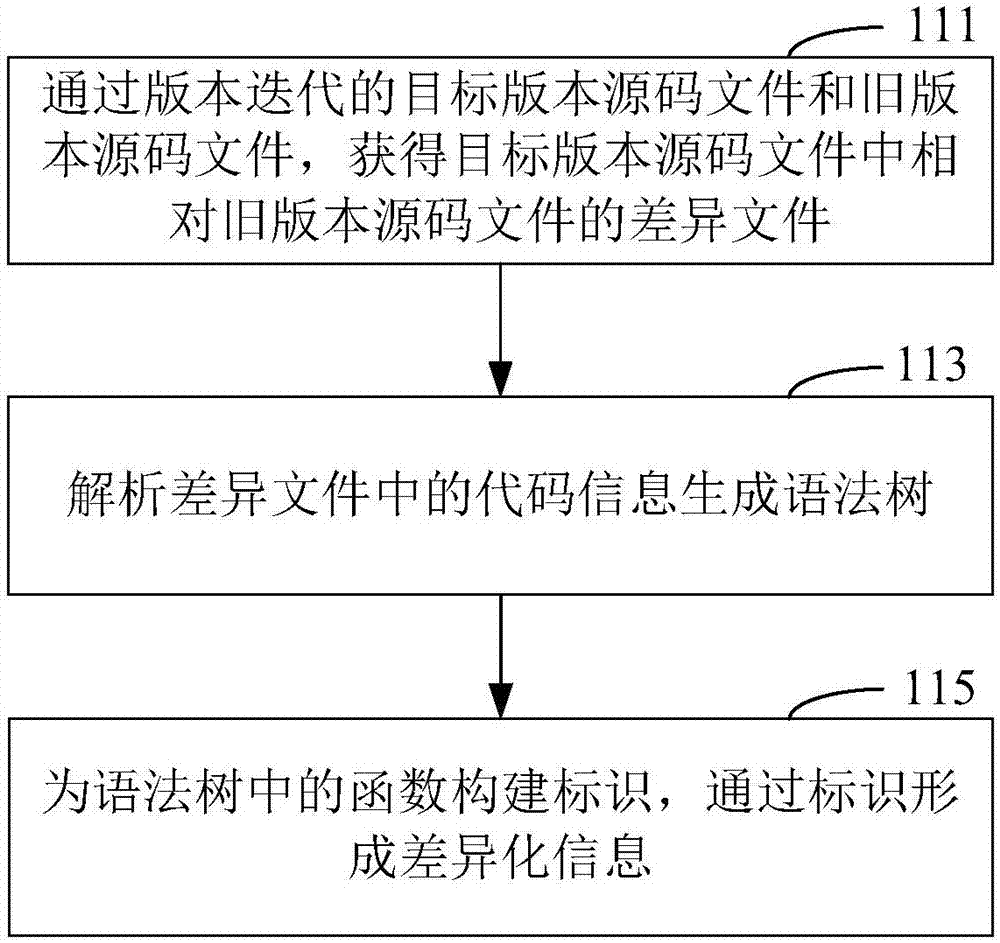

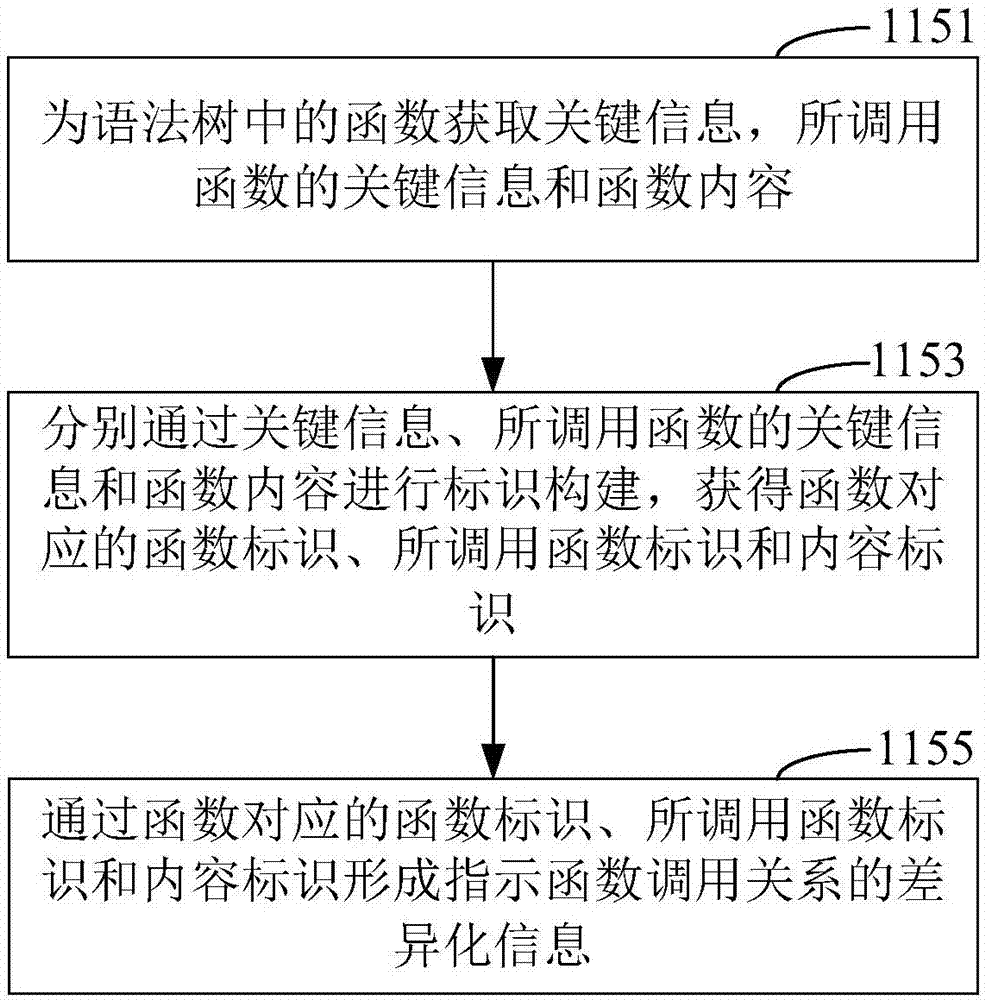

Method and apparatus for processing difference in version iteration

ActiveCN106951228AImprove accuracyVersion controlSpecific program execution arrangementsDiscrepancy functionGranularity

The present invention discloses a method and an apparatus for processing difference in version iteration. The method comprises: obtaining differentiated information of a target version source relative to an old version source file; obtaining a difference function and function call information of the difference function by matching identifications in the differentiated information, wherein the identification is used to mark the difference function; and generating a difference function call relation chain according to the difference function and the function call information of the difference function. According to the difference function call relation chain between the target version source file and the old version source file, difference due to version iteration, and the influence of the difference on the target version source file, namely, the difference function and the function call information corresponding to the difference function are obtained, so that influence positioning generated by the difference is based on function granularity, and the influence caused by version iteration is reflected on the function level; and in addition, the difference function call relation chain for reflecting the influence caused by version iteration is free from artificial experience, so that high accuracy is ensured.

Owner:TENCENT TECH (SHENZHEN) CO LTD

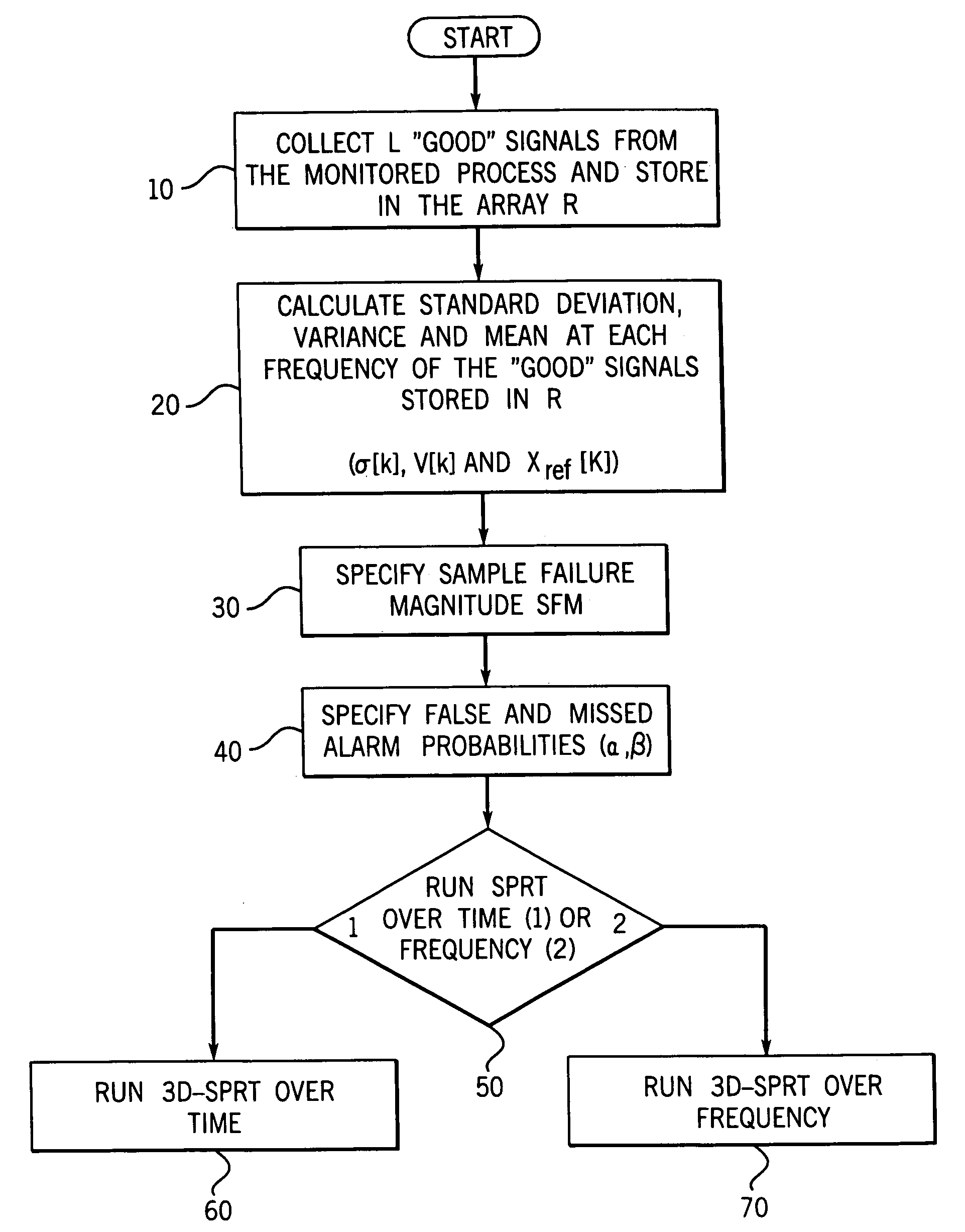

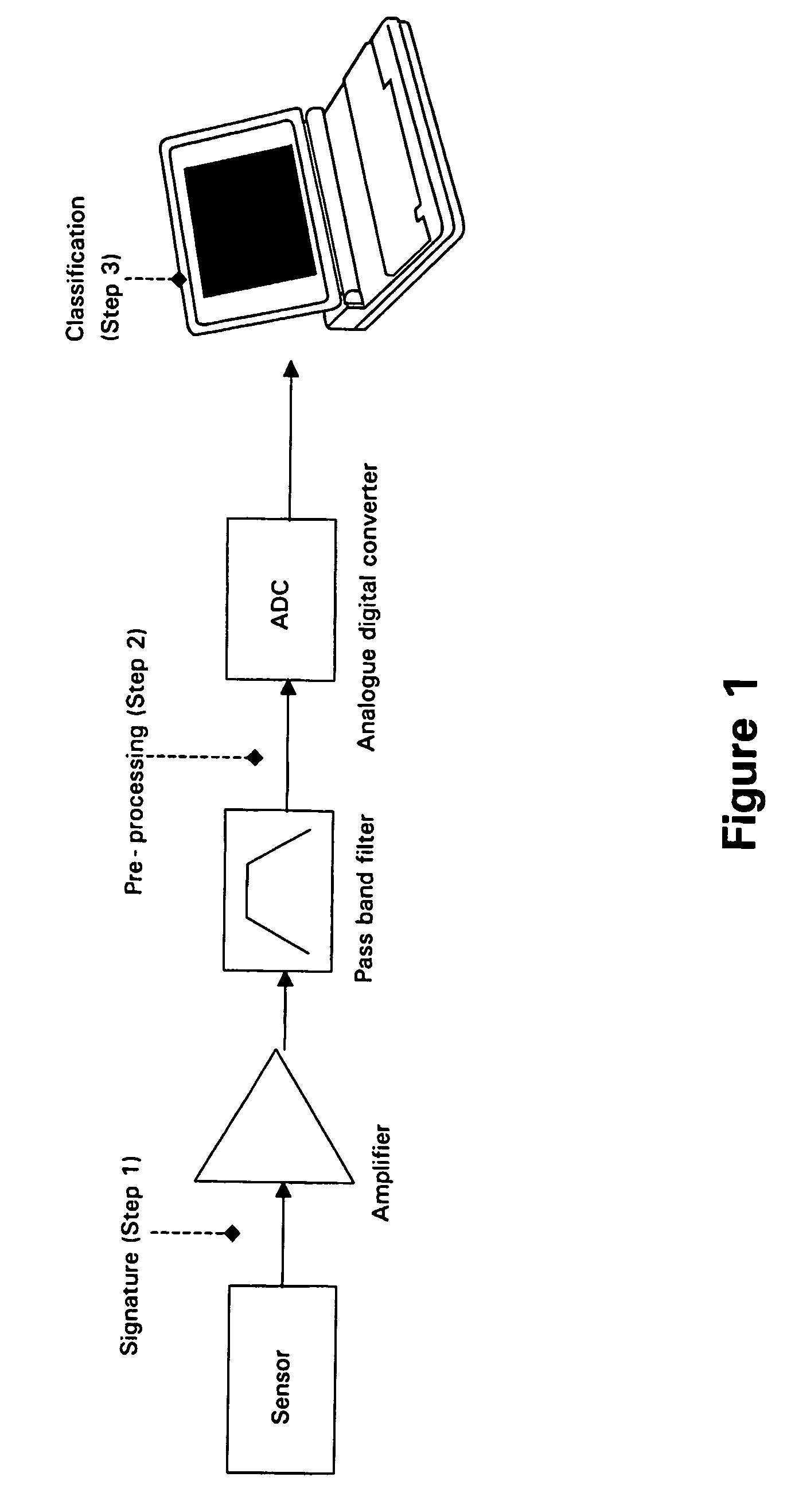

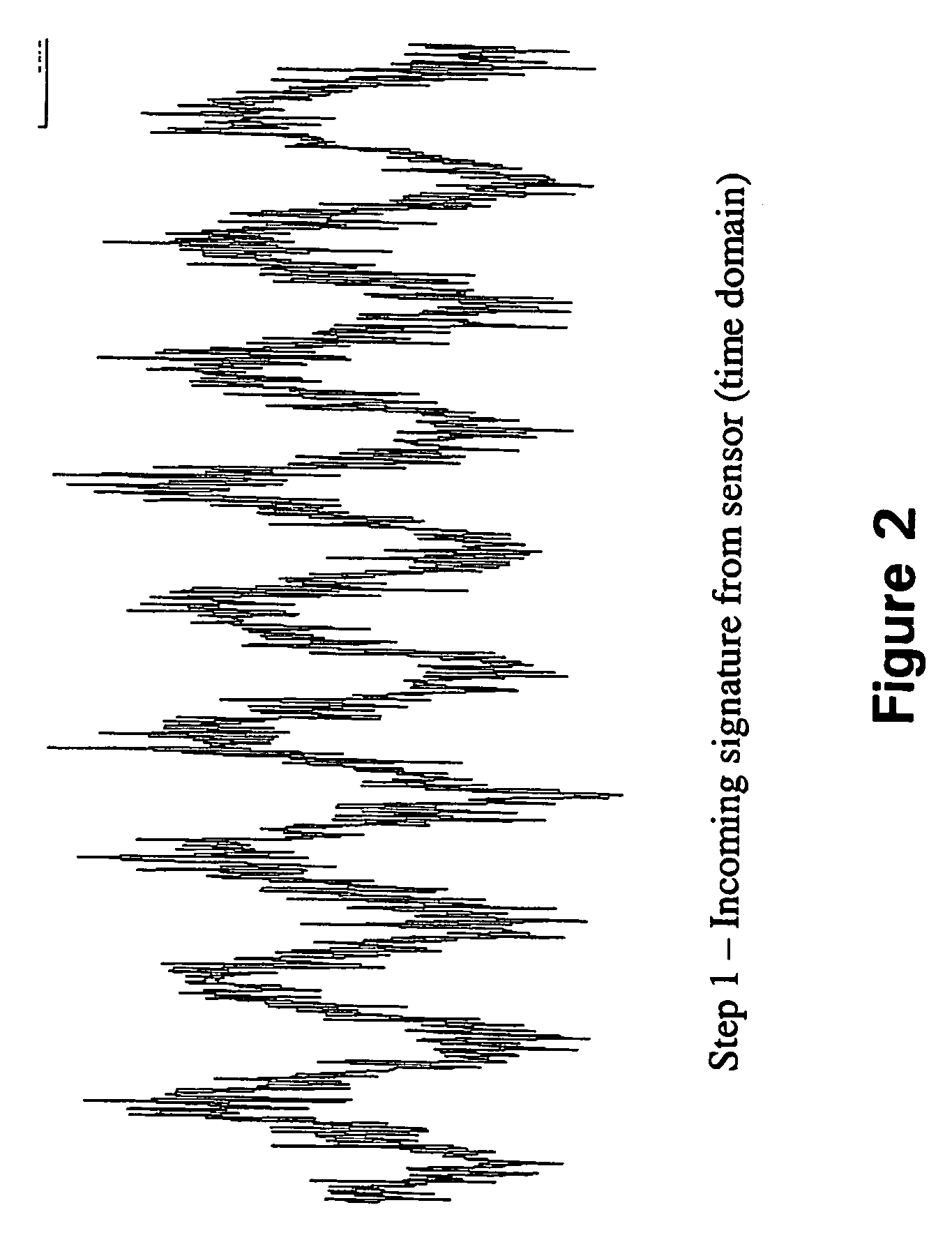

System for surveillance of spectral signals

InactiveUS6999899B2Spectral/fourier analysisAmplifier modifications to reduce noise influenceTime domainFrequency spectrum

A method and system for monitoring at least one of a system, a process and a data source. A method and system have been developed for carrying out surveillance, testing and modification of an ongoing process or other source of data, such as a spectroscopic examination. A signal from the system under surveillance is collected and compared with a reference signal, a frequency domain transformation carried out for the system signal and reference signal, a frequency domain difference function established. The process is then repeated until a full range of data is accumulated over the time domain and a Sequential Probability Ratio Test (“SPRT”) methodology applied to determine a three-dimensional surface plot characteristic of the operating state of the system under surveillance.

Owner:ARCH DEVMENT

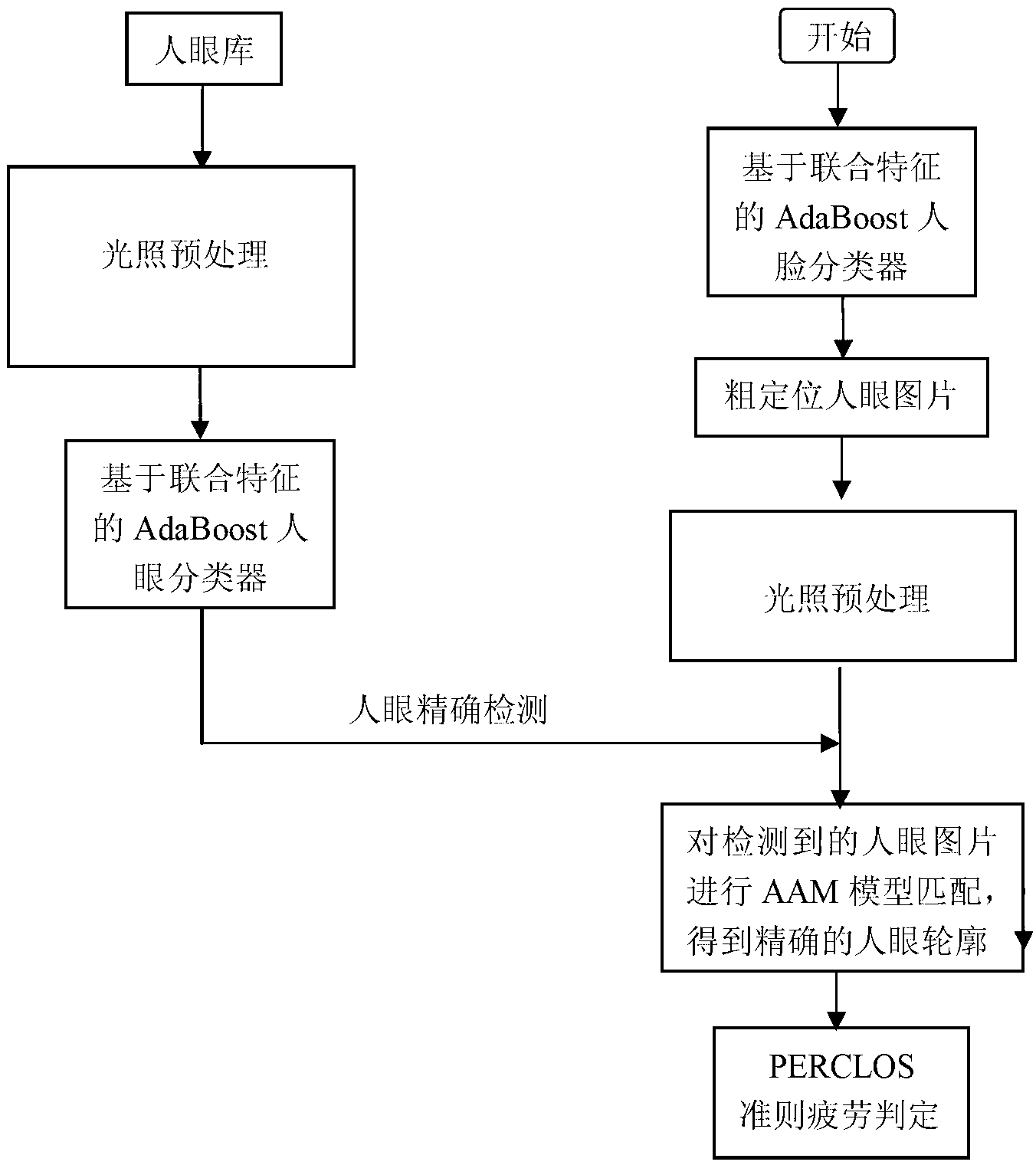

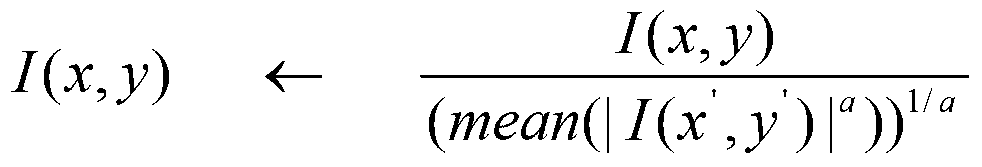

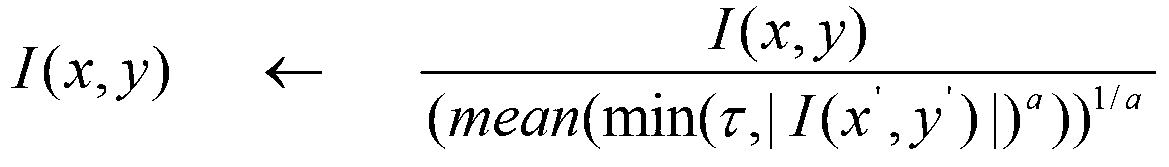

Method for detecting fatigue driving around clock

InactiveCN103268479AImprove adaptabilityContrast EqualizationCharacter and pattern recognitionPretreatment methodMatrix function

The invention provides a method for detecting fatigue driving around the clock. A camera is used for acquiring a human face image to primarily position the eyes of a person; afterwards, a human eye image which is well processed by light is obtained through light preprocessing, then the human eye image is matched with a trained human eye template, and therefore the state of opening and closing of human eyes is acquired; at last, a driver is judged whether to be fatigue or not through a PERCLOS fatigue judging criterion. A light preprocessing method with the contrast ratio balanced is provided, variation of image light and dark areas is used, a convolution operation is conducted according to a convolution operation function and a Gaussian difference function, and therefore contrast ratio balance is achieved. Furthermore, the invention provides a human eye positioning method with multi-feature fusion. The advantages of various features are used, fused features can more effectively present a detected object, detecting is more accurate, and adaptability is stronger.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

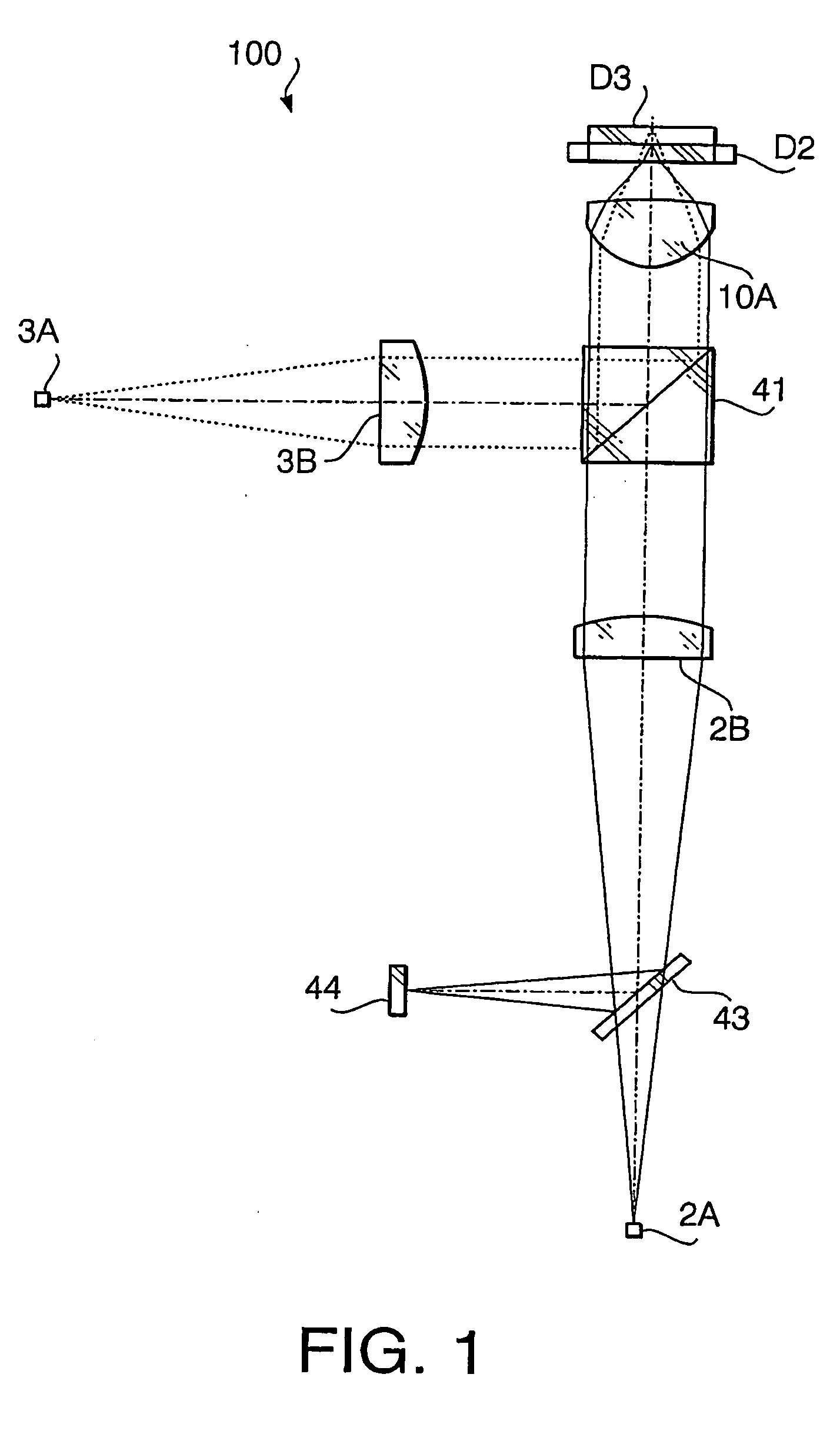

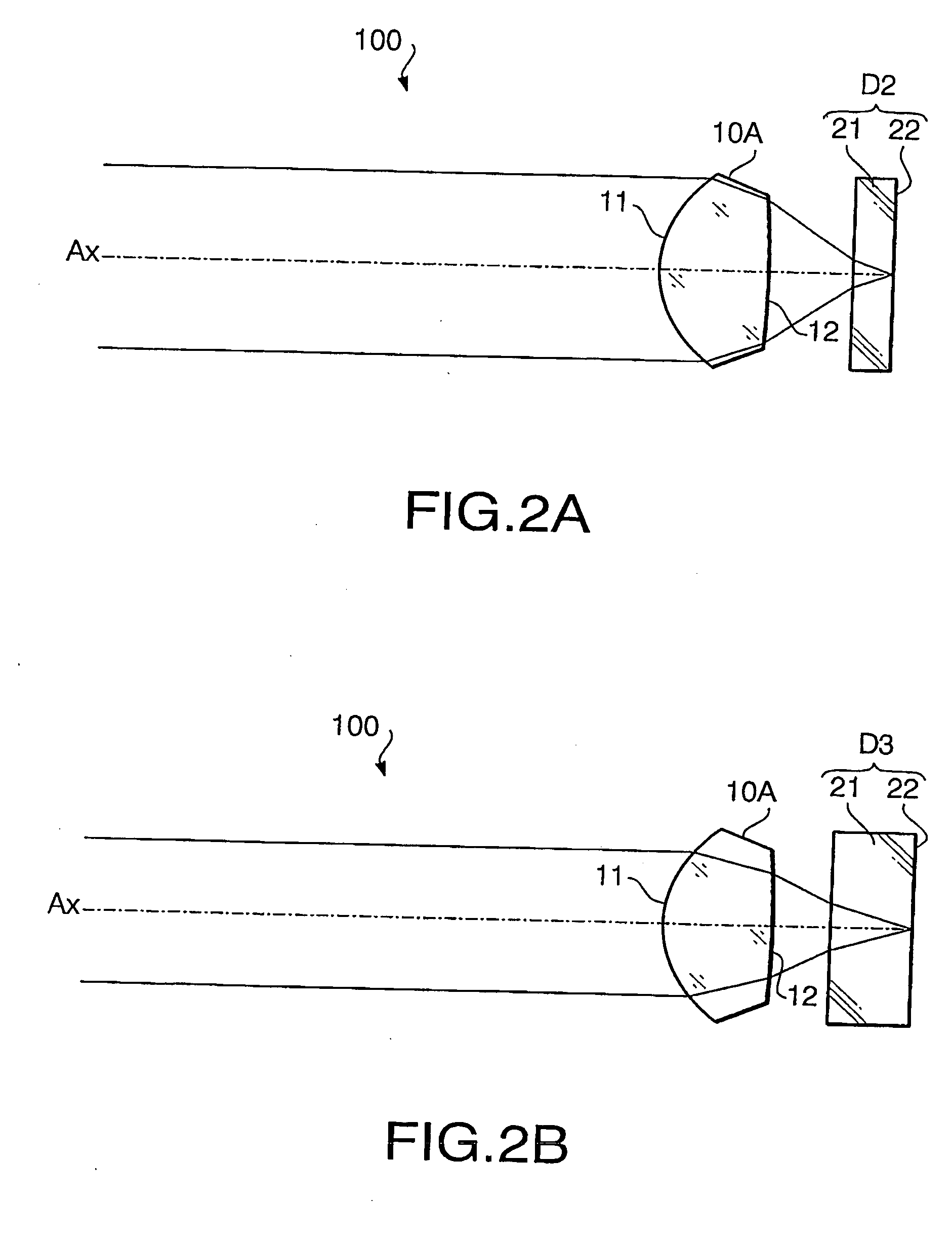

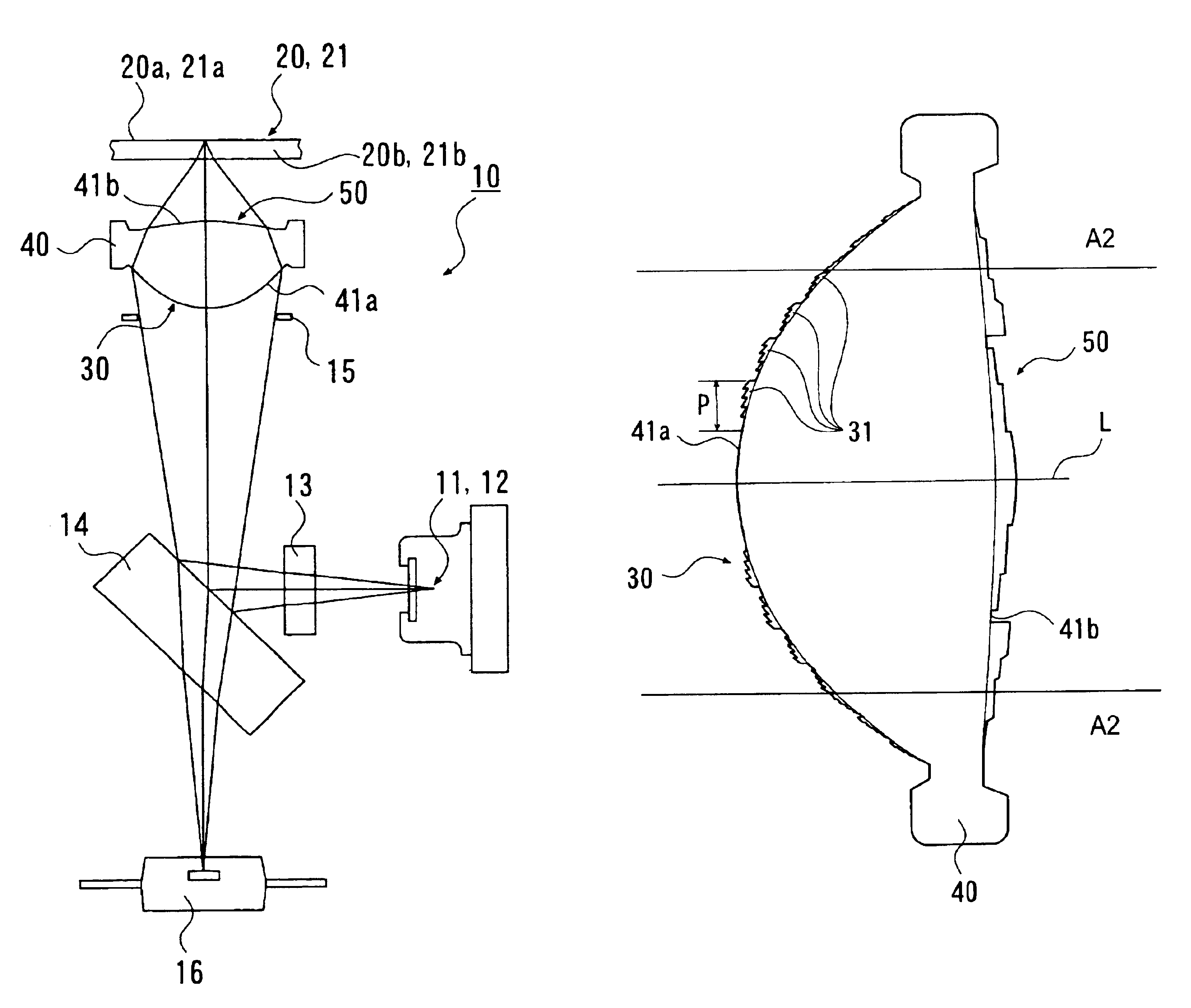

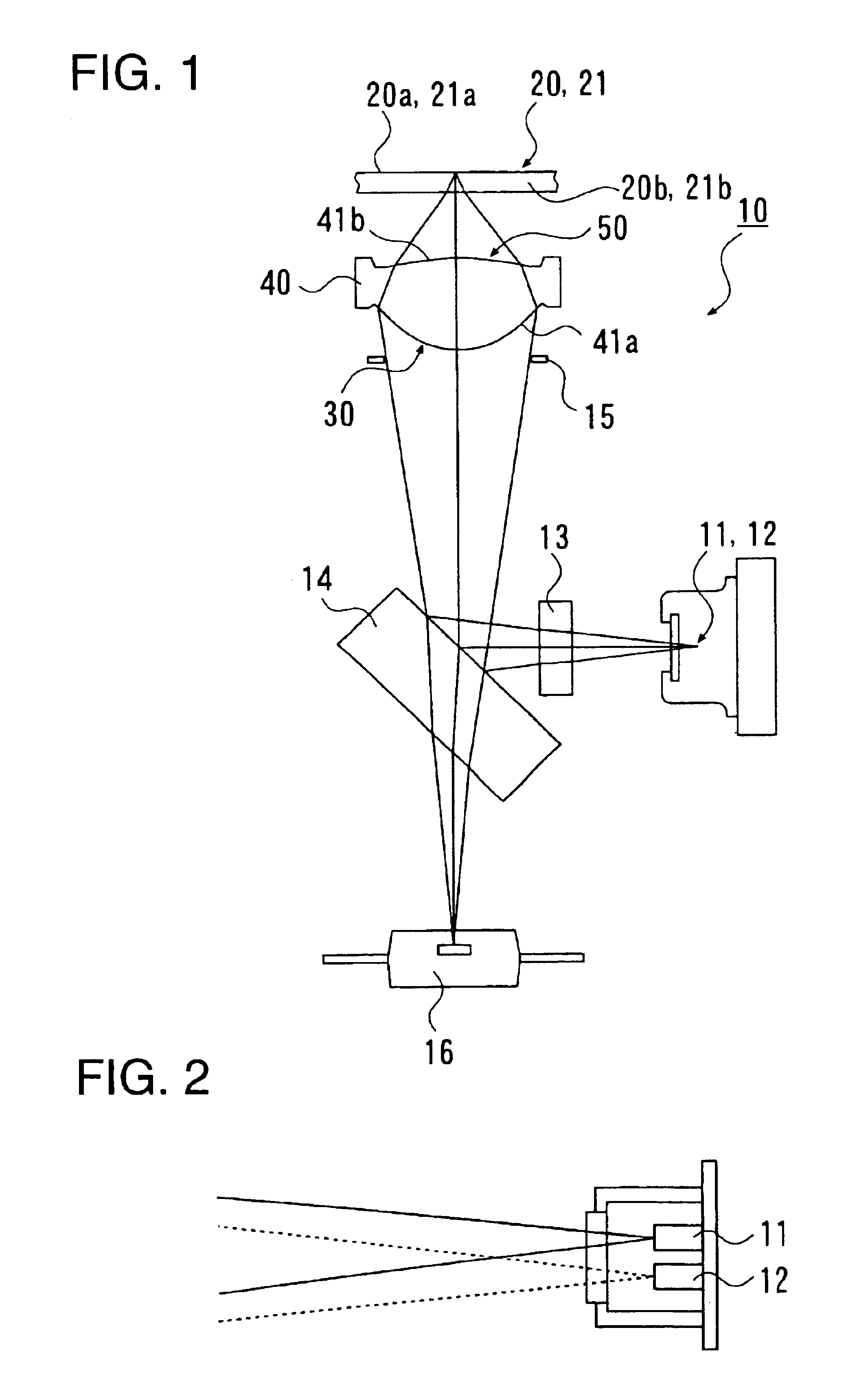

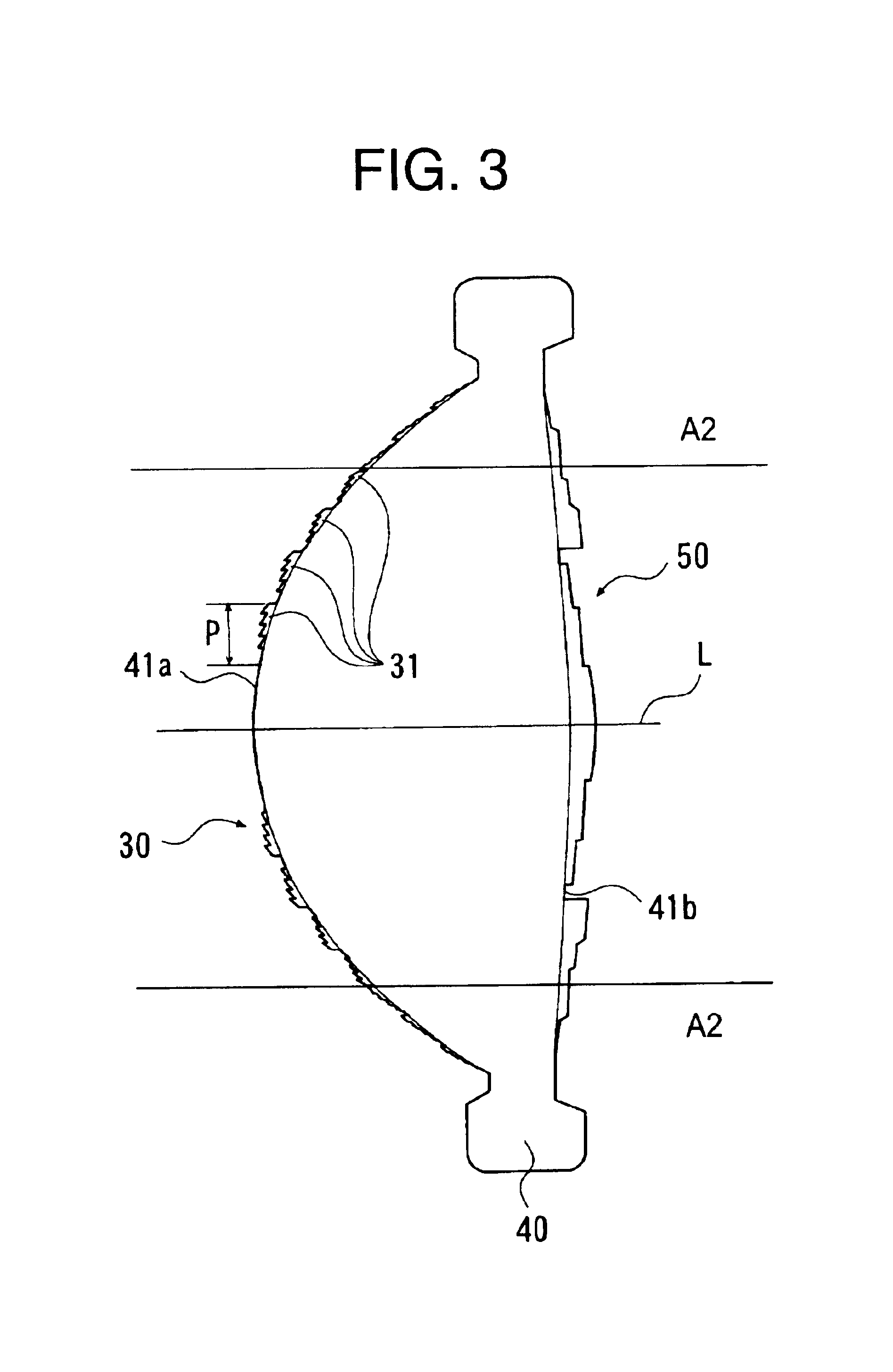

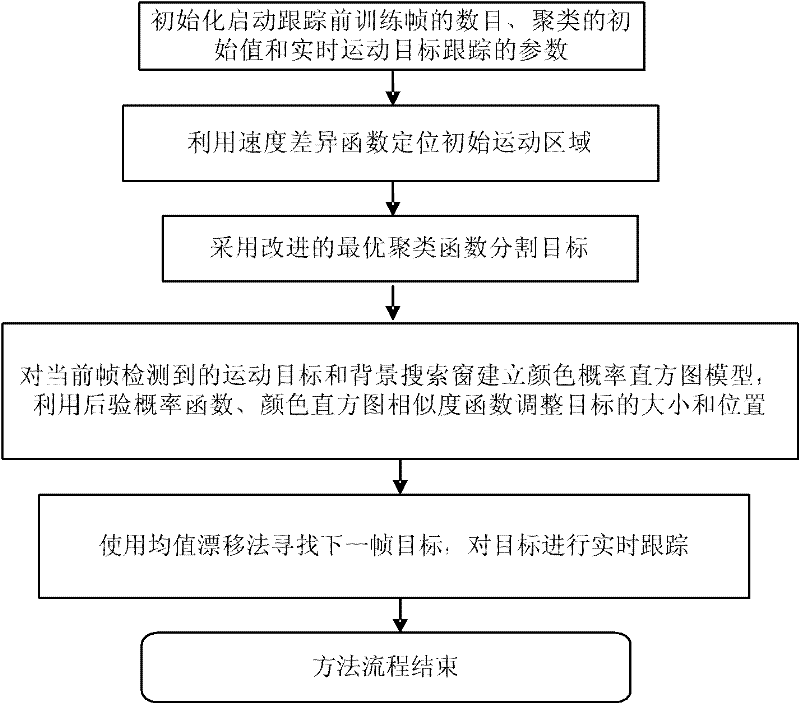

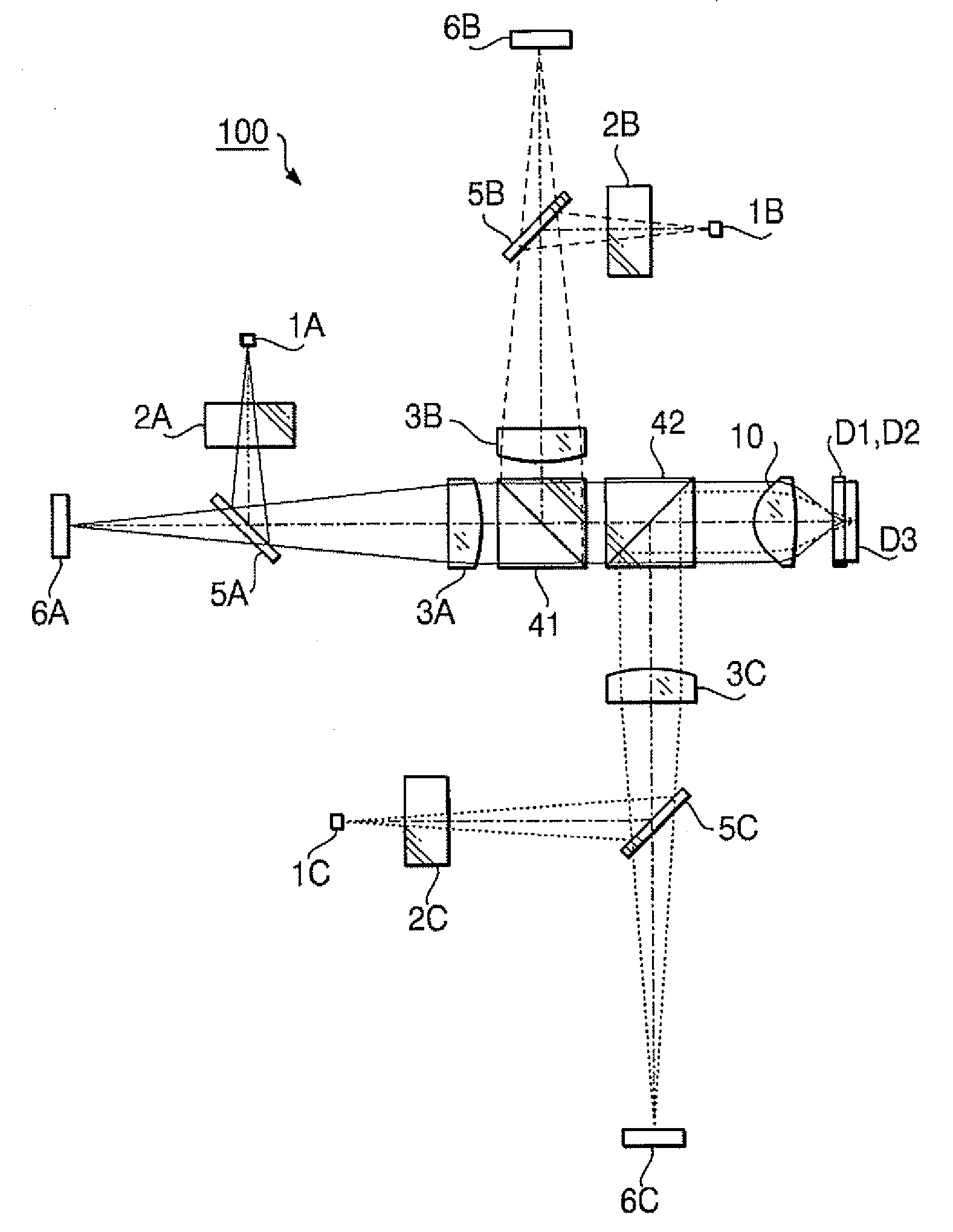

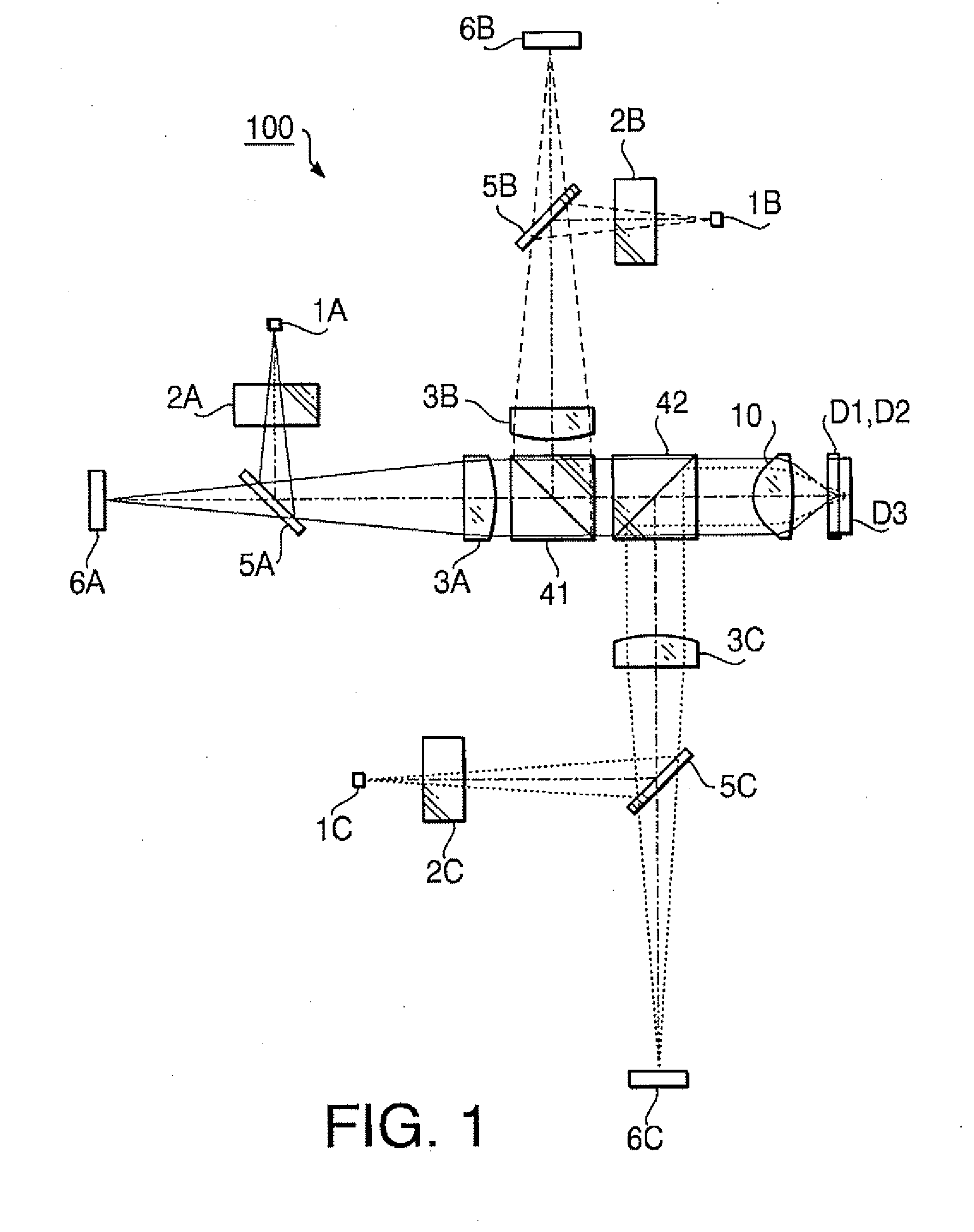

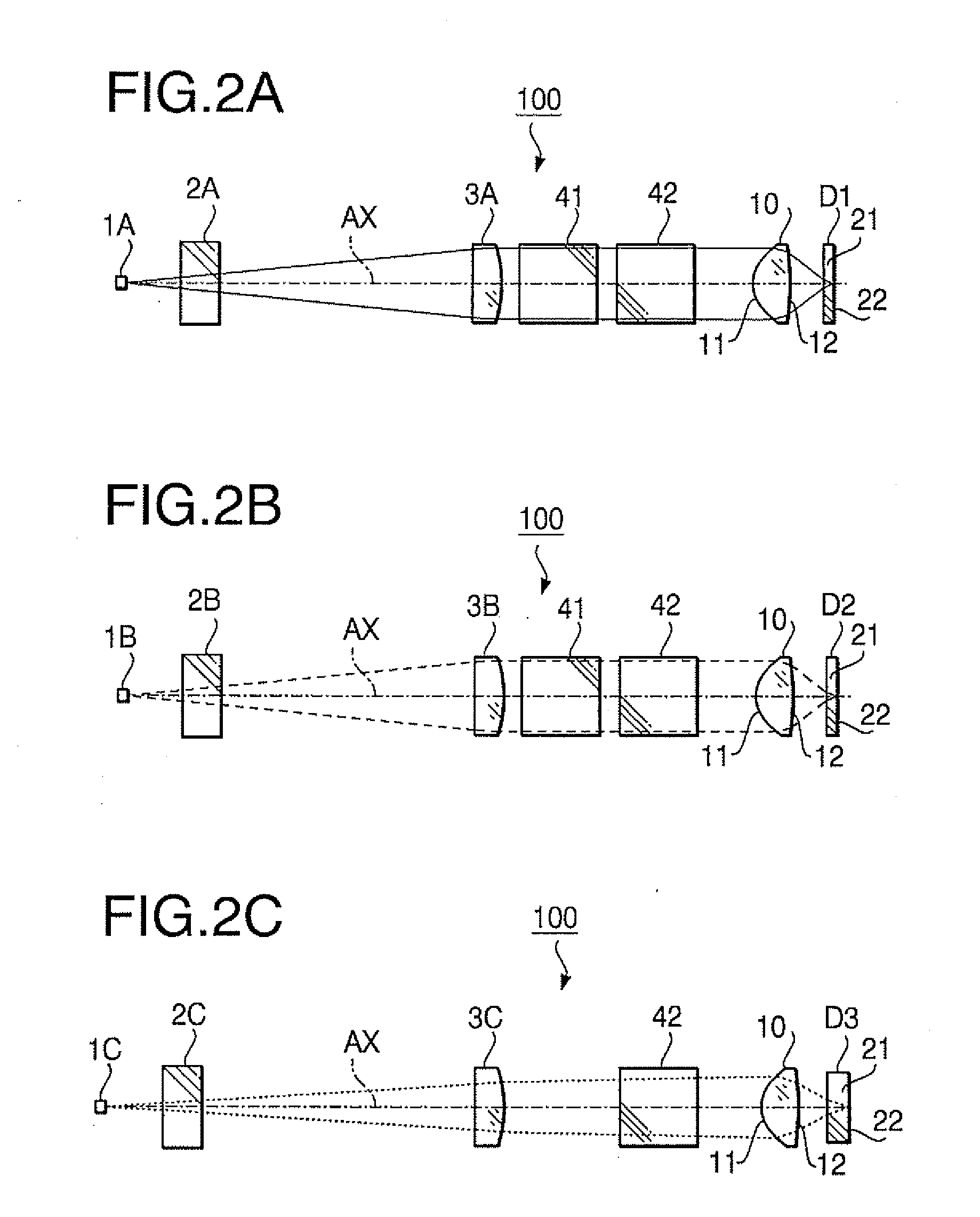

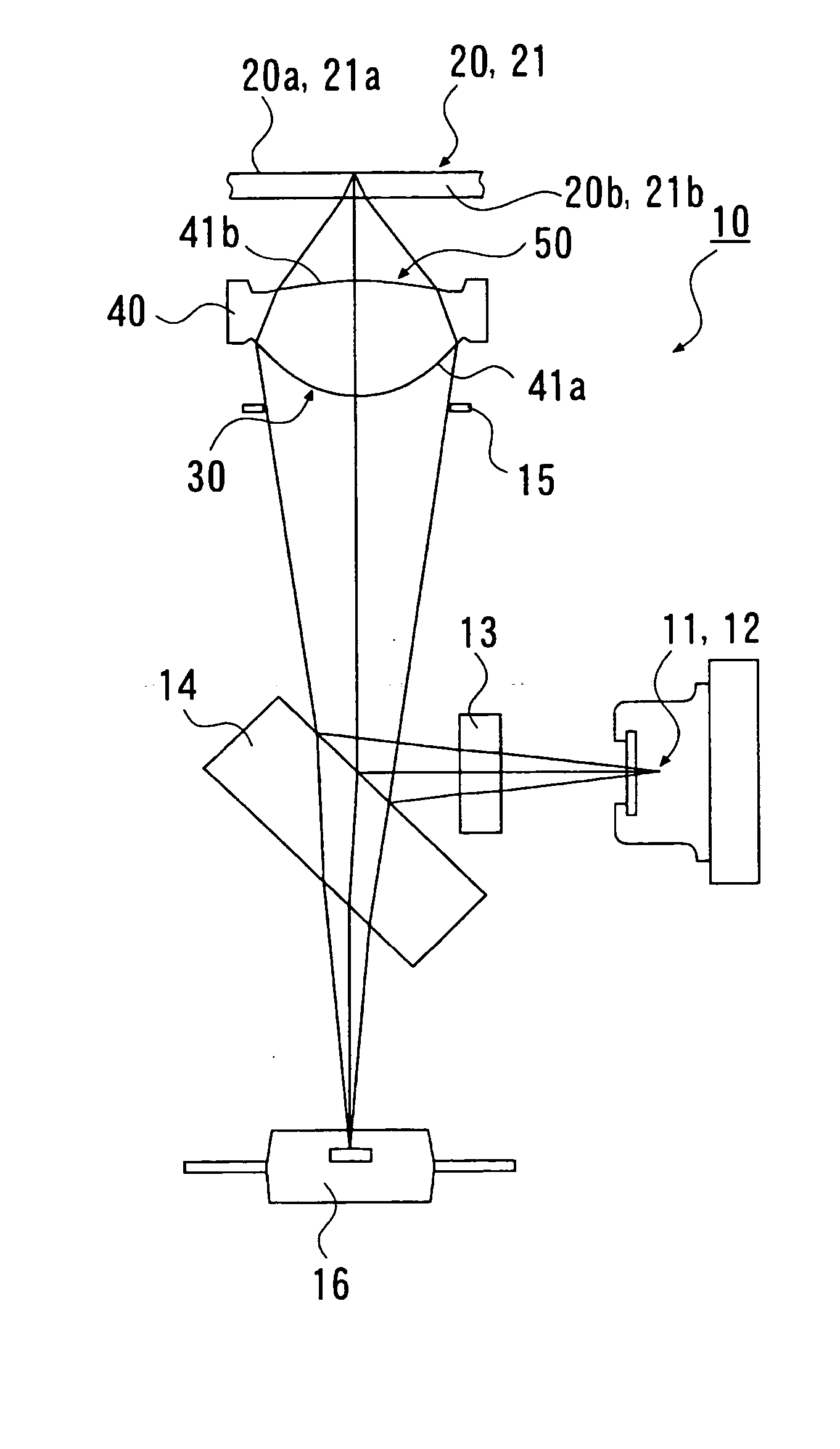

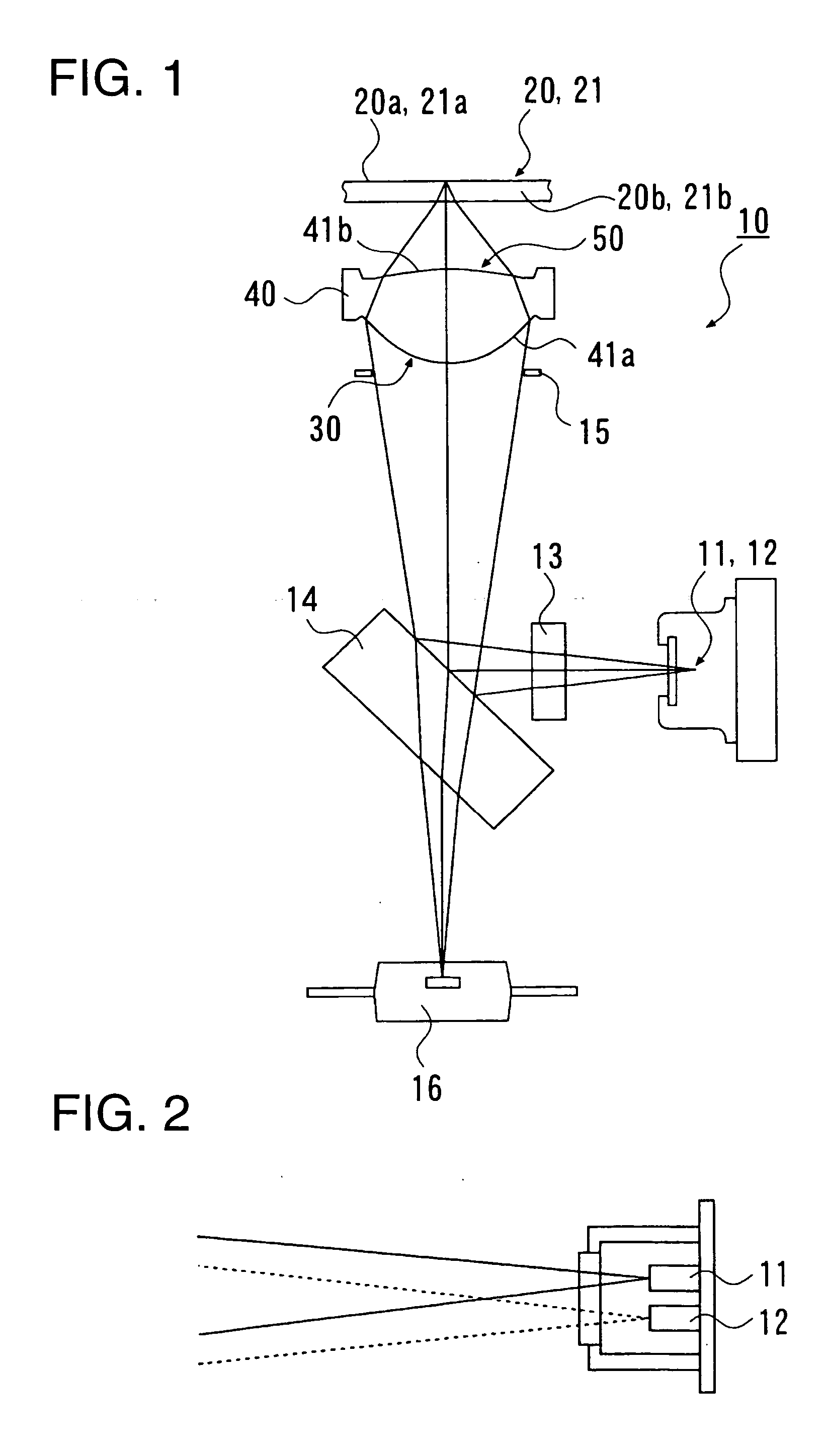

Optical pickup apparatus, condensing optical system, and optical element

InactiveUS6952390B2Improve aberrationExcellent characteristicsOptical beam sourcesRecord information storageOptical pickupDiffraction effect

This invention is directed to an optical pickup apparatus, condensing optical system, and optical element which can at least reproduce and / or record information from / on a first optical information recording medium having a protective substrate thickness t1 by using a light beam of a first wavelength λ1 emitted from a first light source, and reproduce and / or record information from / on a second optical information recording medium having a protective substrate thickness t2 (t2≧t1) by using a light beam of a second wavelength λ2 (λ2>λ1) emitted from a second light source. The optical pickup apparatus of the invention includes a first phase modulator which gives a diffraction effect to only the light beam of the wavelength λ1 on at least one optical surface, of a plurality of optical surfaces of a plurality of optical elements arranged on a common optical path through which the light beam of the first wavelength λ1 and the light beam of the second wavelength λ2 pass, and a second phase modulator which gives a diffraction effect to only the light beam of the wavelength λ2 on at least one of the remaining optical surfaces. Each of the first phase modulator and second phase modulator has staircase-like discontinuous parts, each formed from a predetermined number of stepped portions, formed concentrically around an optical axis at the pitch defined by an optical path difference function.

Owner:KONICA MINOLTA OPTO

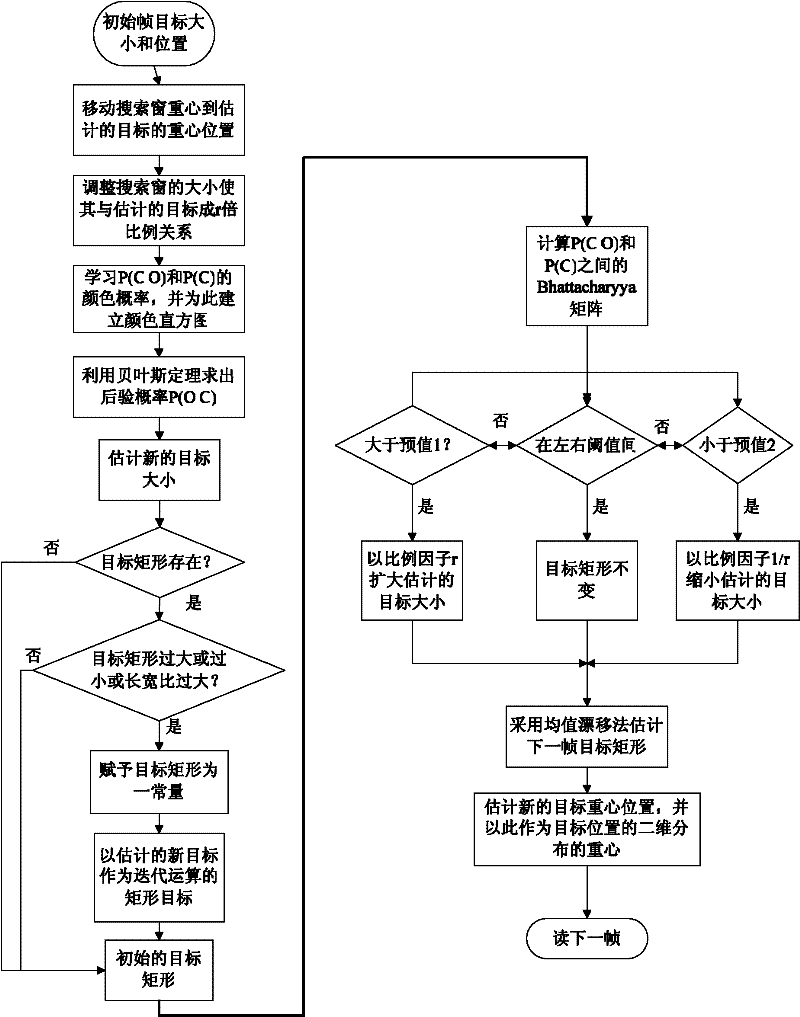

Probabilistic model based automatic target tracking method for moving camera

ActiveCN102332166AAddresses issues with inaccurate tracking of targetsImage analysisProbit modelMean-shift

The invention provides a probabilistic model based automatic target tracking method for a moving camera, which comprises the following specific steps of: firstly, initializing start tracking parameters and real-time moving target tracking parameters; secondly, utilizing a speed difference function to position an initial moving area, and adopting an improved optimal clustering function to segment a moving target; thirdly, establishing a color probability histogram model for the moving target detected by the current frame and a background search window, and utilizing a posteriori probability function and a color histogram similarity function to adjust the size and position of the target; and finally, using a continuously adaptive mean shift method to find the next-frame moving target to achieve the real-time tracking of the moving target in the dynamic background. In the invention, the reliability of moving target tracking is improved, and the problems of selection of initial targets and multi-target tracking, and the problems that the target and background have the same color and the target color changes can be effectively solved under the moving camera.

Owner:BEIHANG UNIV

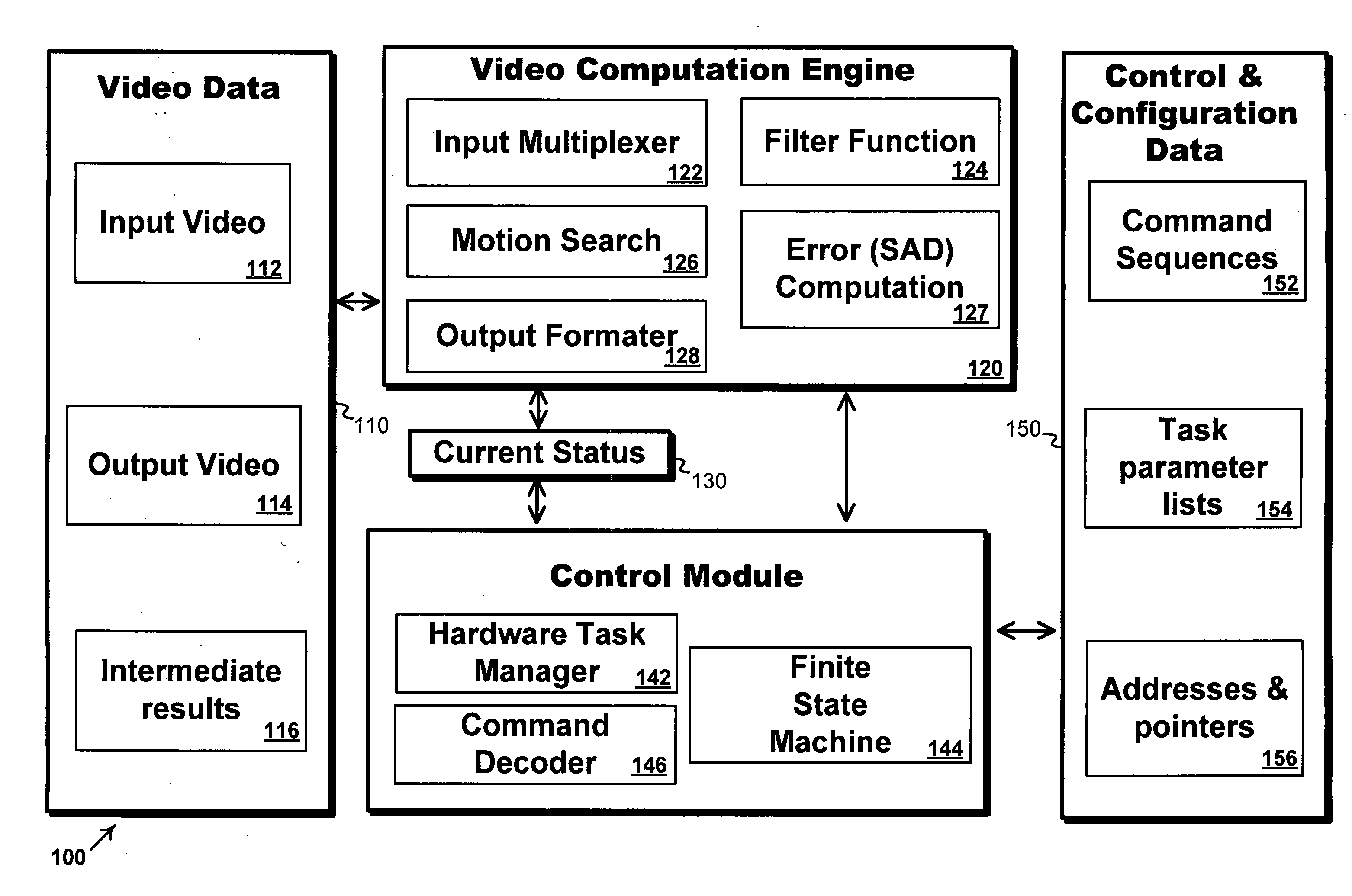

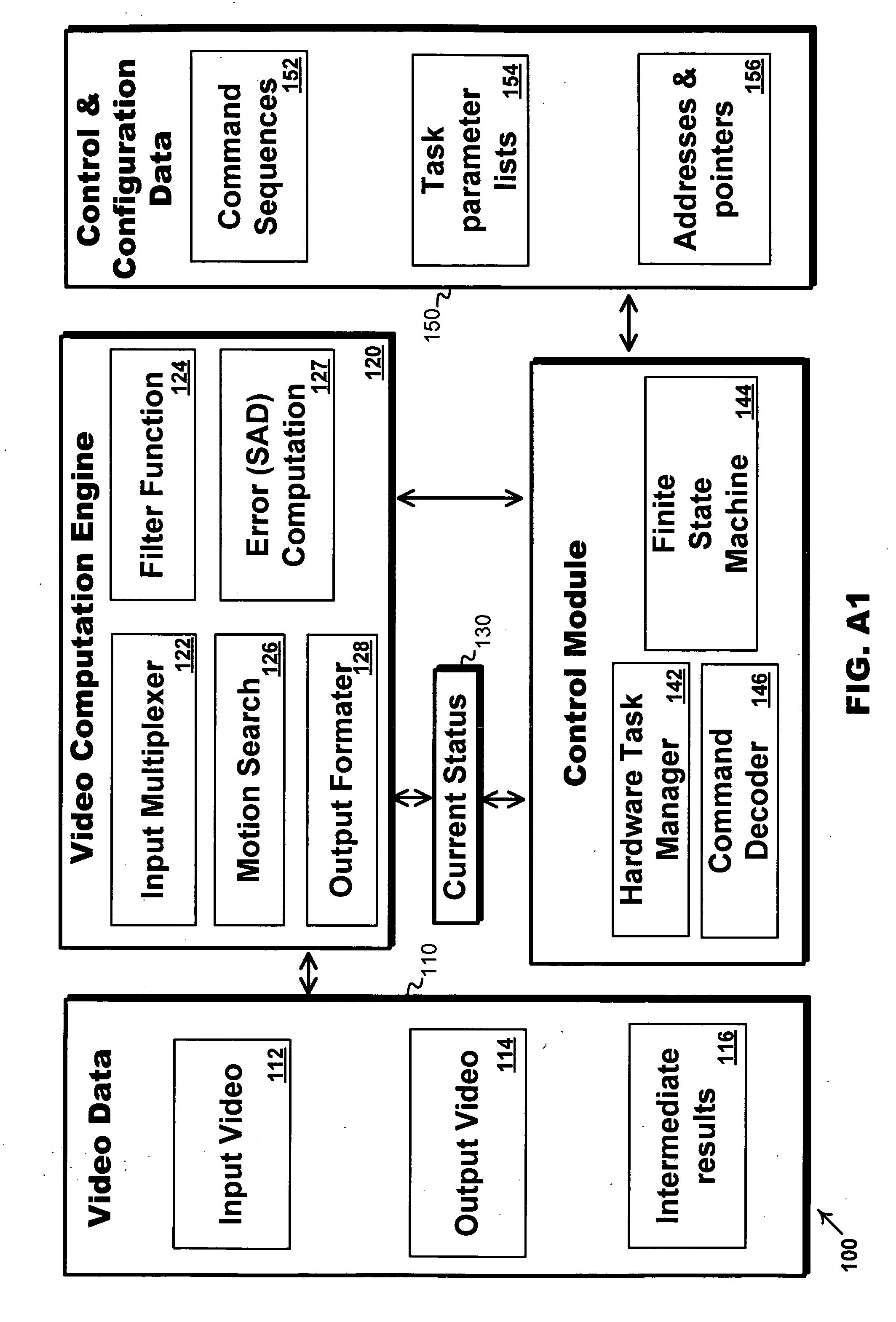

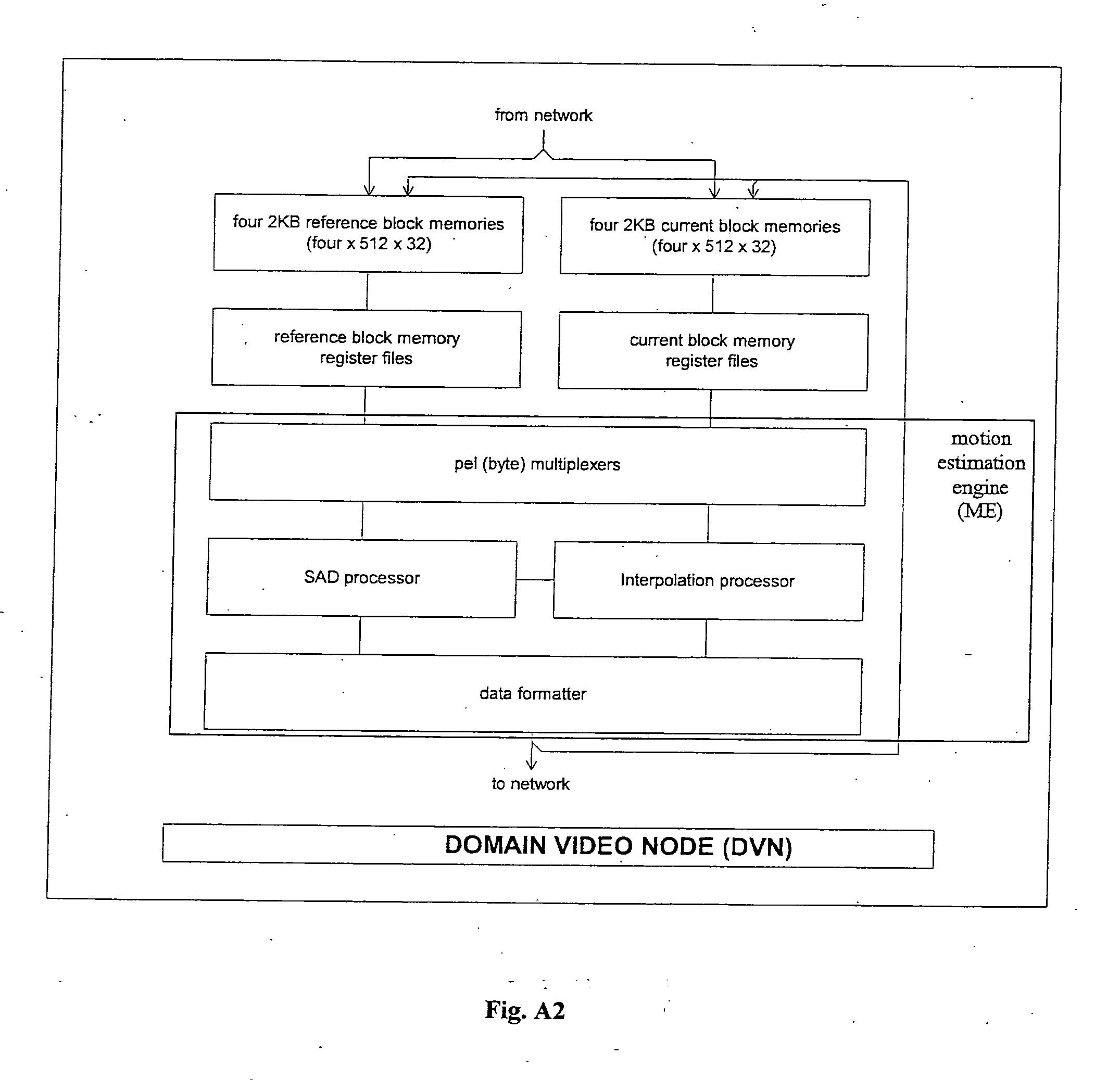

Processor for video data encoding/decoding

ActiveUS20080130742A1Improve accuracyImprove perceived qualityColor television with pulse code modulationColor television with bandwidth reductionComputer architectureVideo processing

A video processor uses attributes of video data to perform encoding and decoding. Some embodiments dynamically configure the processor via a sequence of instructions, where the instructions include information on the attributes of the current video data. Some embodiments include a dynamically configurable adder array that computes difference functions thereby generating error vectors. Some embodiments include a dynamically configurable adder array that computes filtering functions applied to the video data, e.g. interpolation or decimation of the incoming video prior to motion detection. Some embodiments of the invention provide dynamically configurable hardware searches, for example, for detecting motion. Some embodiments of the invention are implemented using an adaptive computing machines (ACMs). An ACM includes a plurality of heterogeneous computational elements, each coupled to an interconnection network.

Owner:NVIDIA CORP

Demultiplexer with a square spectral response

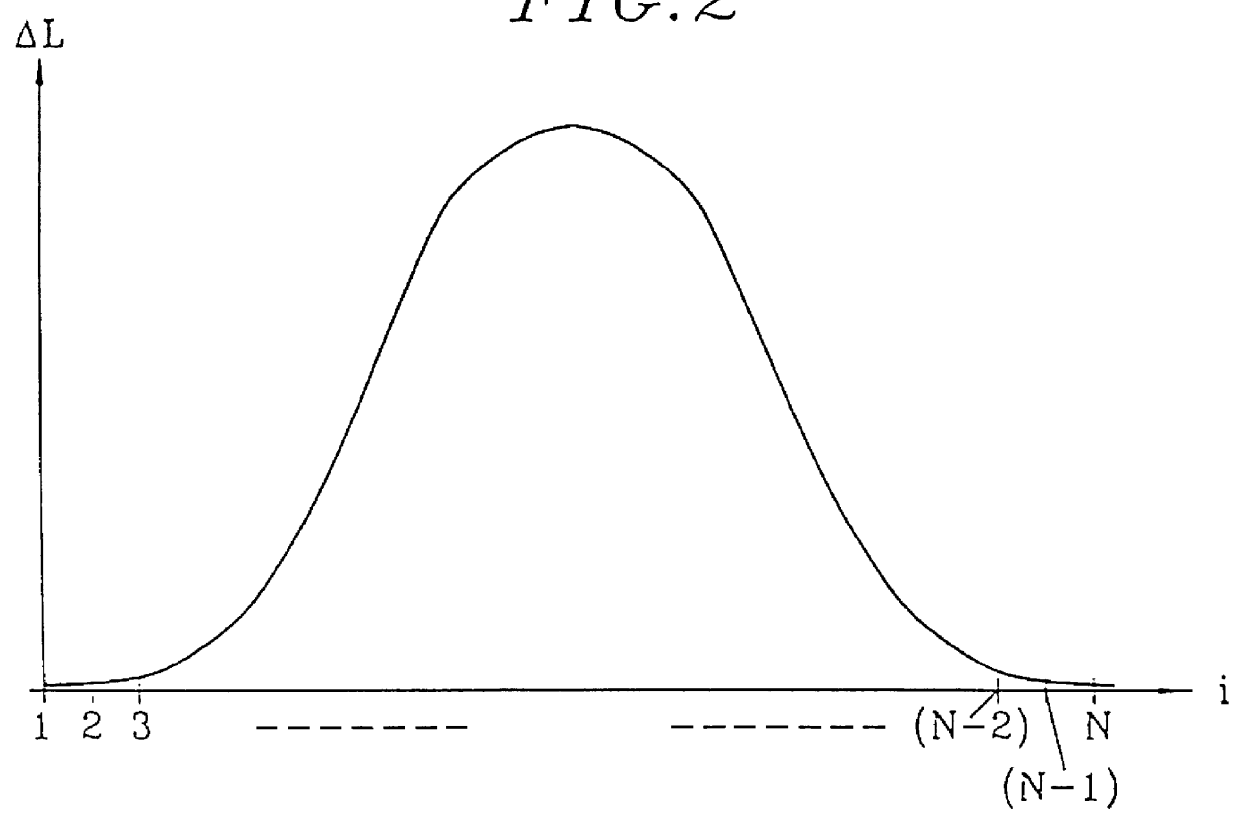

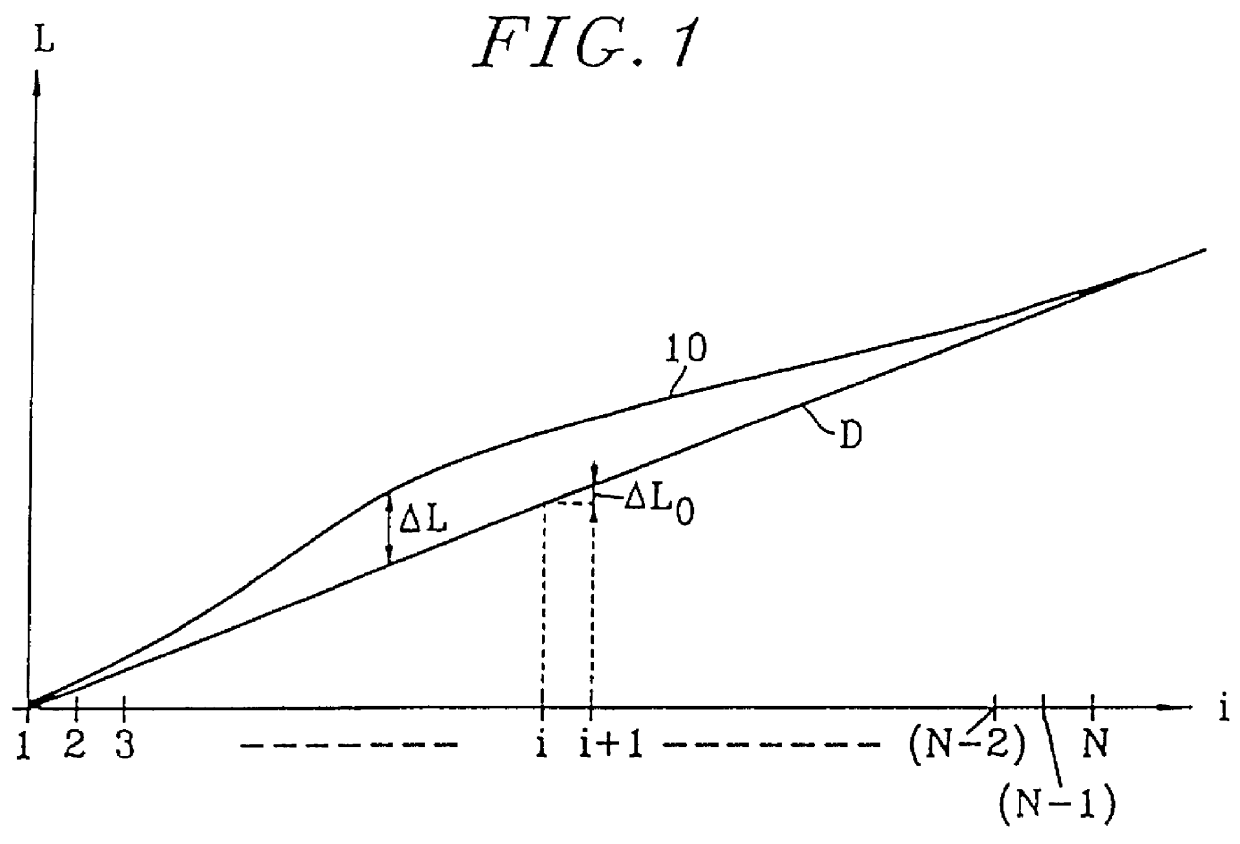

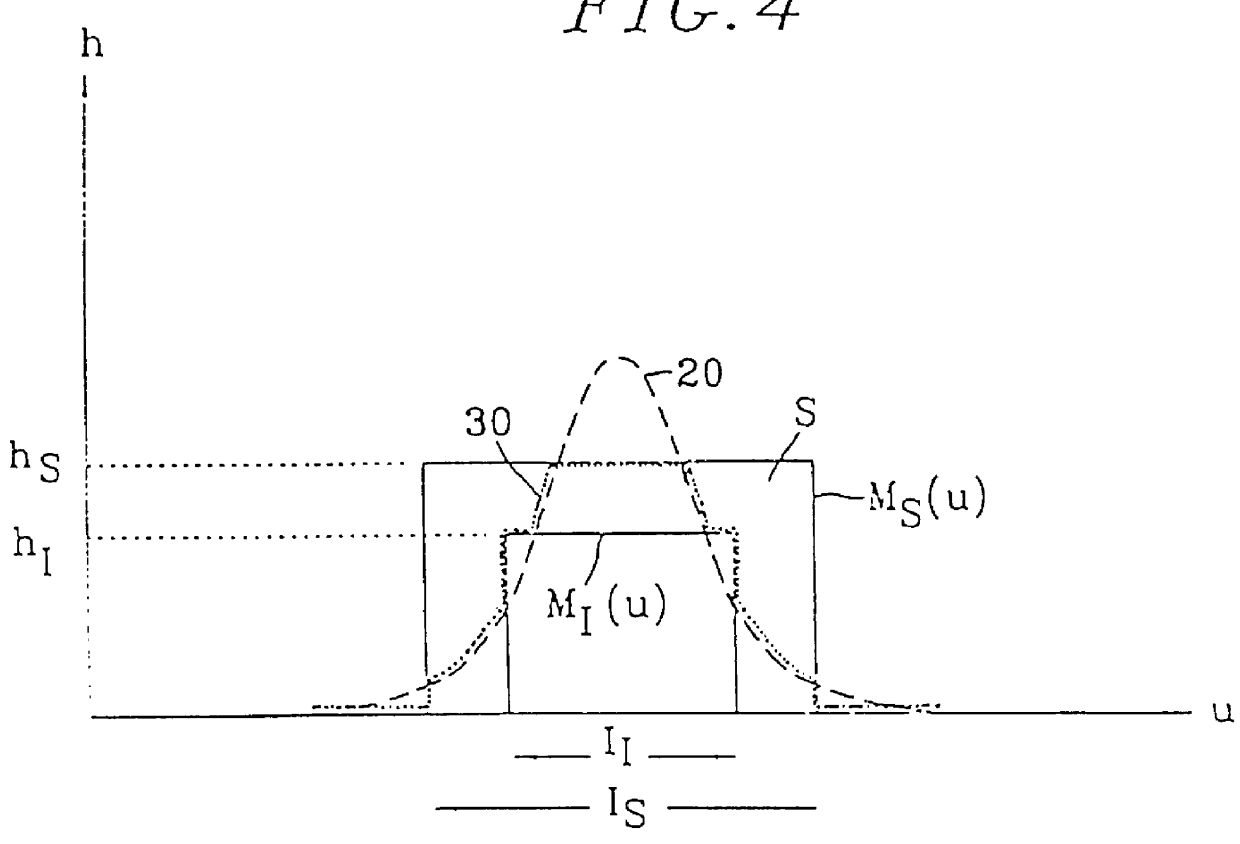

The present invention relates to a multiplexer and / or demultiplexer optical component of the waveguide array spectrograph type, wherein the waveguides are numbered in order of increasing optical path length, the optical path lengths of the waveguides describing a function of waveguide number which varies about a mean linear function, a difference measured between said waveguide number function and said mean linear function describing a difference function not limited to a set of two linear functions, said difference function being suitable for giving the optical component a spectral response that is square in shape.

Owner:FRANCE TELECOM SA

Data analysis system and method

ActiveUS7289857B2Automatic detectionBuildData processing applicationsSimulator controlMonitoring systemData analysis system

Data from a monitoring system is analyzed for monitoring characteristics of a dynamic system. Characteristic data in respect of a dynamic system is monitored and provided with at least one known normal state. Characteristic data is received from a monitoring system and confirmation information from an operator when the dynamic system is in a known normal state. A normality model is derived including comprising data indicative of known normal states in response to received characteristic data and confirmation information. Future characteristic data is predicted from the normality model a difference function is provided indicating an acceptable difference between predicted and received characteristic data. Predicted characteristic data is compared with received characteristic data in conjunction with the difference function and an abnormality signal is produced if the difference exceeds the difference function.

Owner:BRITISH TELECOMM PLC

Method, system and computer program product for producing a raised relief map from images of an object

A method for obtaining a model of an object surface from a plurality of images of said object, wherein the object is illuminated with one or more illumination sources, the method comprising: —obtaining a set of images each comprising an array of pixels and representing similar views of an object, wherein the similar views are obtained under different illumination conditions; —defining a model function that expresses the known pixel intensity values of the images in terms of the following unknown model components: —a first model component (A) representing the albedo of the object at each pixel location and being the same for the plurality of images and being an albedo value; —a second model component (L) representing an intensity of illumination for each image and being an illumination source intensity value being the same for all pixels of each image; —a third model component (V) representing a specific illumination direction and being different for each image and being an illumination vector and being the same for all pixels of each image; —a fourth model component (N) representing surface normal directions of the object surface at each pixel position and being the same for all images and being a normal vector; —performing one or more sequences of minimization operations to minimize a difference function between the pixel values obtained from the set of images and pixel values calculated using said model function, each minimization operation being performed by allowing one of said model components (A, L, V, N) to vary while the others remain unchanged; —outputting the fourth model component (N) as said model of the object surface.

Owner:BIOMERIEUX SA

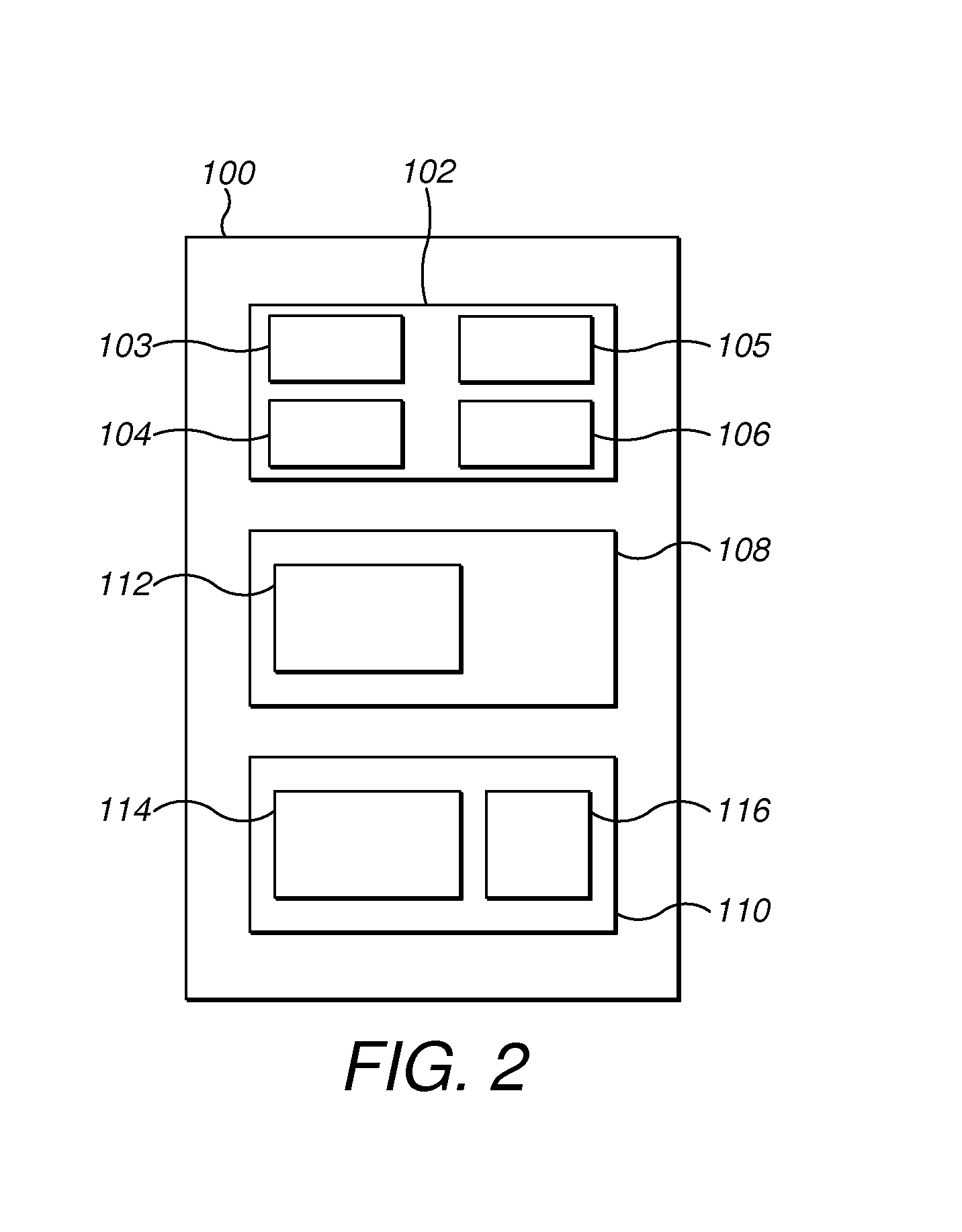

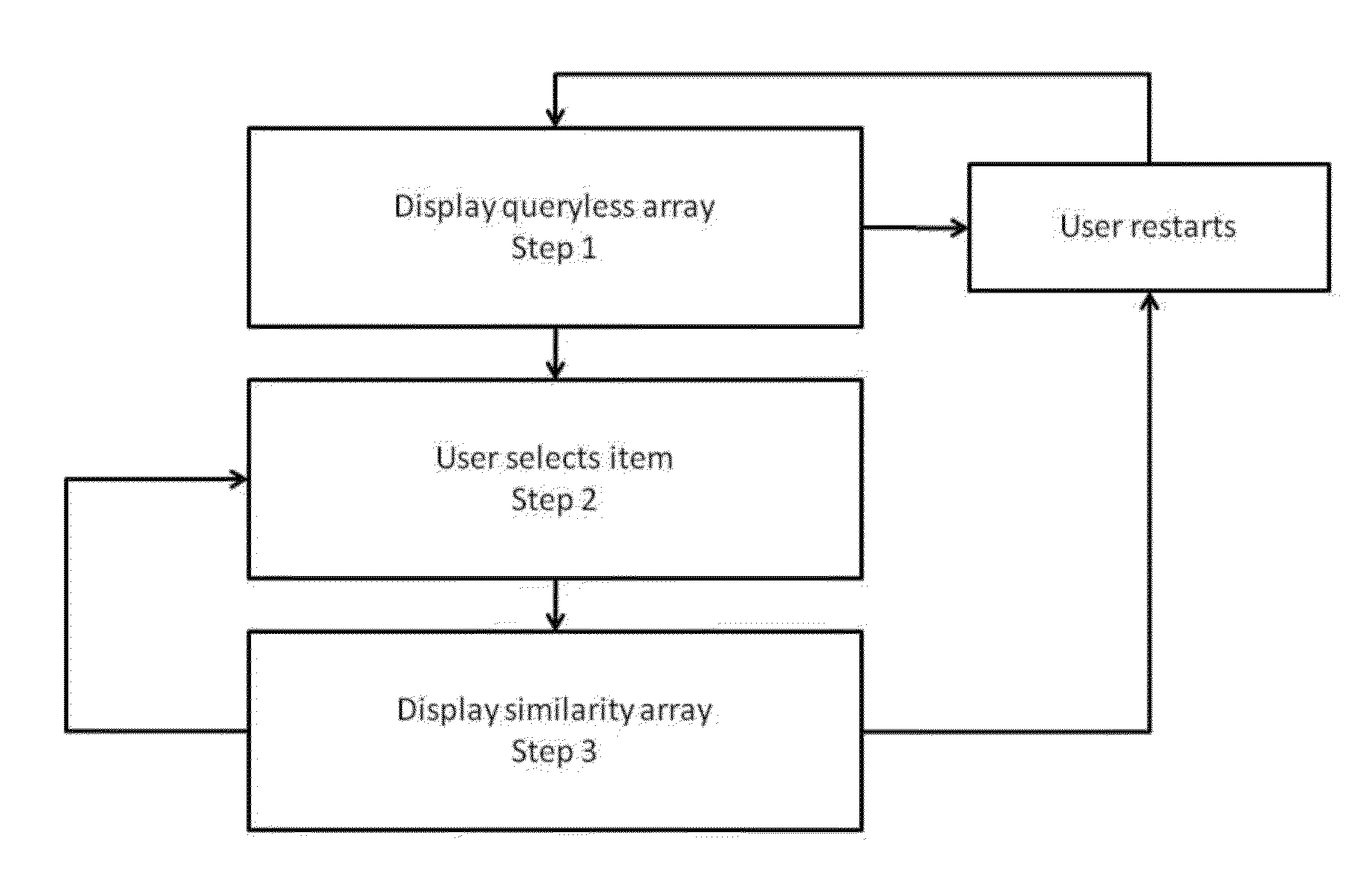

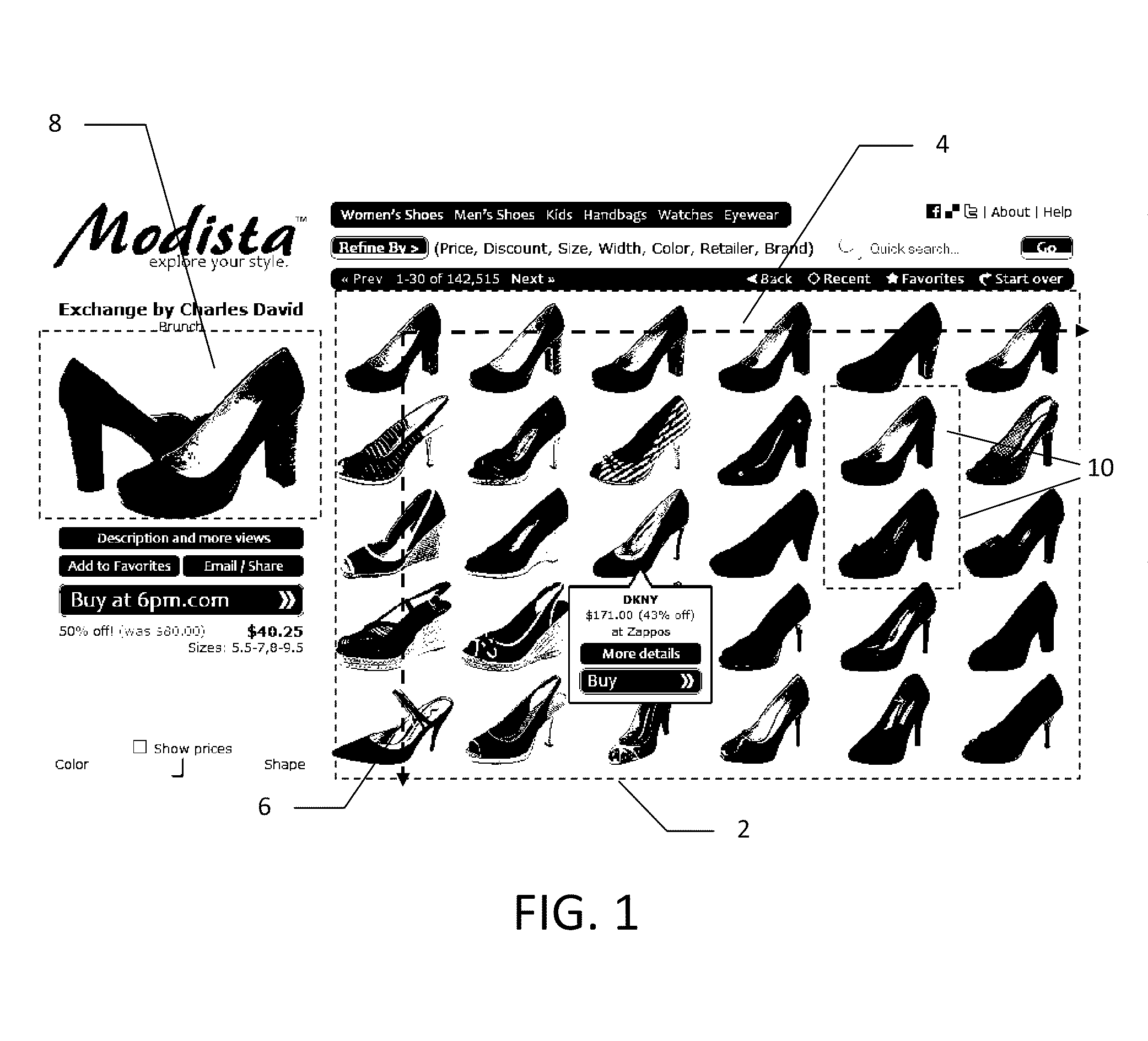

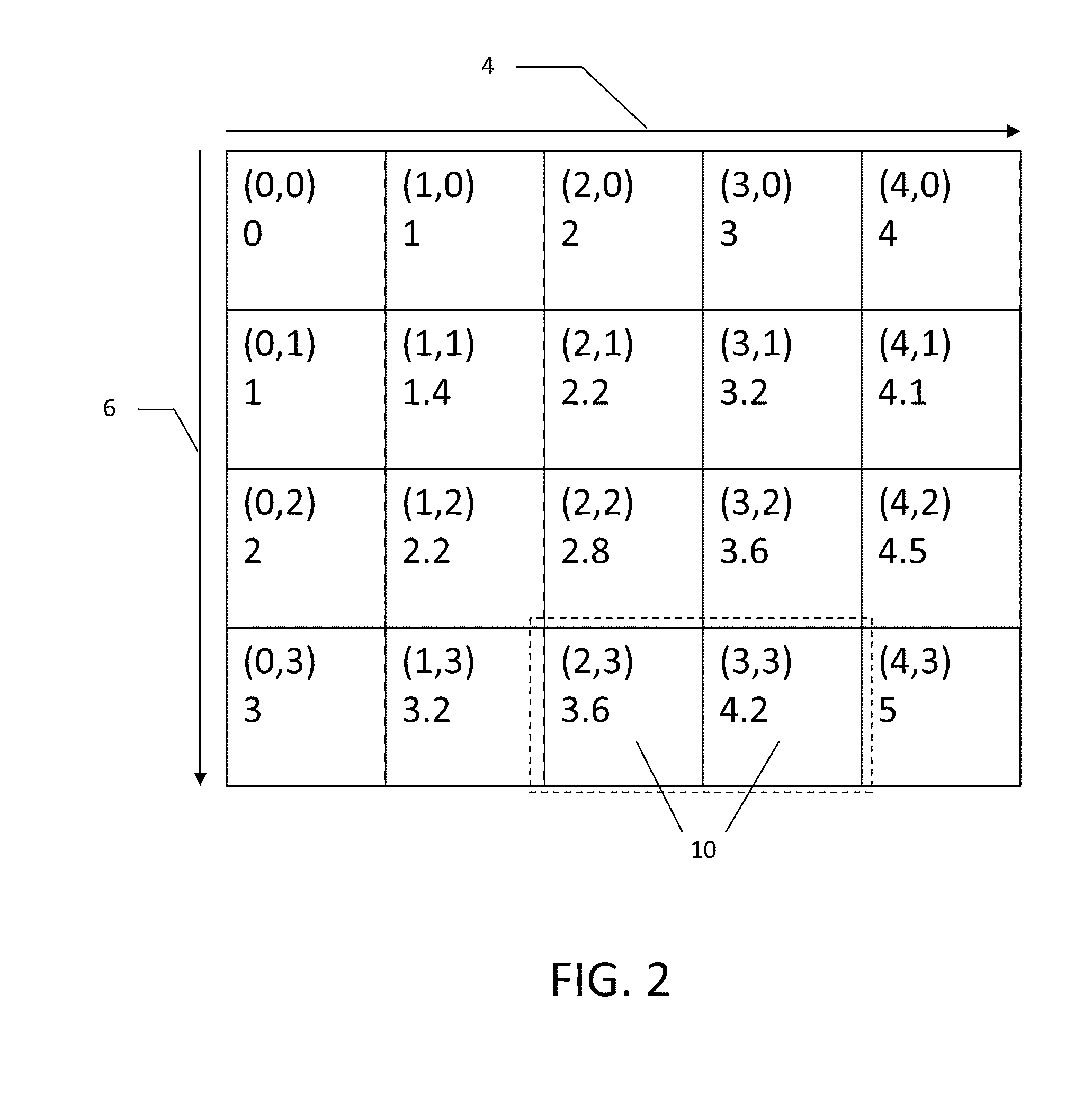

System And Method For The Structured Display Of Items

InactiveUS20100049707A1Metadata text retrievalDigital data processing detailsDiscrepancy functionPattern recognition

A system and method for displaying items by receiving a query, identifying query feature values for similarity features associated with the query, identifying items each having item feature values for similarity features thereof, for each of the identified items and for each of the similarity features, determining a feature distance between the query feature value and the item feature value, and presenting the identified items in a two dimensional array of cells. The array defines reference vectors corresponding to the similarity features. The identified items are positioned within the array relative to the origin cell, for any of the cells, by determining difference function values. for the identified items each based on the feature distances of the item, the reference vectors and the coordinates of the cell, and placing one of the items in the cell based upon the determined difference function values.

Owner:UGMODE

Optical disc drive and objective lens for the same

InactiveUS20070014211A1Inhibit deteriorationImprove recording densityRecord information storageOptical beam guiding meansLight beamLength wave

There is provided an objective lens used for three types of optical discs including by selectively using one of three types of light beams. At least one of surfaces of the objective lens is provided with a first region converging the third light beam on a recoding surface of the third optical disc. The first region has a step structure configured to have concentric refractive surface zones and to give an optical path length difference to an incident beam at each step formed between adjacent refractive surface zones. The step structure is configured such that the optical path length difference given by each step is substantially equal to an odd multiple of a wavelength of a first light beam, and a value of differentiation of an optical path difference function defining the step structure crosses zero in a height ranging from 30% to 70% of an effective diameter of the first region.

Owner:HOYA CORP

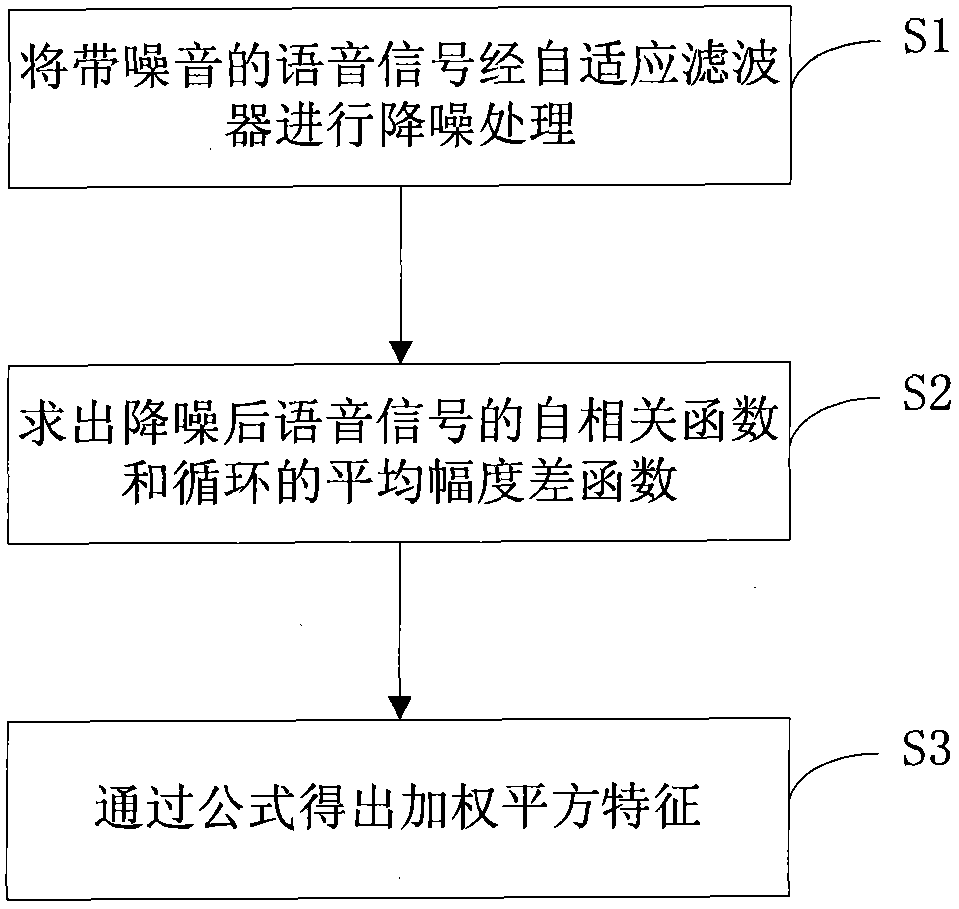

Algorithm for estimating pitch period of voice signal

InactiveCN102737645AEfficient detectionReduce complexitySpeech recognitionAdaptive filterSignal-to-noise ratio (imaging)

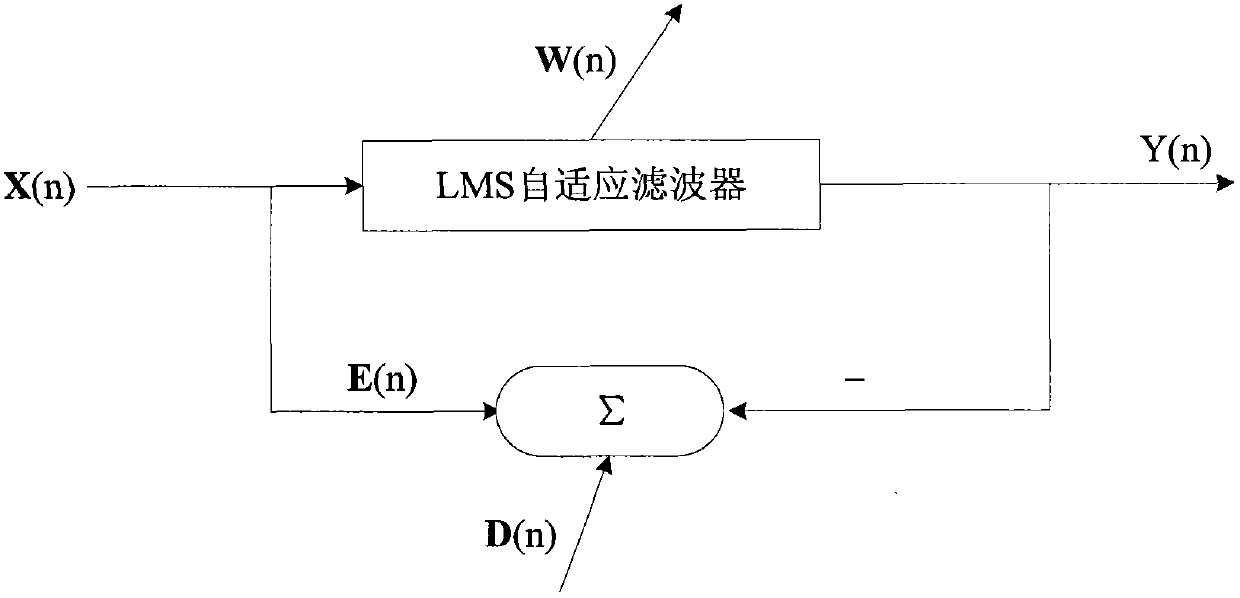

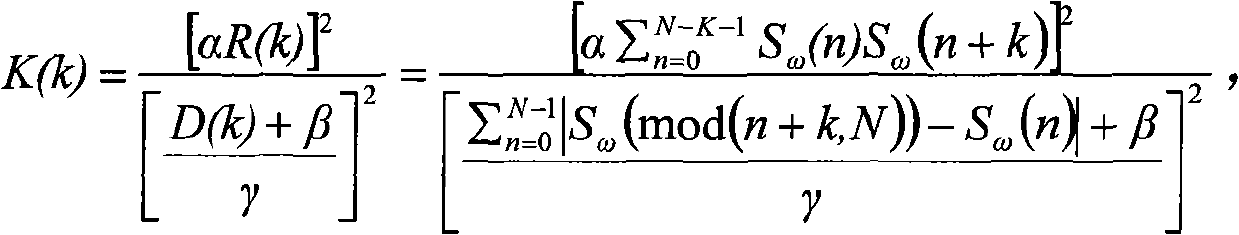

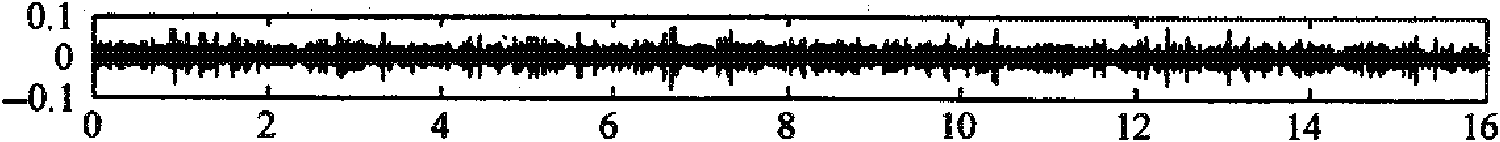

The invention discloses an algorithm for estimating a pitch period of a voice signal and relates to the field of voice signal processing. The algorithm comprises the following steps of: 1, denoising a voice signal with noise through an adaptive filter; 2, determining a self-correlation function of the denoised voice signal and a cyclic average magnitude difference function; and 3, obtaining a weighted square characteristic value through a formula, wherein alpha, beta and gamma are constants which are respectively more than 1, R (k) is the self-correlation function, and the D (k) is the average magnitude difference function. By the algorithm, the pitch period can be effectively detected in the environment with a low signal to noise ratio, the extraction errors are reduced, octave or semioctave errors are reduced, the estimation accuracy of a pitch is improved when the algorithm is sensitive to change of an amplitude or frequency of the voice signal, and the robustness is high.

Owner:WUHAN TIANYU INFORMATION IND

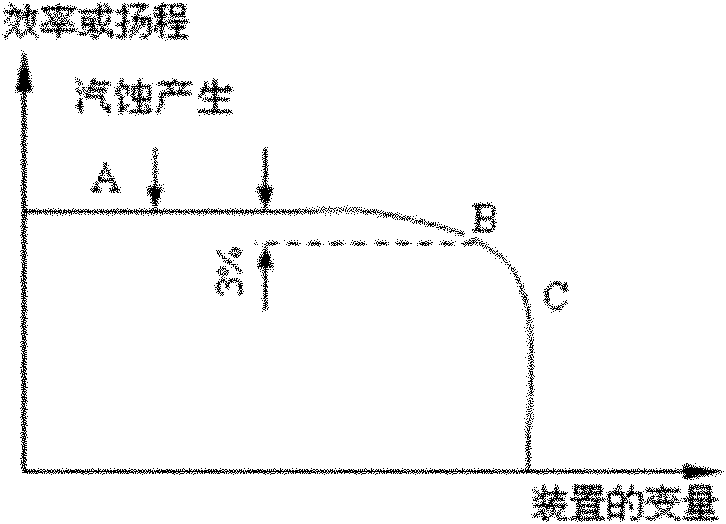

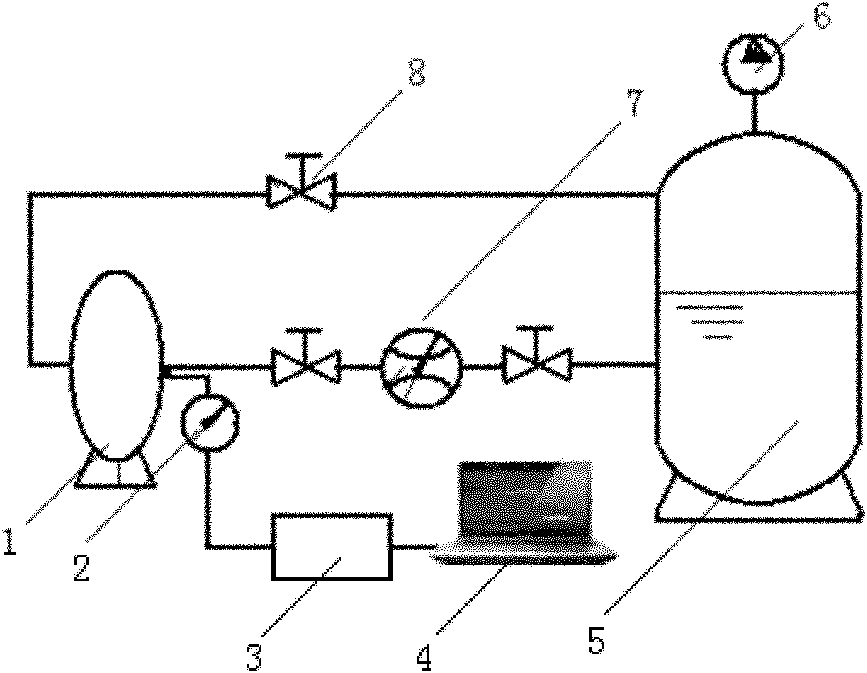

Water pump cavitation measuring method

InactiveCN102022348AImprove certaintyGrasp cavitation performancePump controlNon-positive displacement fluid enginesCavitationDecomposition

The invention discloses a water pump cavitation measuring method. For an eccentric water pump, a fluid pressure fluctuation signal acquired in a certain time period at the pump inlet is subject to EMD (empirical mode decomposition) so as to obtain an IMF (intrinsic mode function) component with different frequency components, thus further identifying whether cavitation occurs. The water pump cavitation measuring method comprises the following steps: assigning the fluid pressure fluctuation signal to an intermediate function; constructing an upper-lower envelope curve function by using all local maximum values and local minimum values of the intermediate function; obtaining an average envelop function and a difference function between the intermediate function and the average envelop function; judging whether the difference function meets the IMF condition of an intrinsic mode signal; if the difference function meets the IMF condition, obtaining an IMF component; otherwise, updating the intermediate function with the difference function, repeating the processes until the IMF components are obtained; and updating the intermediate function with the remaining components, and repeatingthe processes again until enough IMF components are obtained. By using the water pump cavitation measuring method, the cavitation measurement determinacy is improved, and the basis is laid for water pump re-design and prevention of further fault development.

Owner:BEIHANG UNIV

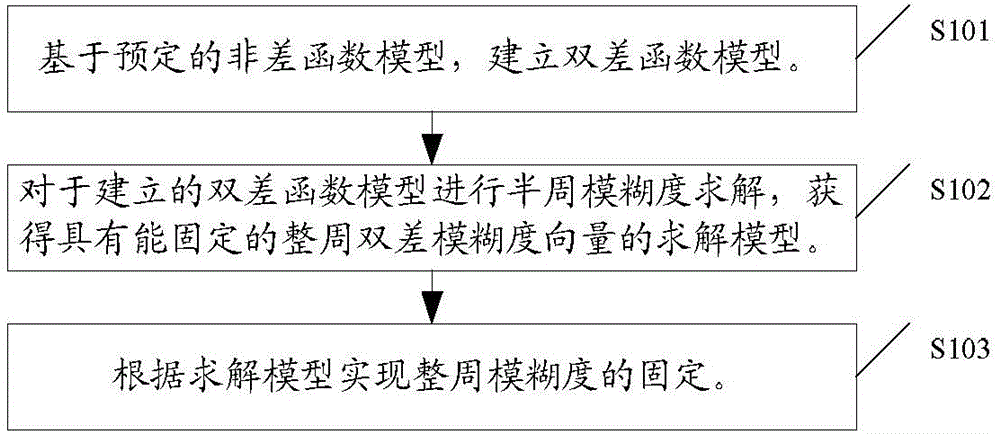

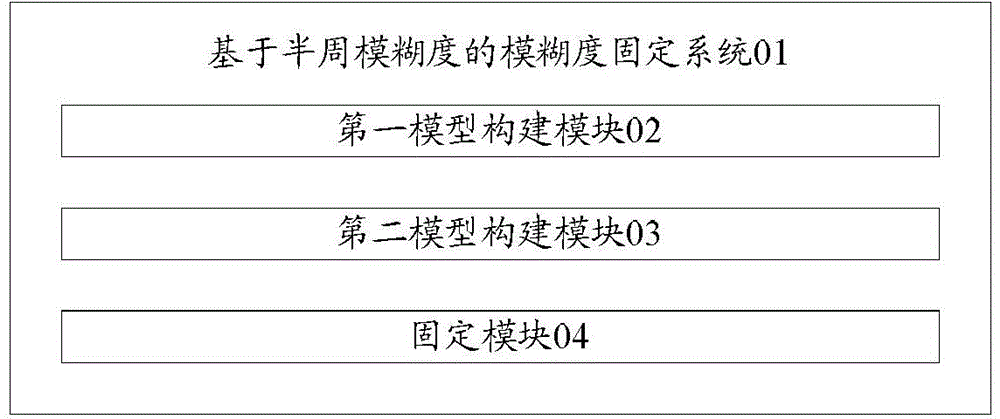

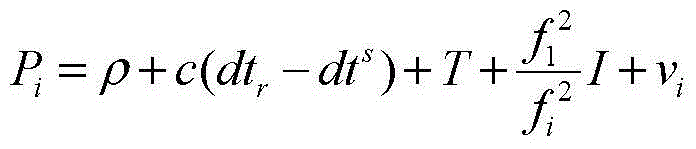

Ambiguity fixing method and system based on semi-cycle ambiguity

The present invention discloses an ambiguity fixing method and system based on semi-cycle ambiguity. The method comprises establishing a double difference function model based on a predetermined non-difference function model; performing semi-cycle ambiguity solution on the established double difference function model, and converting a semi-cycle-containing ambiguity vector into a whole cycle ambiguity vector through conversion, so as to obtain a resolving model having a fixable whole-cycle double-difference ambiguity vector; and realizing fixation of whole cycle ambiguity according to the resolving model. Through the above scheme, as for the real-time kinematic (RTK) technology, fixation of the ambiguity is completed before polarity judgment is completed, and the RTK initialization time is shortened.

Owner:UNICORE COMM INC

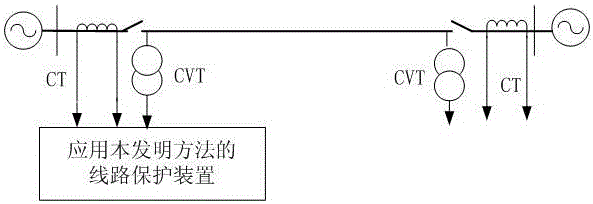

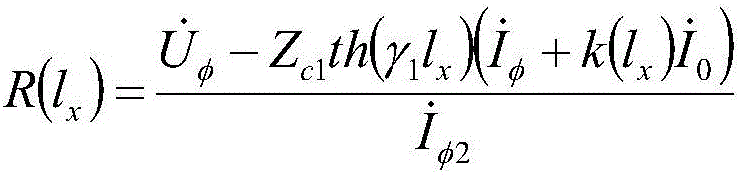

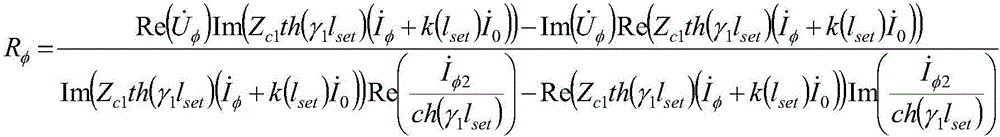

Range finding method for single-phase earth fault of line based on actual measurement of transition resistance

ActiveCN105891669AImprove ranging accuracyPracticalFault location by conductor typesPhase currentsCapacitance

The invention discloses a range finding method for a single-phase earth fault of a line based on actual measurement of transition resistance. The method includes the steps of measuring fault phase voltage, fault phase current, fault phase negative sequence current and zero sequence current at the protective installation part of a power transmission line, describing the physical characteristics of voltage and current transmission of the power transmission line by using a distributed parameter model, calculating the transition resistance at the single-phase earth fault point of the power transmission line, and sequentially calculating the transition resistance and transition resistance difference function value of each point on the power transmission line by using a one-dimensional searching method. Accurate range finding for the single-phase earth fault of the power transmission line is realized by using the characteristic that the transition resistance difference function value at the fault point of the power transmission line reaches the minimal value, which theoretically eliminating the influence of the factors including distribution capacitance, transition resistor and load current, and ensuring high range finding precision. The method is a searching method which means no false solution problem of equation solving methods and misconvergence problems of iterative methods, and the method is highly practical.

Owner:STATE GRID FUJIAN ELECTRIC POWER CO LTD +2

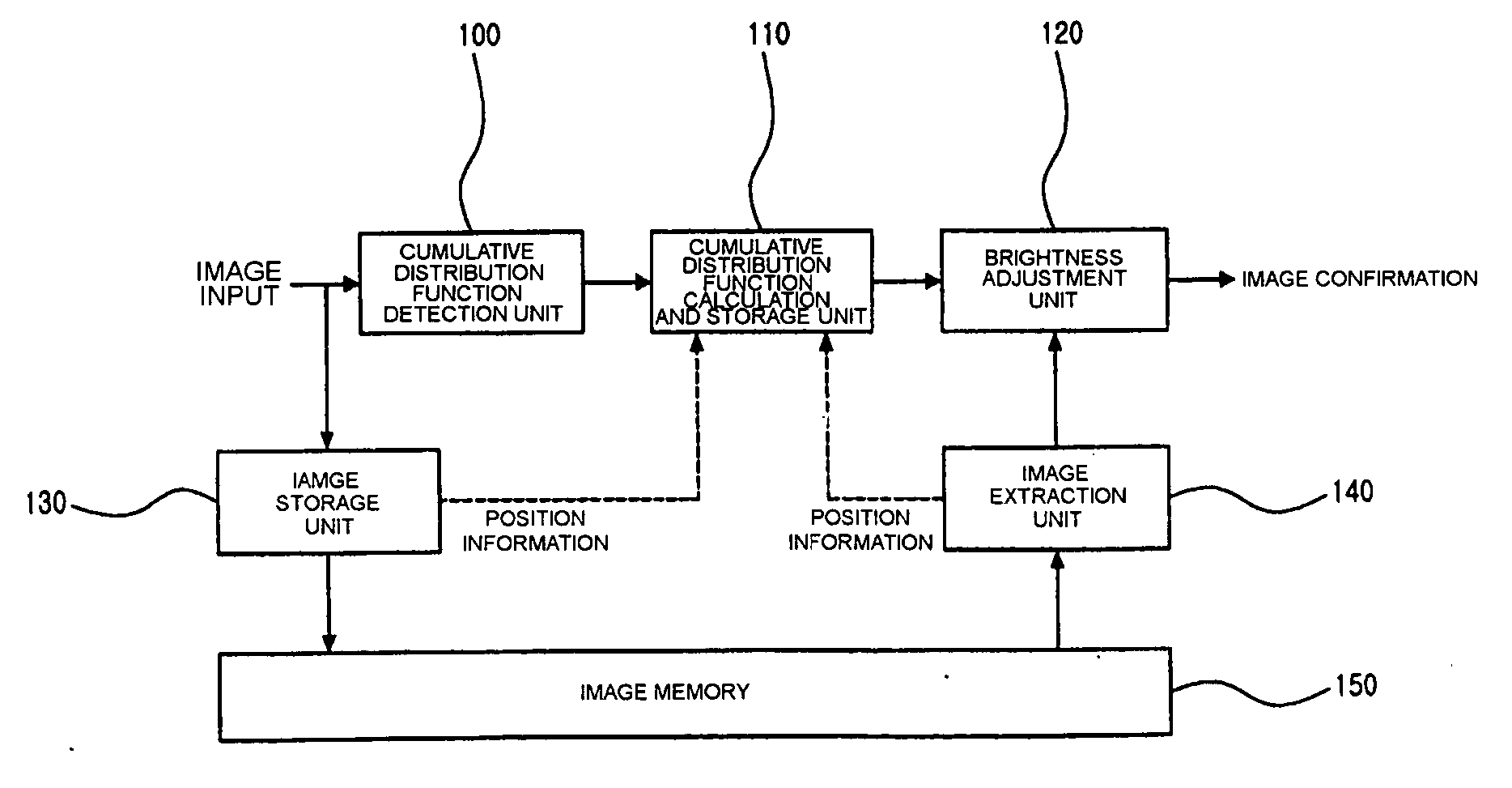

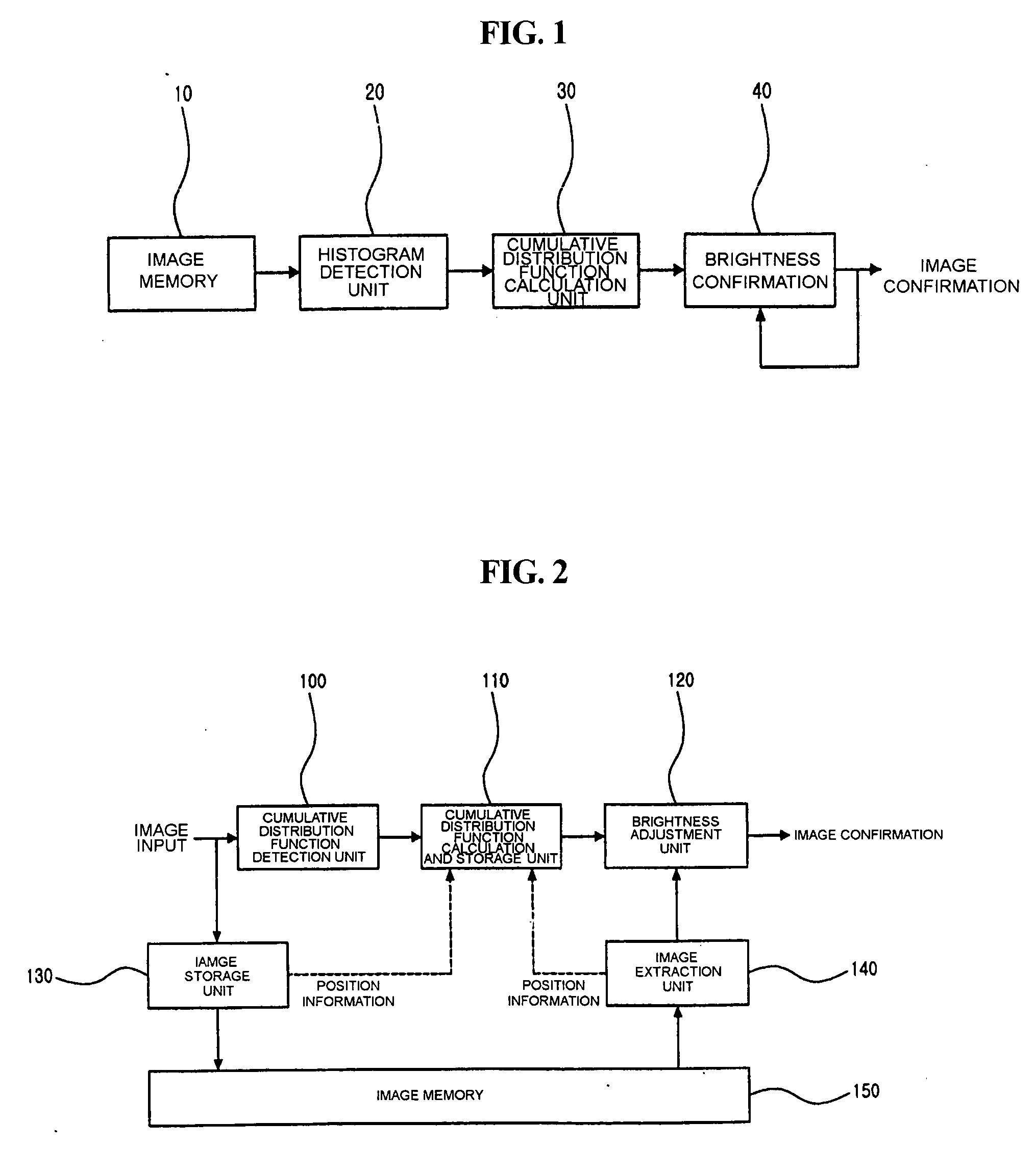

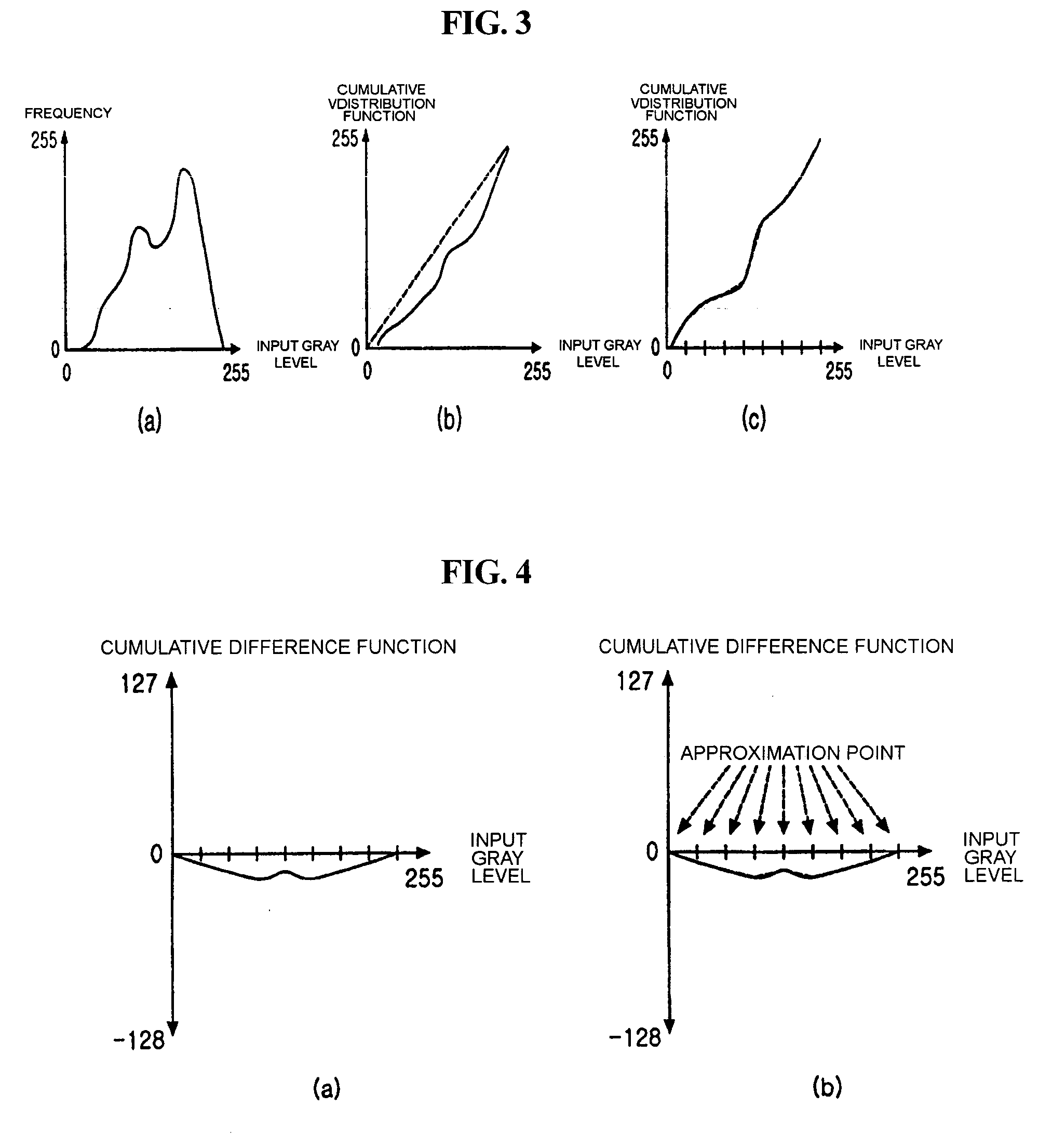

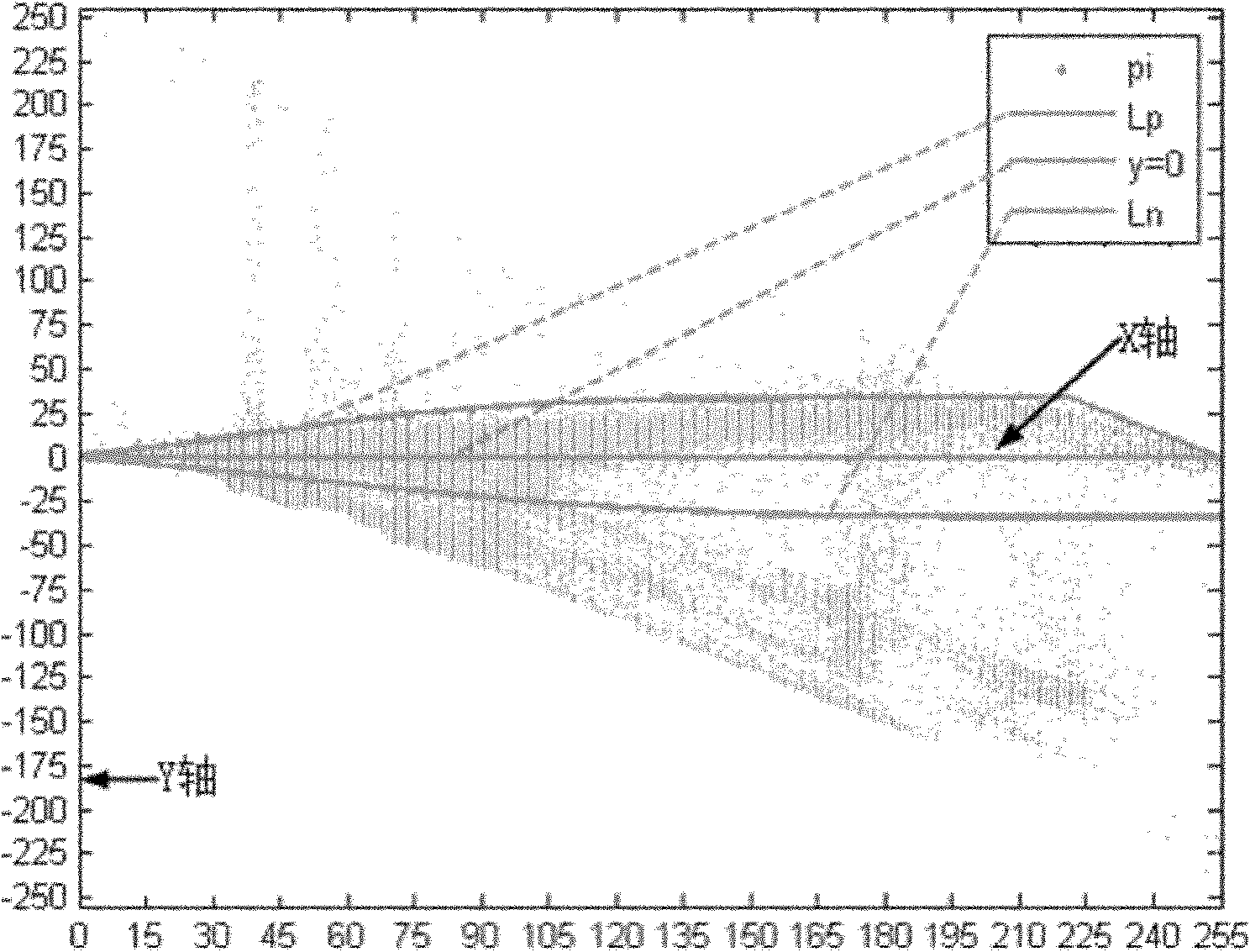

Apparatus and method for controlling brightness of moving image signals in real time

InactiveUS20050002565A1Reduce amountReduce the amount requiredImage enhancementTelevision system detailsImaging processingDifference function

The present invention relates to an image processing apparatus, which calculates the histogram of an image on the basis of moving image information that is input in real time, and corrects and outputs the brightness of the image using the histogram in real time. The apparatus for controlling the brightness of moving image signals according to the present invention includes a cumulative difference function detection means, an image storage means and a brightness adjustment means. The cumulative difference function detection means calculates a cumulative difference function using upper n bits of each input image. The image storage means stores therein the input image. The brightness adjustment means adjusts the brightness of the image in real time using the cumulative difference function calculated by the cumulative difference function detection means when the input image stored in the image storage means is displayed.

Owner:EDTECH

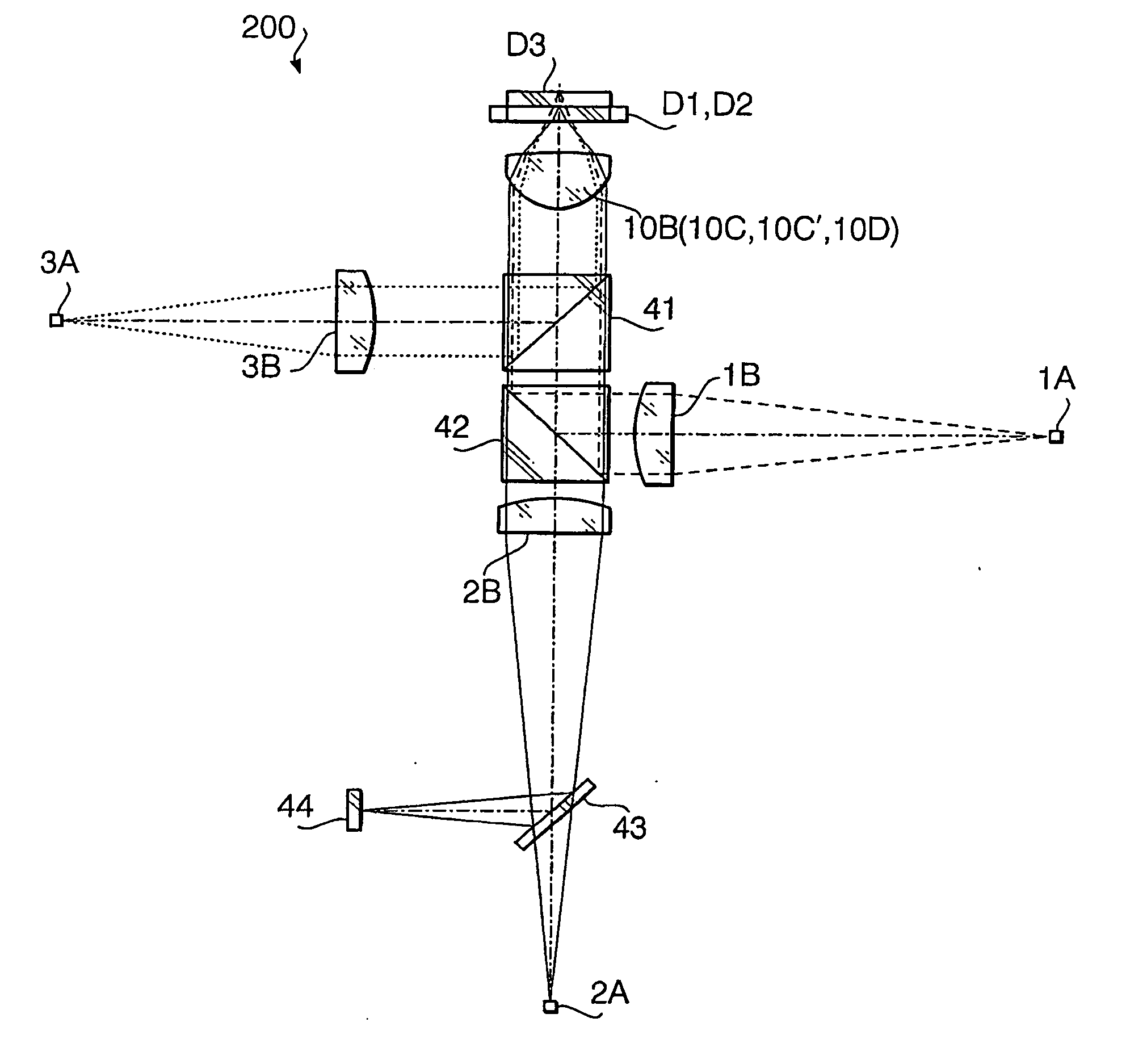

Optical pickup apparatus, condensing optical system, and optical element

InactiveUS20040264348A1Optical beam sourcesRecord information storageOptical pickupDiffraction effect

This invention is directed to an optical pickup apparatus, condensing optical system, and optical element which can at least reproduce and / or record information from / on a first optical information recording medium having a protective substrate thickness t1 by using a light beam of a first wavelength lambda1 emitted from a first light source, and reproduce and / or record information from / on a second optical information recording medium having a protective substrate thickness t2 (t2>=t1) by using a light beam of a second wavelength lambda2 (lambda2>lambda1) emitted from a second light source. The optical pickup apparatus of the invention includes a first phase modulator which gives a diffraction effect to only the light beam of the wavelength lambda1 on at least one optical surface, of a plurality of optical surfaces of a plurality of optical elements arranged on a common optical path through which the light beam of the first wavelength lambda1 and the light beam of the second wavelength lambda2 pass, and a second phase modulator which gives a diffraction effect to only the light beam of the wavelength lambda2 on at least one of the remaining optical surfaces. Each of the first phase modulator and second phase modulator has staircase-like discontinuous parts, each formed from a predetermined number of stepped portions, formed concentrically around an optical axis at the pitch defined by an optical path difference function.

Owner:KONICA MINOLTA OPTO

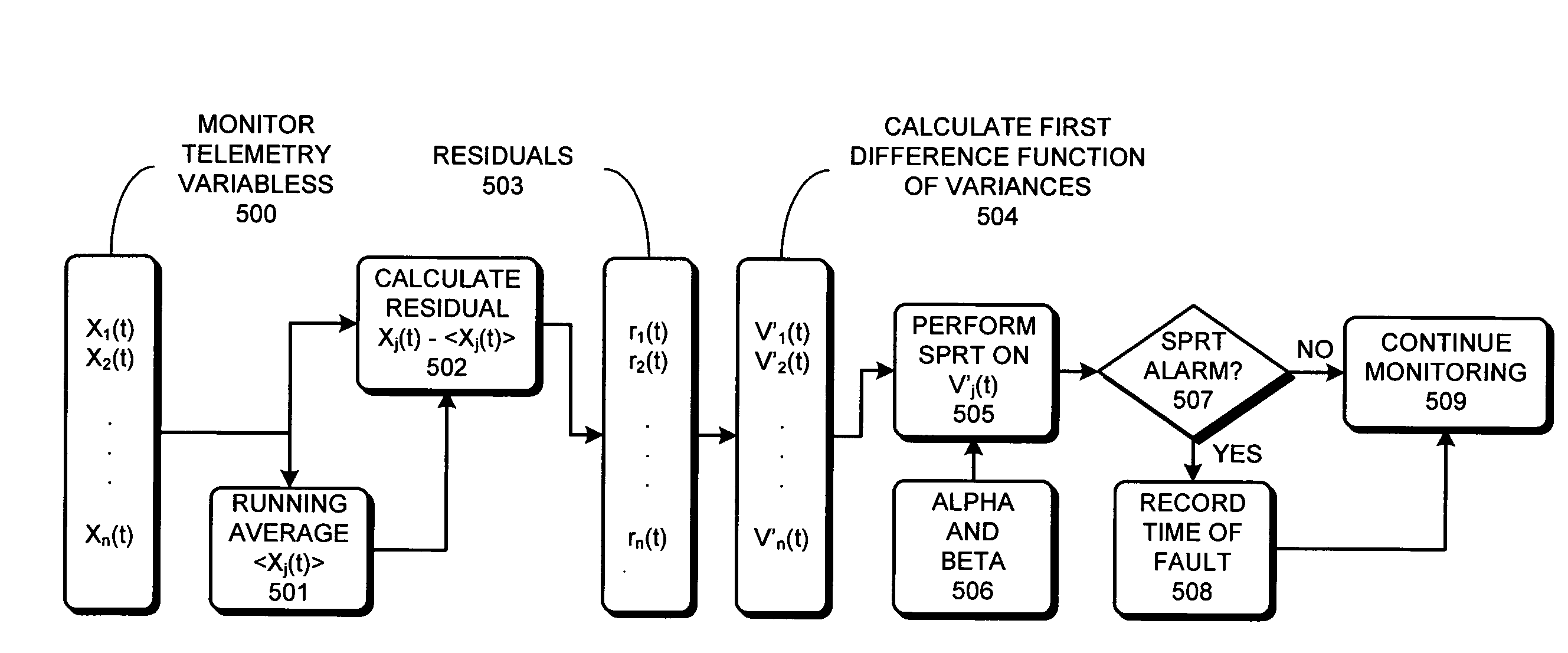

Method and apparatus for monitoring the health of a computer system

A system that monitors the health of a computer system is presented. During operation, the system receives a first-difference function for the variance of a time series for a monitored telemetry variable within the computer system. The system then determines whether the first-difference function indicates that the computer system is at the onset of degradation. If so, the system performs a remedial action.

Owner:ORACLE INT CORP

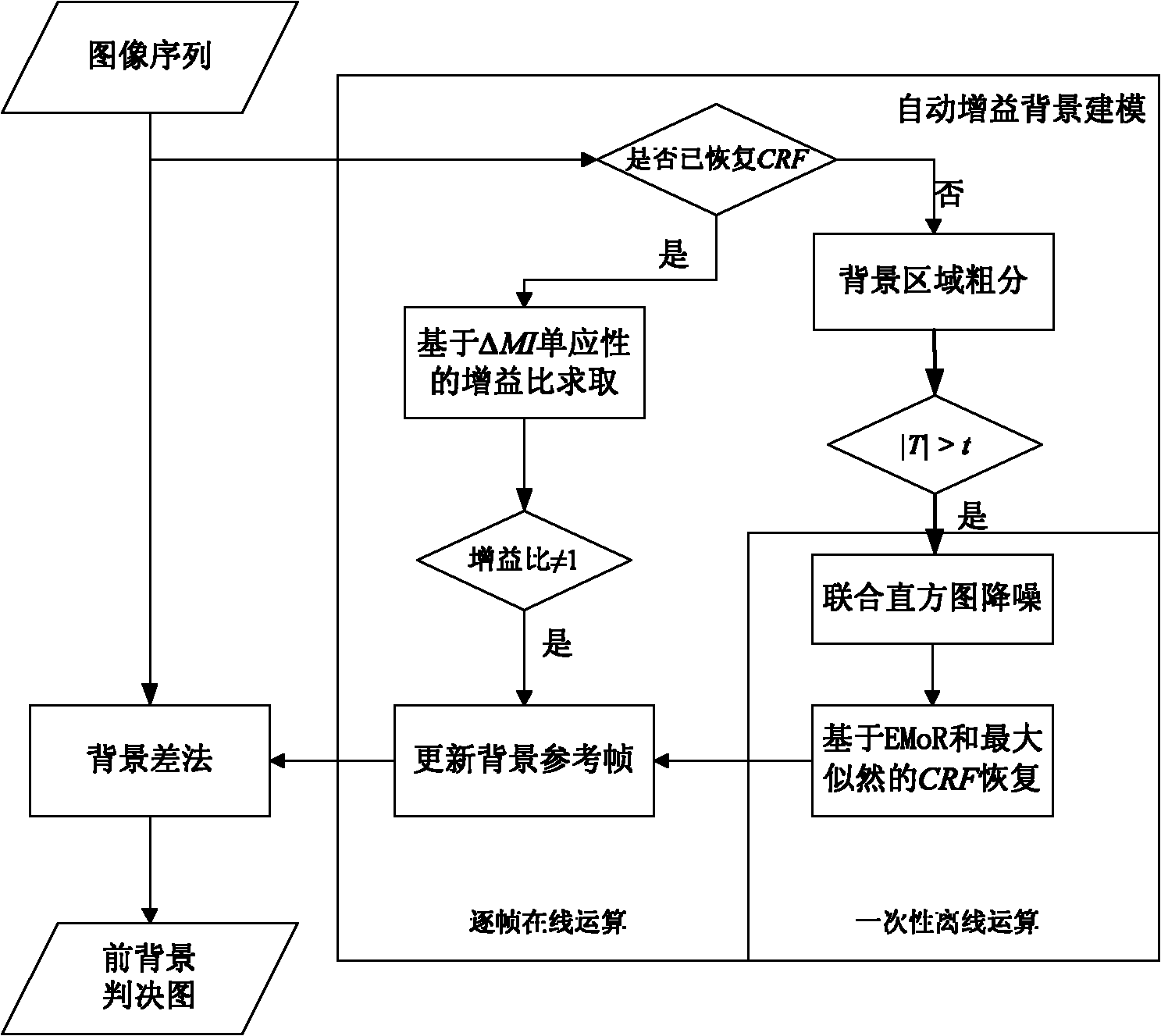

Method for modeling background based on camera response function in automatic gain scene

InactiveCN102129689AImprove general performanceReduce adverse effectsImage enhancementTelevision system detailsLow noiseCamera response function

The invention discloses a method for modeling a background based on a camera response function in an automatic gain scene, which comprises the following steps of: performing automatic gain progressiveness-based analysis to obtain a roughly divided background area, obtaining low-noise training data by using a joint histogram method, and performing recovery once to obtain a globally optimal camera response function by the method based on maximum likelihood estimation and parameter constraints; online calculating a gain ratio frame by frame by utilizing correlation between a foreground and background difference and the gain ratio and the homography of a grayscale difference function relative to the gain ratio; and if the gain ratio is not 1, performing updating to obtain a background reference frame the same as a current reference frame by using the camera response function and the gain ratio, otherwise determining the background reference frame is unchanged, and obtaining the background reference frame with a gain coefficient the same as that of the current frame along with the change of the gain coefficient of a camera. By the method, the shortcomings of high background change speed, caused by difficulties in realizing automatic gain along with the camera, of the conventional methods are overcome, thereby ensuring high-efficiency motion detection.

Owner:NANJING HUICHUAN IND VISUAL TECH DEV

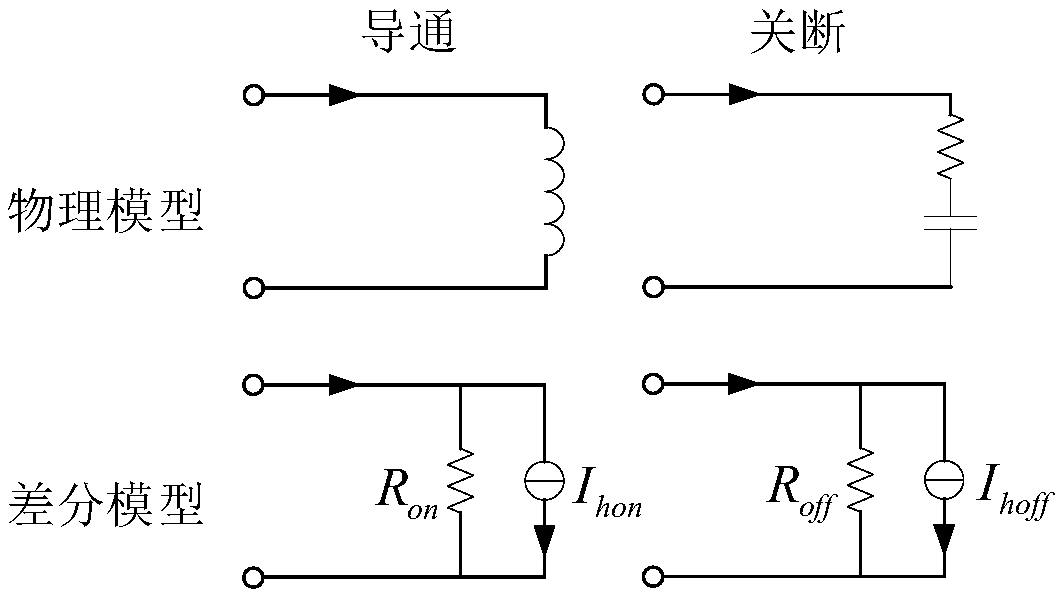

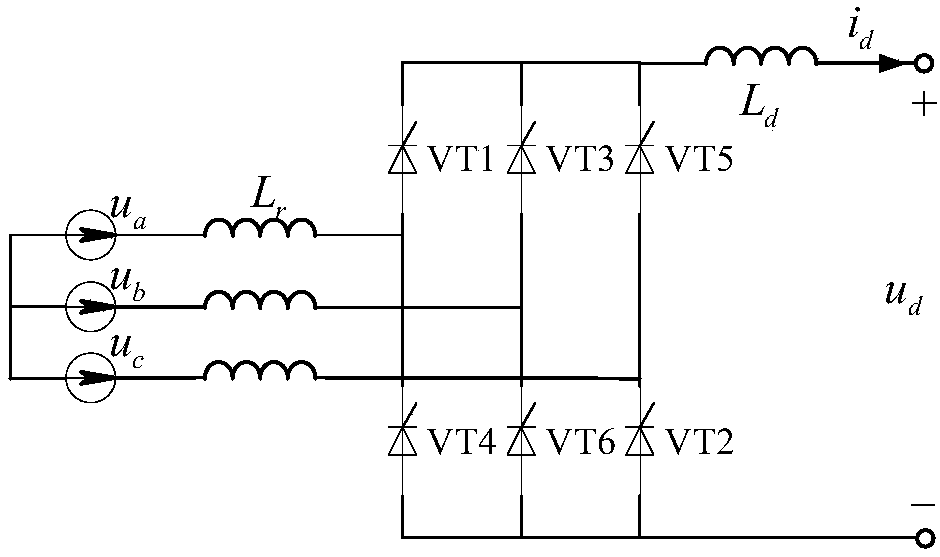

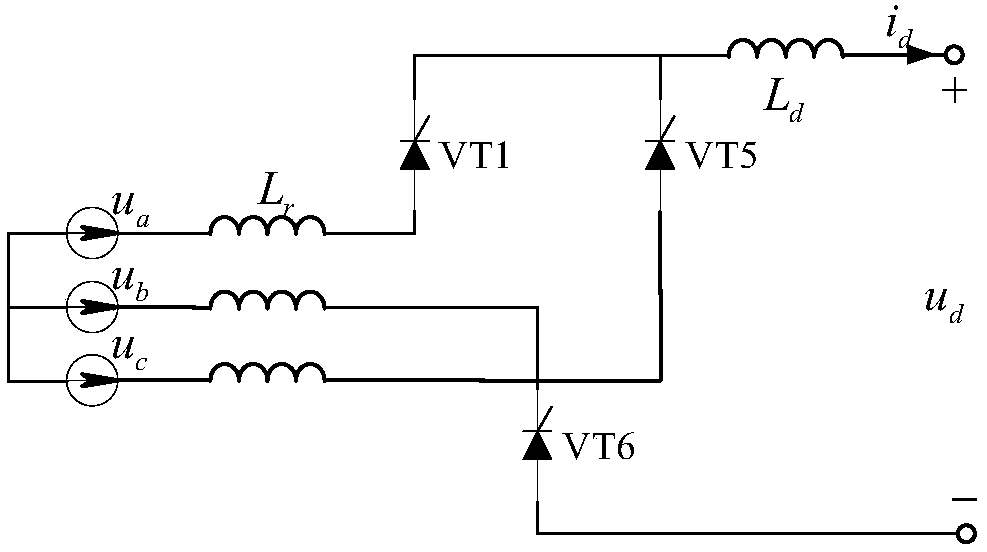

LCC-HVDC simulation model and parameter optimization method based on inductance/capacitance switch model

ActiveCN108536949AAvoid the problem of multiple inversionsDesign optimisation/simulationSpecial data processing applicationsCapacitanceModel parameters

The invention discloses a LCC-HVDC simulation model and parameter optimization method based on an inductance / capacitance switch model. An inductance / capacitance effective switch is used for LCC-HVDC modeling and simulation of a six-pluse rectification system; according to the working state of each thyristor, an instant-switching transient response, a steady state response and switching loss are obtained after analysis when the inductance / capacitance effective switch and an ideal switch are in different working states; a minimized difference function of the effective switch and the ideal switchserves as an optimal object, and model parameter optimization is achieved so that the inductance / capacitance effective switch can be approximate to the ideal switch. According to the LCC-HVDC simulation model and parameter optimization method, in the process that a power system containing a large amount of LCC-HVDC is simulated, admittance matrixes of the whole system cannot be changed along withthe on-off state of a switch original, the problem of multiple times of inversion of a large quantity of matrixes is solved accordingly, and large system simulation efficiency is improved.

Owner:SHANGHAI JIAO TONG UNIV