Accelerating core virtual scratch pad memory method based on heterogeneous multi-core platform

A heterogeneous multi-core and memory technology, applied in the field of heterogeneous multi-core platform memory access optimization, can solve problems affecting the performance of heterogeneous multi-core platforms, limited data bus bandwidth, slow access speed, etc., to save SPM size and improve interaction speed , the effect of reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

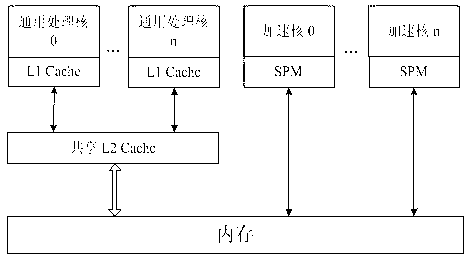

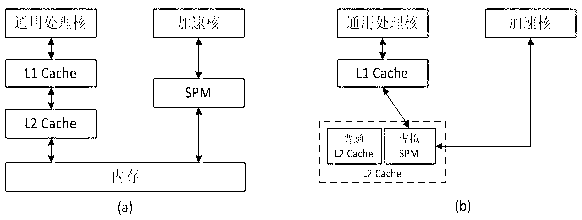

[0022] like figure 1 In the storage hierarchical architecture diagram of the heterogeneous multi-core platform shown, L1 Cache is the first-level cache of general-purpose processing cores, which is private to each general-purpose processing core; L2 Cache is the second-level cache, which is shared by all general-purpose processing cores, but Because the memory access characteristics of the accelerated core are very different from those of the general-purpose processing core, it does not participate in the shared L2 Cache; SPM is the abbreviation of Scratch Pad Memory, and SPM is used as the local memory of the accelerated core to store Generated local data, and acts as a cache between the accelerated core and memory.

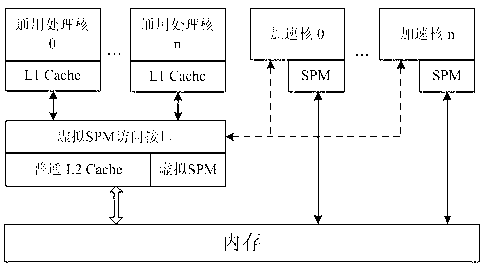

[0023] like figure 2 As shown, the present invention is figure 1 Based on the storage hierarchy in , make some optimizati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com