A kind of gate electrode and preparation method thereof

A gate electrode and gate oxide technology, applied in the field of gate electrode and its preparation, can solve the problems of large error of a single resistance, affecting the normal operation of a chip, uneven switching speed of the chip, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

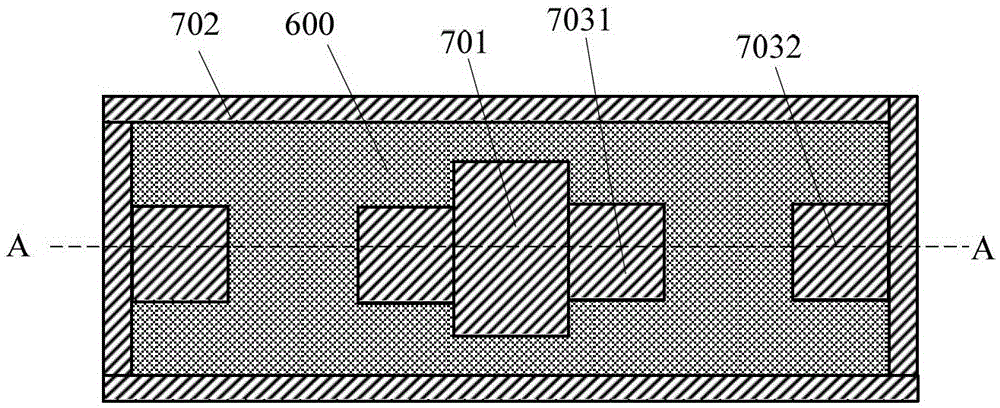

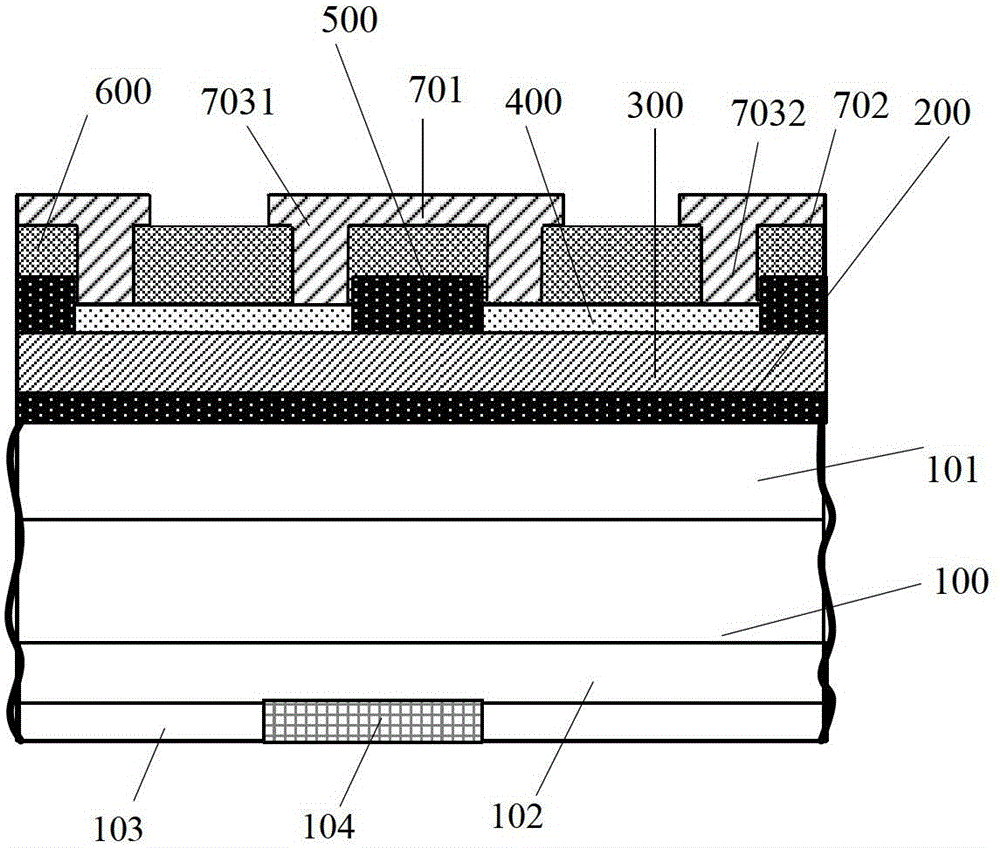

[0054] combine Figure 1 to Figure 2 The structure of the gate electrode in Embodiment 1 of the present invention will be described. figure 1 is the top view of the gate electrode, figure 2 is a cross-sectional view of the gate electrode along the direction A-A.

[0055] The gate electrode includes a substrate 100, a gate oxide layer 200 and a polysilicon layer 300 located on the substrate 100 in sequence, wherein the polysilicon layer 300 includes a first region and a second region, and the division of the first region and the second region is determined according to the layer structure above the polysilicon layer 300, and the second region includes at least a subregion surrounding the first region. It can also be understood in this way that the first area is embedded in the second area. The first region includes at least two discontinuous sub-regions.

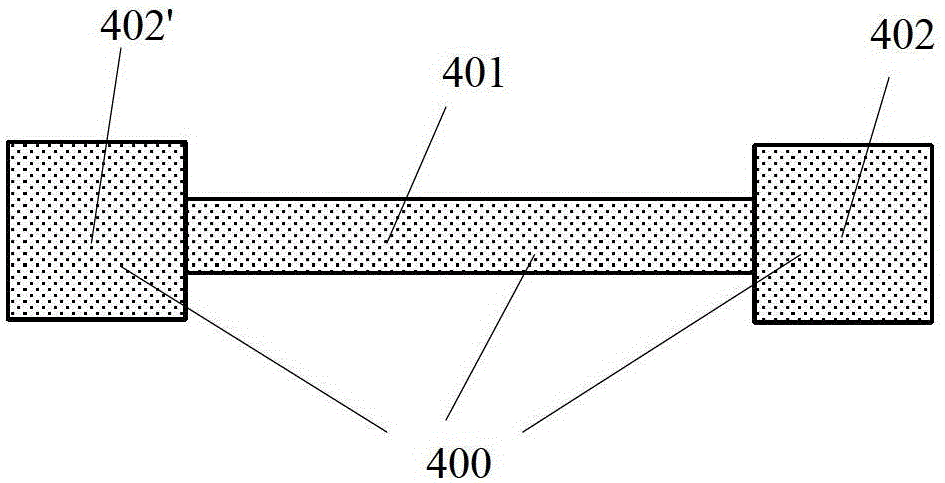

[0056] The gate electrode also includes a metal silicide layer 400 on the first region of the polysilicon layer 300 . ...

Embodiment 2

[0071] combine Figure 6 Referring to FIG. 7 ( 8 b ), the preparation method of the gate electrode provided by the embodiment of the present invention is described. The preparation method of the gate electrode comprises the following steps,

[0072] S61. Provide a substrate:

[0073] A substrate 100 is provided. Referring to FIG. 7 (1), the material of the substrate 100 can be a common silicon semiconductor material, or a wide bandgap semiconductor material such as silicon carbide, gallium nitride or diamond. The thickness range of the substrate is between 50-800 μm. The front surface of the substrate material has a first diffusion well 101, and the width of the first diffusion well is not smaller than the width of the gate electrode. The conductivity type of the first diffused well 101 is opposite to that of the substrate 100. The first diffused well is used to protect and prevent the depletion or even inversion of the gate electrode region in the reverse withstand voltag...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More