The method of using space redundancy to reduce the times of erasing and writing eeprom pages during transaction processing

A transaction processing and space redundancy technology, which is applied in the direction of memory address/allocation/relocation, etc., to achieve the effect of overcoming running speed and improving transaction processing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

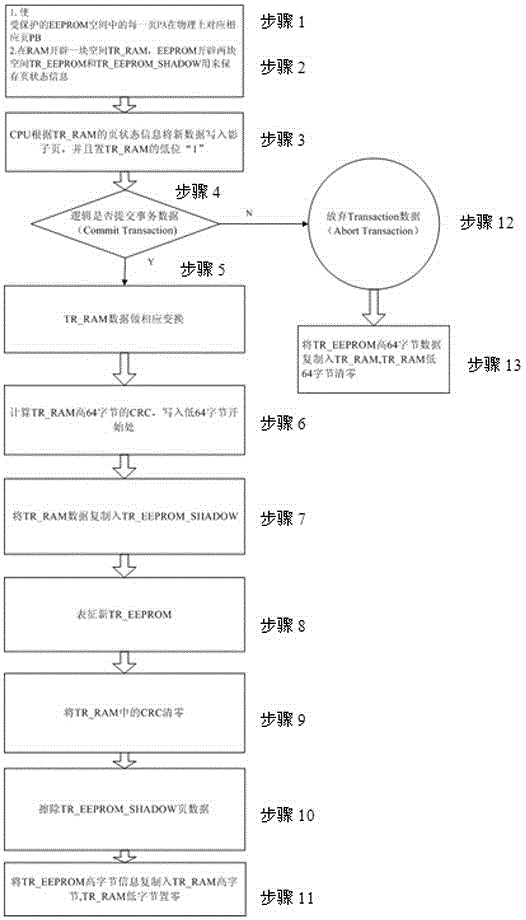

[0046] based on the following Figure 1 to Figure 6 , specifically explain the preferred embodiment of the present invention.

[0047] like figure 1 Shown, the present invention provides a kind of method utilizing space redundancy to reduce the number of erasing and writing times to EEPROM page in transaction process, comprises the following steps:

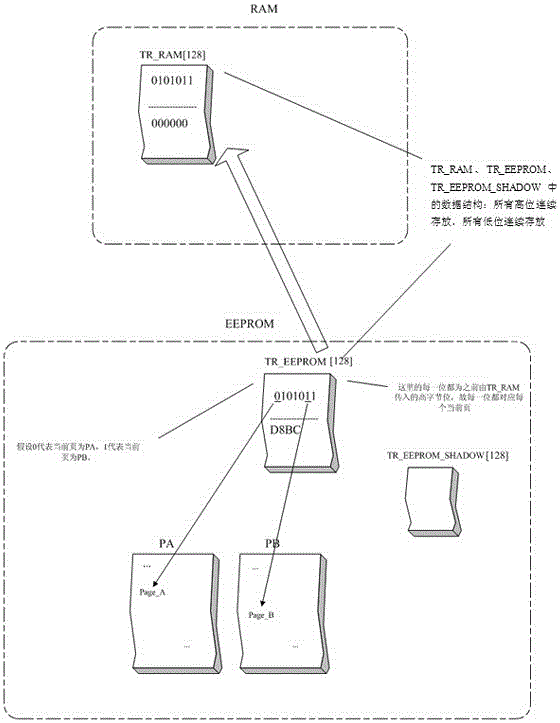

[0048] Step 1. Make each page in the space that needs to be protected by the transaction processing mechanism in the EEPROM physically correspond to two pages (PA and PB), one of which is used as the current page, and the other page is used as the shadow page;

[0049] Step 2, open up page state area TR_RAM in RAM, open up current page state area TR_EEPROM and page state shadow area TR_EEPROM_SHADOW in EEPROM respectively, be used to store page state information;

[0050] Use 2 bits to map the page status of EEPROM;

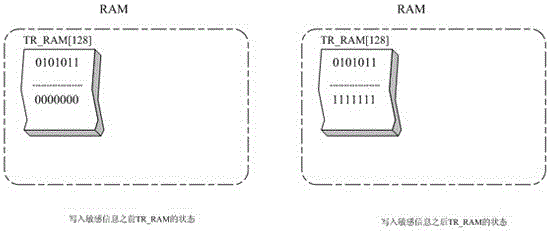

[0051] The status of each page is marked by two bits in the corresponding page status area TR_RAM, the "high bi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More