Conductive structure and method for forming the same

A technology of conductive structures and conductive bumps, applied in circuits, electrical components, semiconductor devices, etc., can solve problems such as uneven etching of metal layers and deformation of bumps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0063]The content of the present invention will be explained through the following examples. However, the descriptions in the examples are only for explaining the technical content of the present invention and its purpose and effect, and are not intended to directly limit the present invention. It should be noted that in the following embodiments and accompanying drawings, elements that are not directly related to the present invention have been omitted and not shown; and the dimensions and relative positional relationship of each element in the accompanying drawings are only for illustration to facilitate understanding, not for Limit implementation ratio and size.

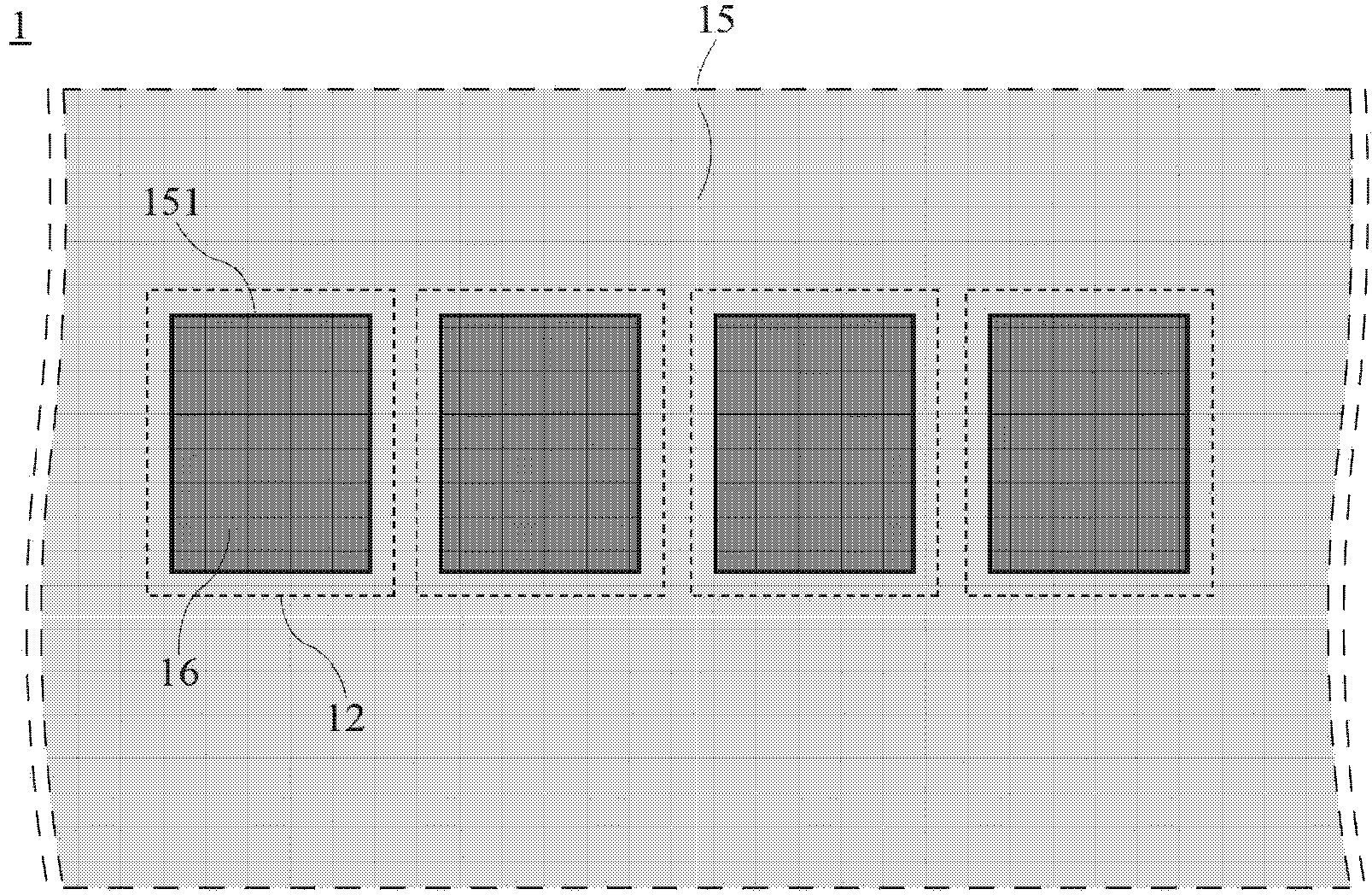

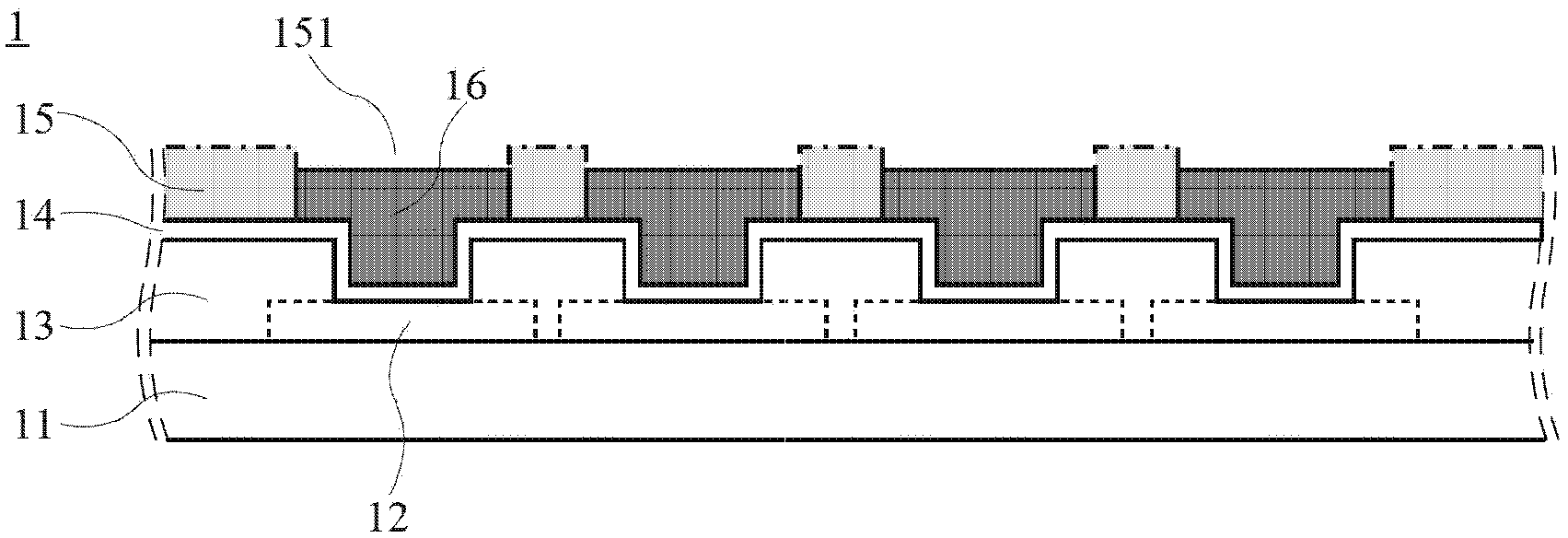

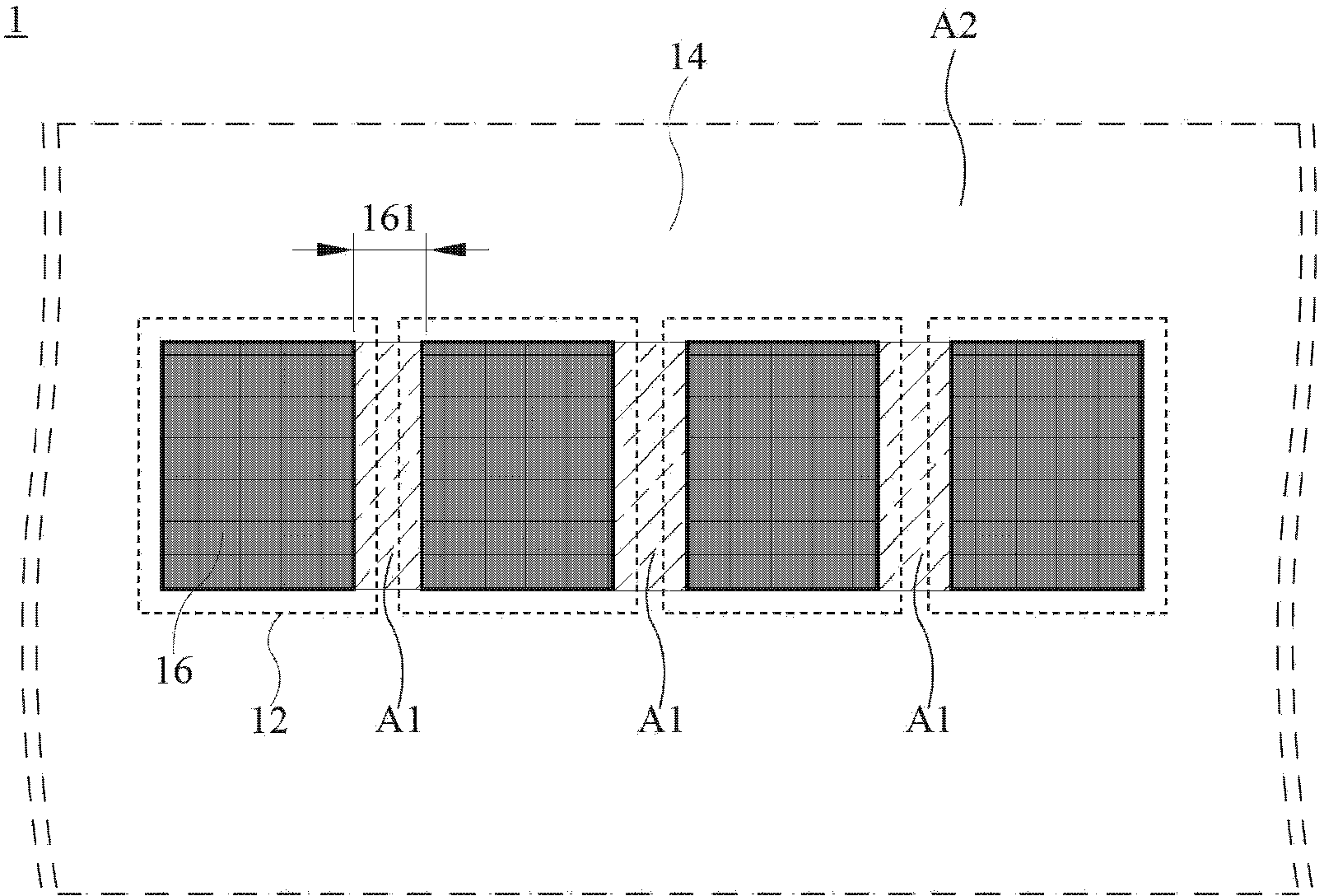

[0064] Figure 2A to Figure 2E and Figure 2A' to Figure 2E' The present invention is used in the schematic diagram of the conductive structure 3 of the first embodiment of a semiconductor chip 2 and its formation process, wherein Figure 2A to Figure 2E is a schematic top view of the conductive structure 3, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More