Wafer thinning method

A technology of wafers and fillers, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of reducing wafer area utilization, reducing wafer usage area, increasing process costs, etc. Wafer area utilization, avoidance of scratches and residues, the effect of simplifying the process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Embodiments embodying the features and advantages of the present invention will be described in detail in the following description. It should be understood that the invention can have various changes in different examples without departing from the scope of the invention, and that the descriptions and illustrations therein are illustrative in nature rather than limiting the invention.

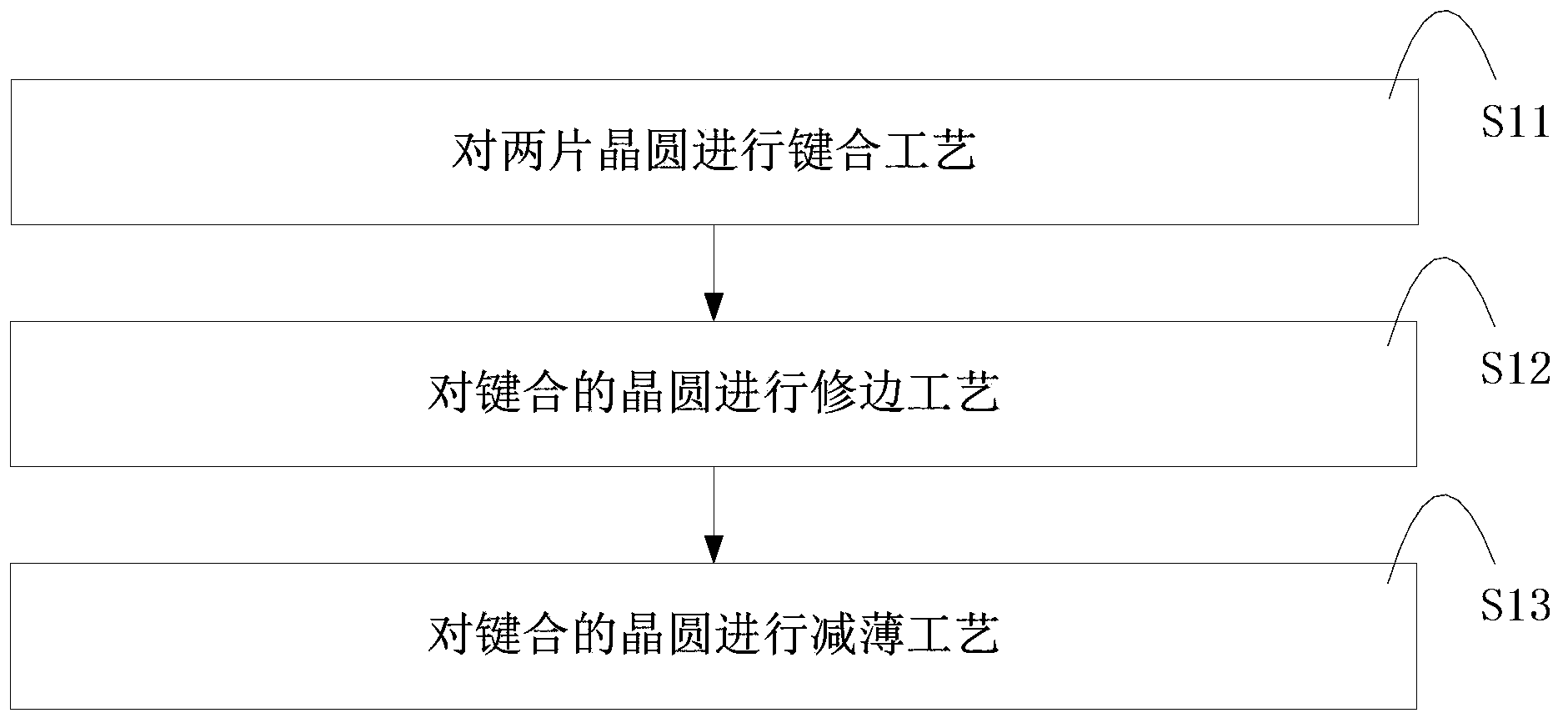

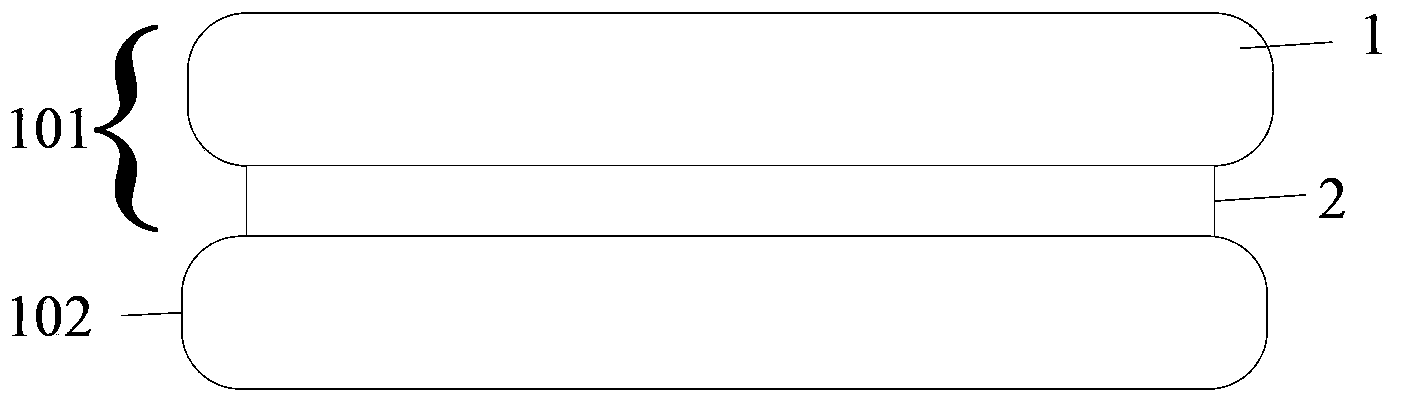

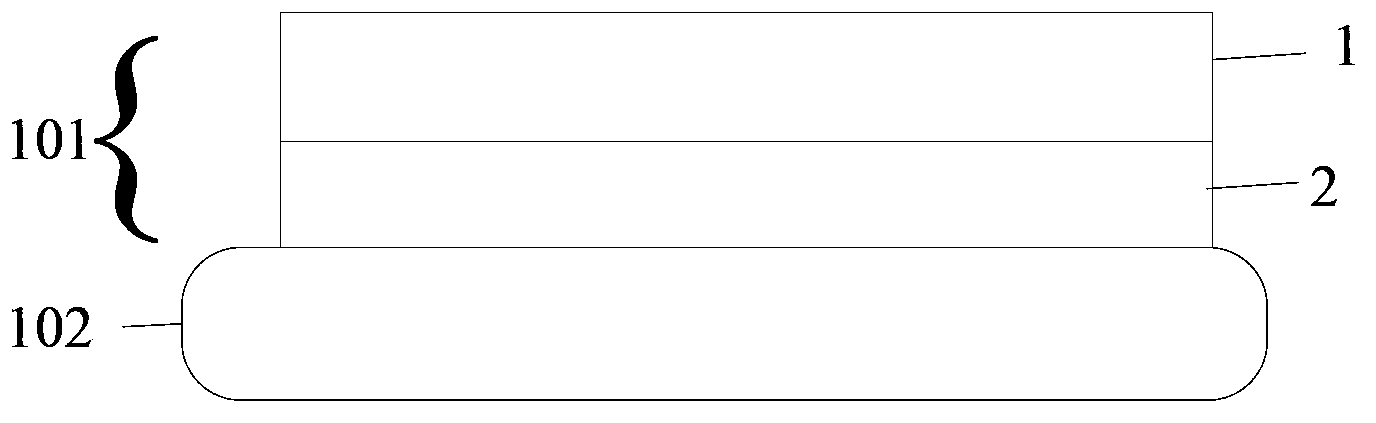

[0032] The following is attached Figure 5-11 , the wafer thinning method of the present invention will be further described in detail through specific embodiments. in, Figure 5 is a schematic flow chart of a wafer thinning method according to a preferred embodiment of the present invention, Figure 6-11 It is a schematic diagram of the cross-sectional structure formed by each preparation step of the wafer thinning method of the above-mentioned preferred embodiment of the present invention.

[0033] It should be noted that the drawings are all in a very simplified form, using imprec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More