Semiconductor device manufacturing method, and semiconductor device

A manufacturing method, semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as the method of using metal for the gate electrode that has not been proposed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

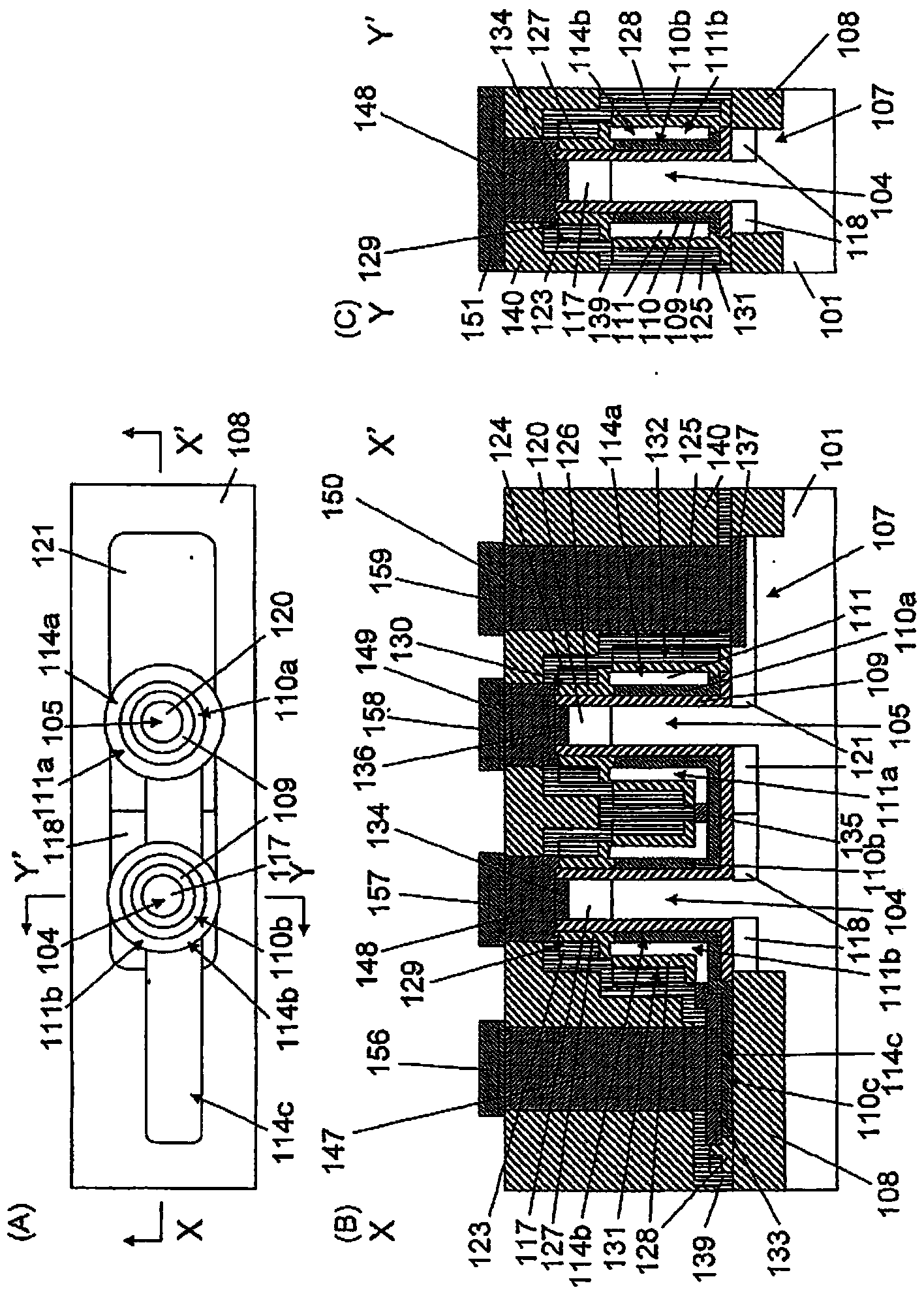

[0113] Below, refer to figure 2 (A), figure 2 (B), figure 2 (C)~ Figure 40 (A), Figure 40 (B), Figure 40 (C) The manufacturing steps of the semiconductor device having the SGT structure according to the embodiment of the present invention will be described.

[0114] Hereinafter, the first step is shown, that is, forming a planar silicon layer 107 on the silicon substrate 101 , and forming the first columnar silicon layer 104 and the second columnar silicon layer 105 on the planar silicon layer 107 .

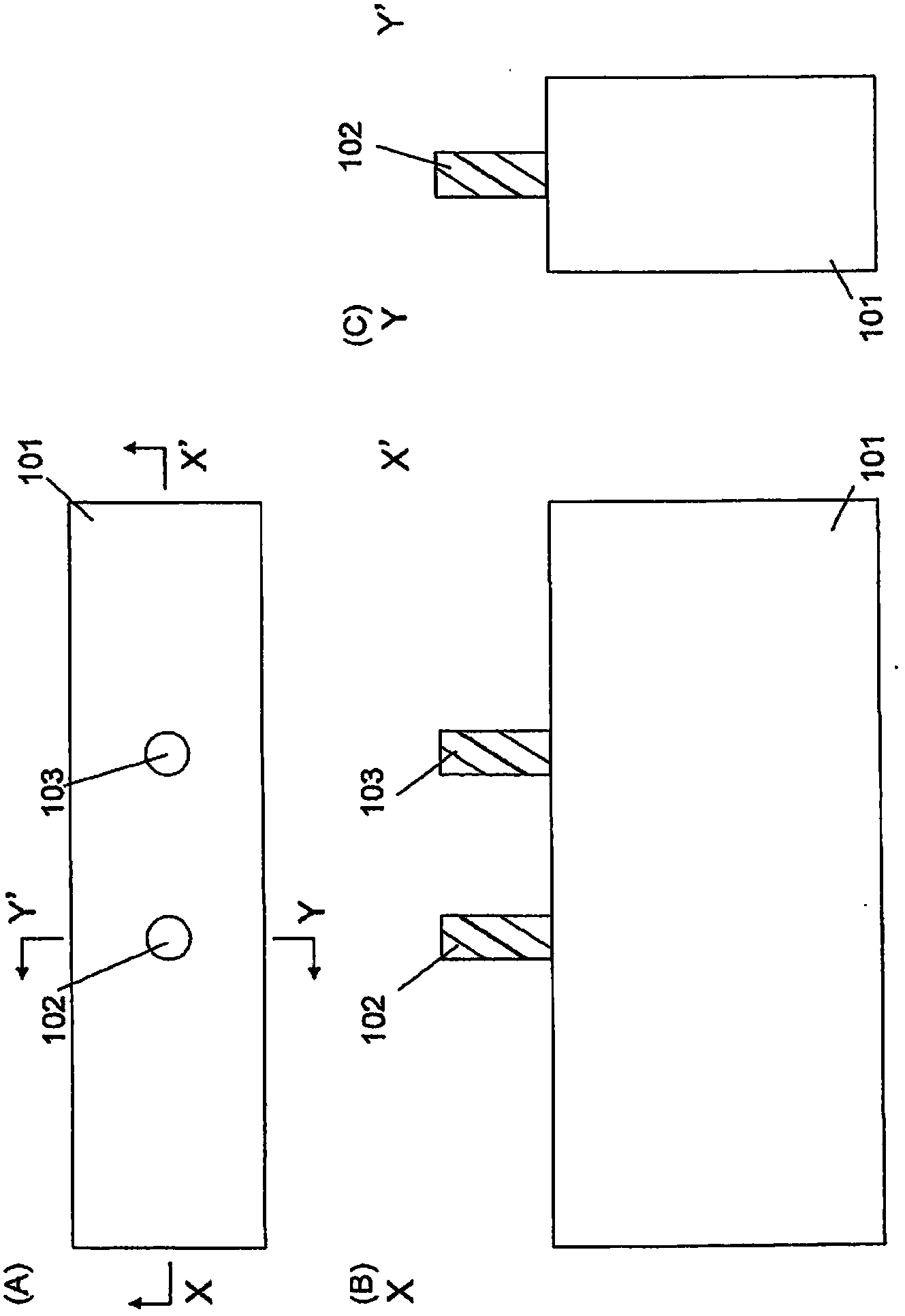

[0115] First, if figure 2 (A), figure 2 (B), figure 2 As shown in (C), the first resists 102 and 103 are formed on the silicon substrate 101 for forming the first columnar silicon layer 104 and the second columnar silicon layer 105 .

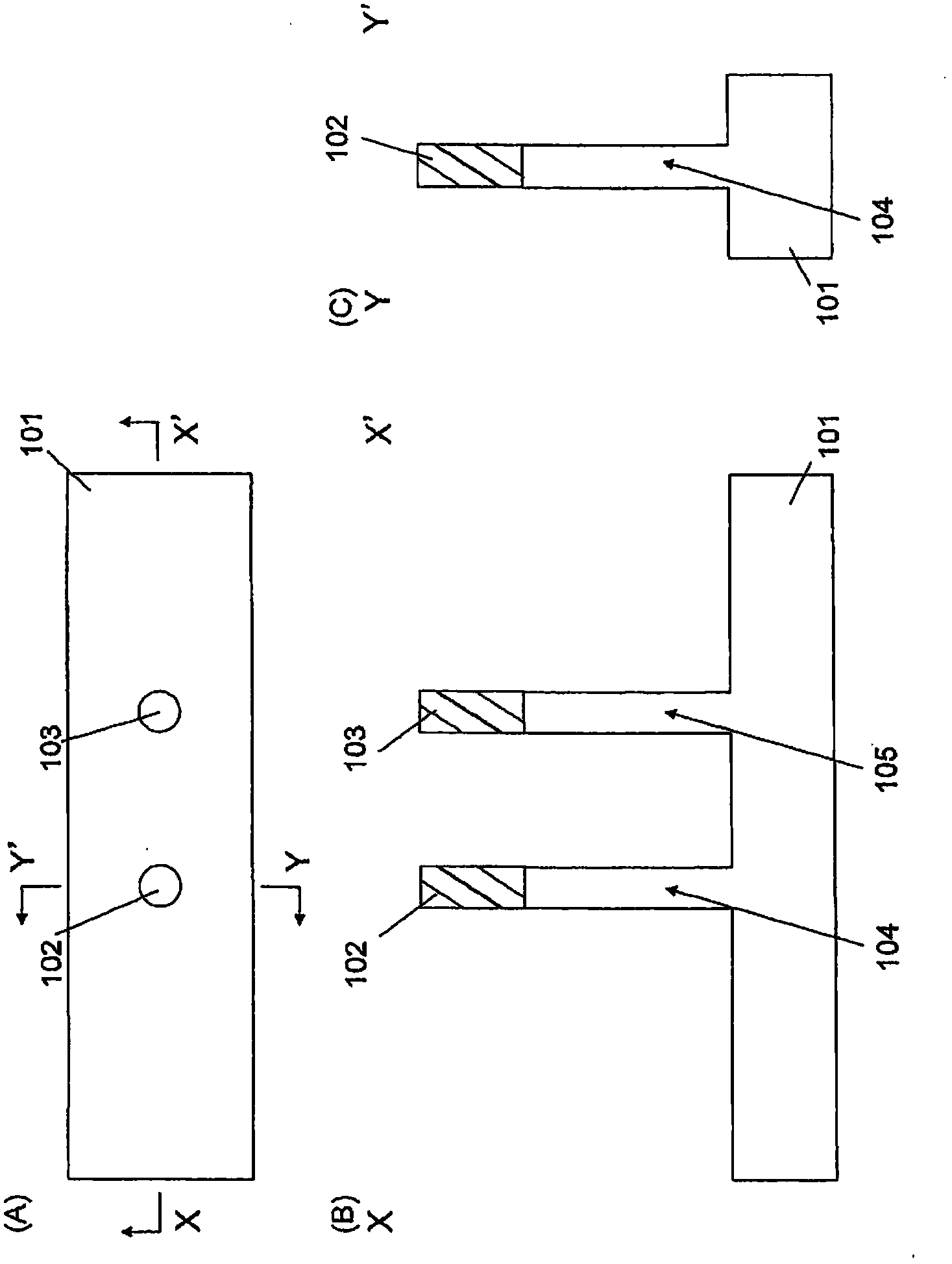

[0116] Then, if image 3 (A), image 3 (B), image 3 As shown in (C), the silicon substrate 101 is etched to form the first columnar silicon layer 104 and the second columnar silicon layer 105 . Preferably, the heights of the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More