Semiconductor device manufacturing method

A device manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of sub-threshold characteristic degradation, high defect density, self-heating effect, etc., to avoid self-heating problems, manufacturing methods The effect of simplicity and efficiency, reducing complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] Hereinafter, the present invention is described by means of specific embodiments shown in the drawings. It should be understood, however, that these descriptions are exemplary only and are not intended to limit the scope of the present invention. Also, in the following description, descriptions of well-known structures and techniques are omitted to avoid unnecessarily obscuring the concept of the present invention.

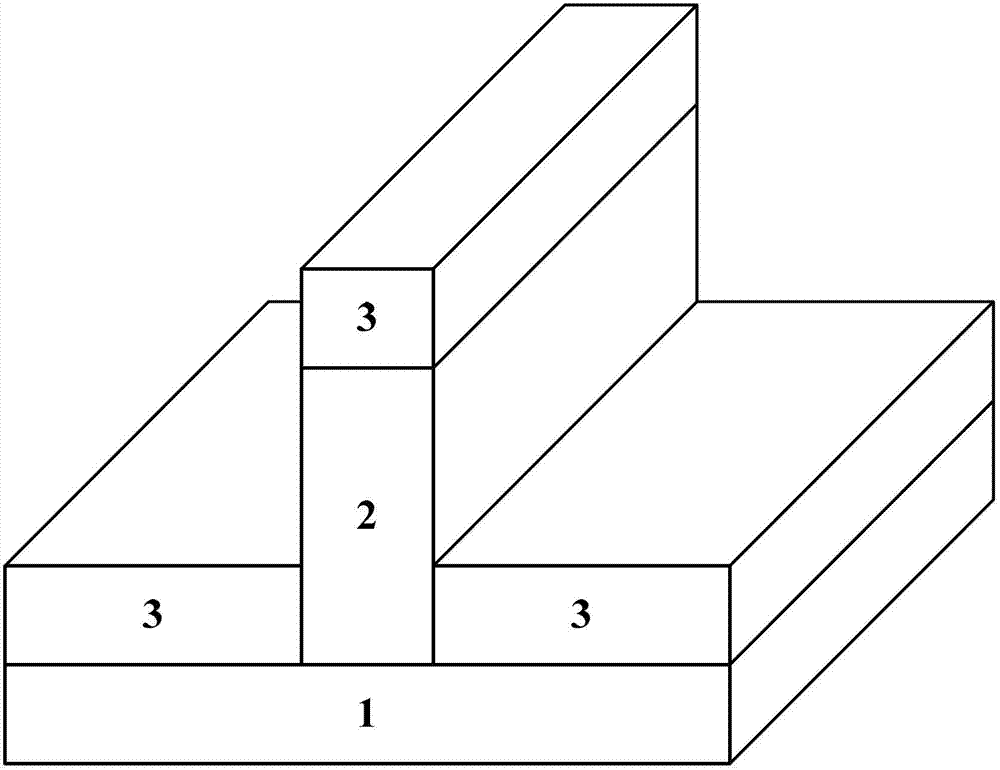

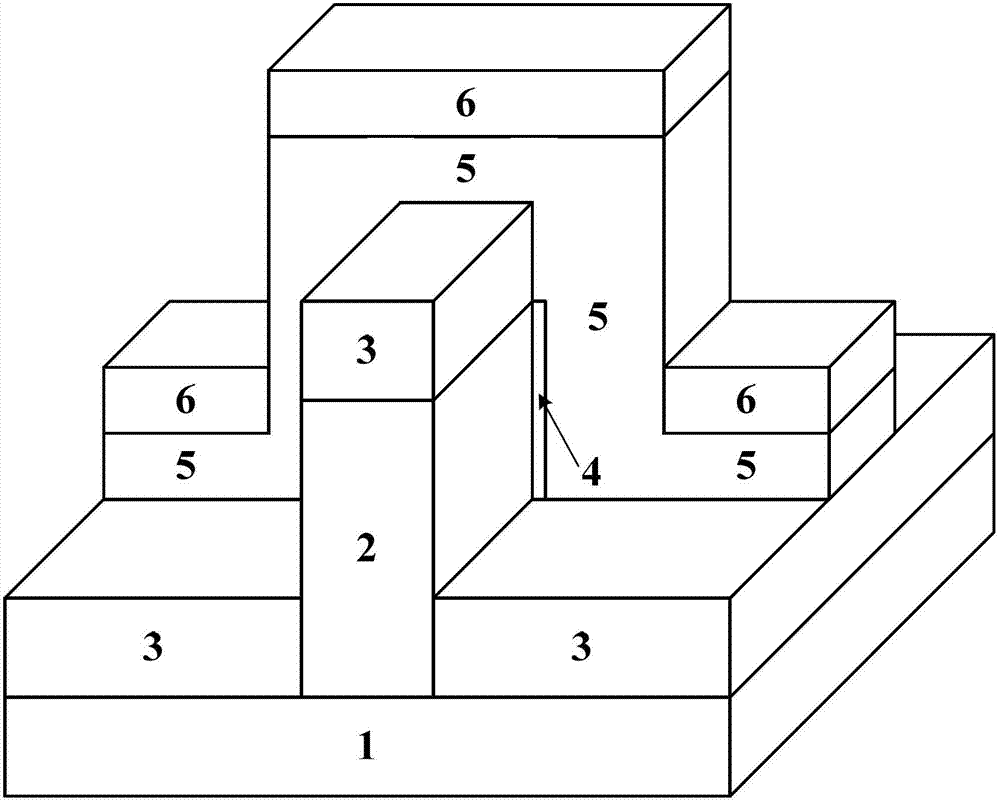

[0036] The present invention provides a FinFET manufacturing method, and its manufacturing process is shown in the attached Figure 1-9 .

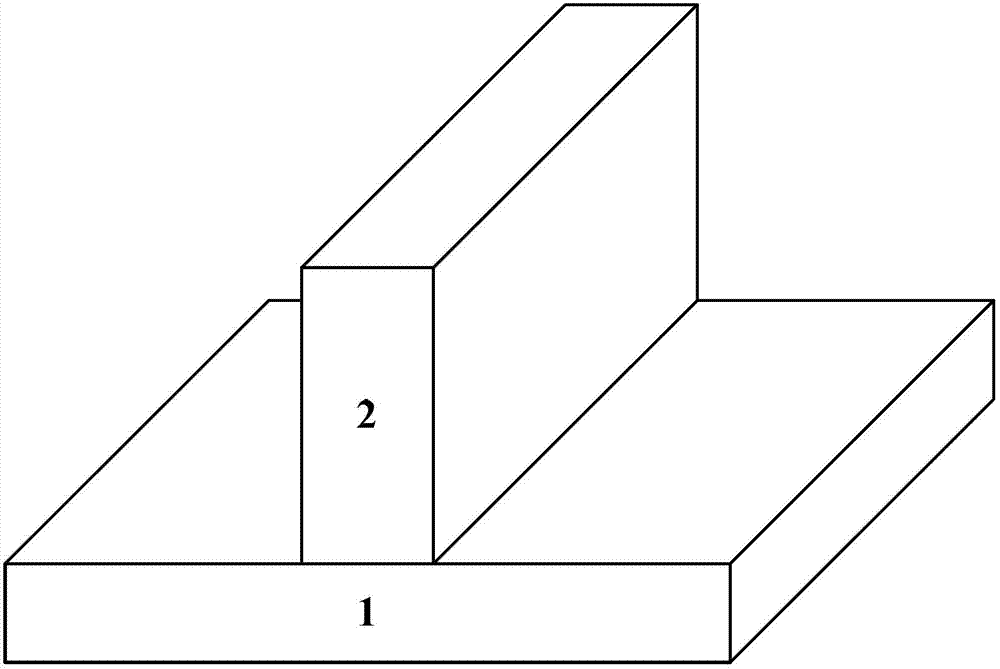

[0037] First, see attached figure 1, Fin (fin-shaped semiconductor pillar) 2 is formed on the semiconductor substrate 1 . A semiconductor substrate 1 is provided, and a bulk silicon substrate is used in this embodiment. Fin2 is formed on a semiconductor substrate 1, and Fin2 has a side surface and a top surface. The method for forming Fin2 specifically includes: first coating a photoresist on the semiconductor subs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More