Interrupt processing method and device and interrupt controller

A processing method and technology of central processing unit, applied in the field of communication, can solve the problems of large occupied area and many logics, and achieve the effect of saving area, simplifying software process, and reducing the number of logics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] Hereinafter, the present invention will be described in detail with reference to the drawings and examples. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other.

[0044] When the interrupt controller in the related art performs interrupt processing, synchronous sampling is adopted, which may easily lead to the risk of loss of the sampling signal, and the handshake process is relatively complicated. Based on this, an embodiment of the present invention provides an interrupt processing method, device, and interrupt controller, which simplifies the handshaking process and reduces the logic of the interrupt controller, and will be described through embodiments below.

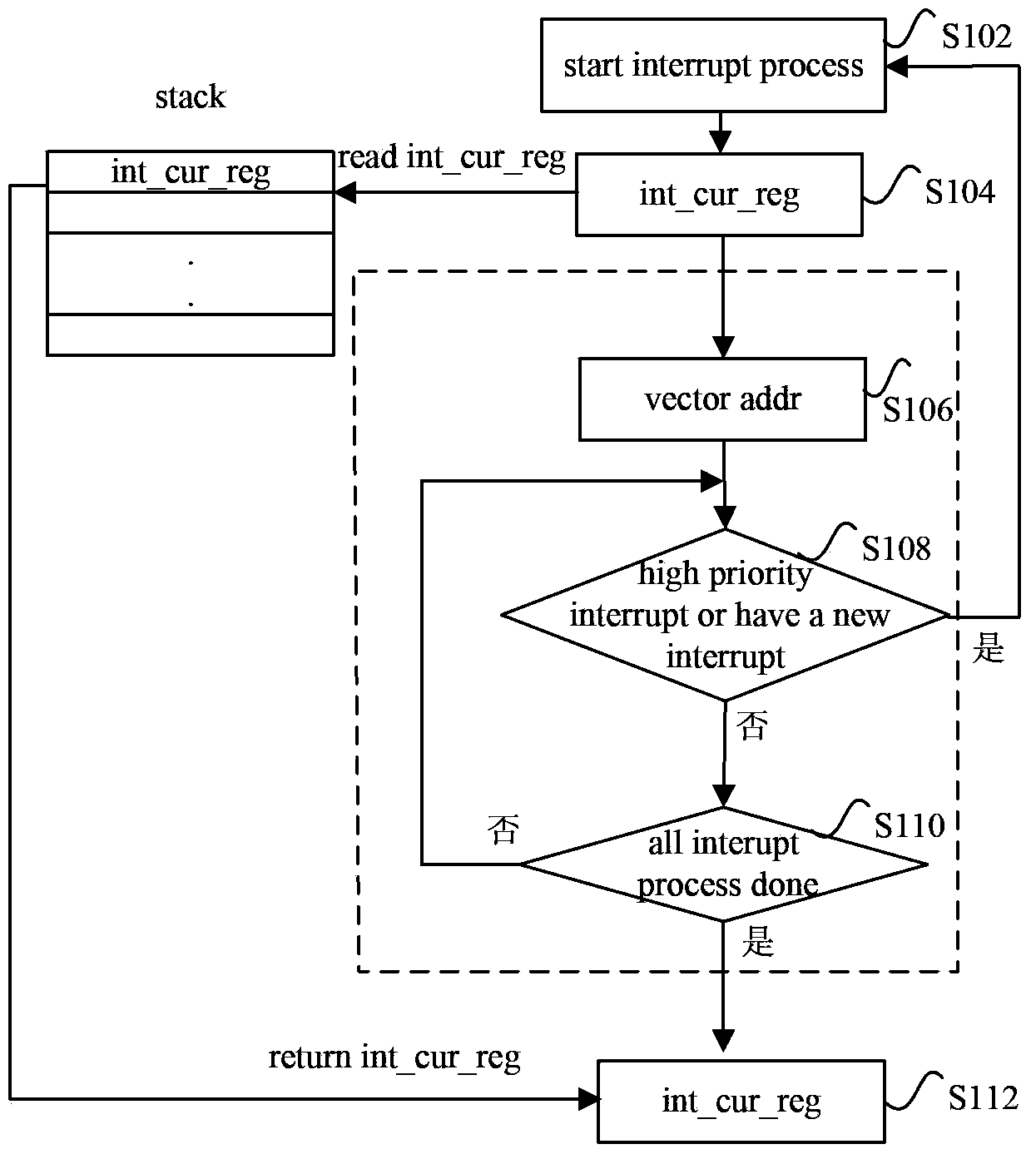

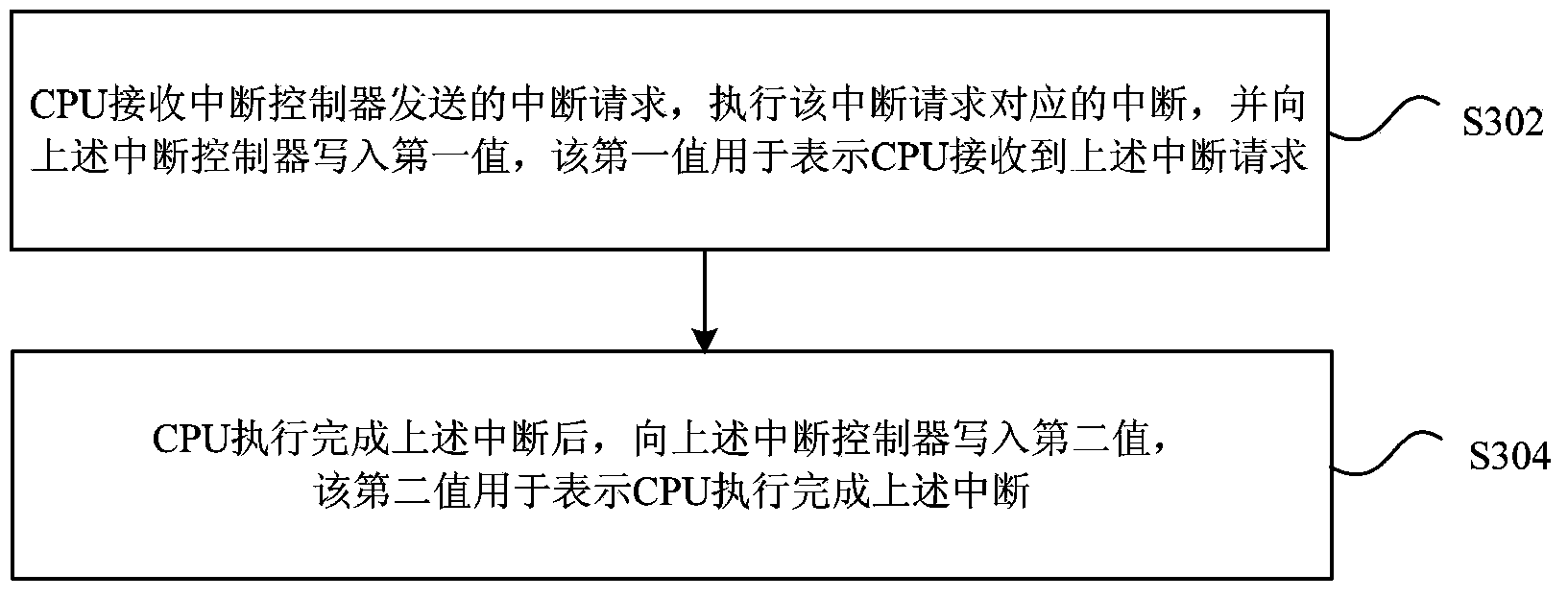

[0045] image 3 is a flowchart of an interrupt processing method according to an embodiment of the present invention, such as image 3 As shown, the method includes the following steps (step S302-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More