Semiconductor device, apparatus of estimating lifetime, method of estimating lifetime

A semiconductor and life-span technology, applied in semiconductor devices, semiconductor/solid-state device components, measuring devices, etc., can solve the problem that it is difficult to specify the location of raised cracks in advance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example )

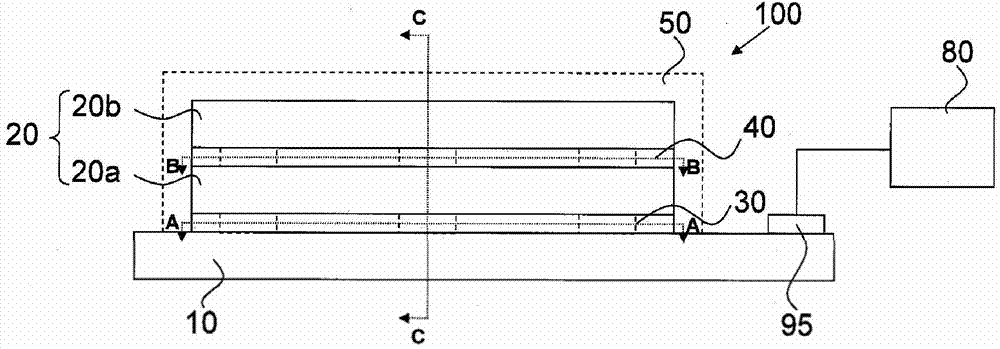

[0023] figure 1 is a diagram illustrating the semiconductor device 100 of the first embodiment.

[0024] The semiconductor device 100 is configured to include a stacked semiconductor chip 20 formed by stacking a plurality of semiconductor chips in a stacking direction (upward in the figure) on a circuit board 10 such as an interposer. The stacked semiconductor chips 20 are configured to include a plurality of first semiconductor chips 20a including a lowermost semiconductor chip and a plurality of second semiconductor chips 20b stacked over the first semiconductor chips 20a.

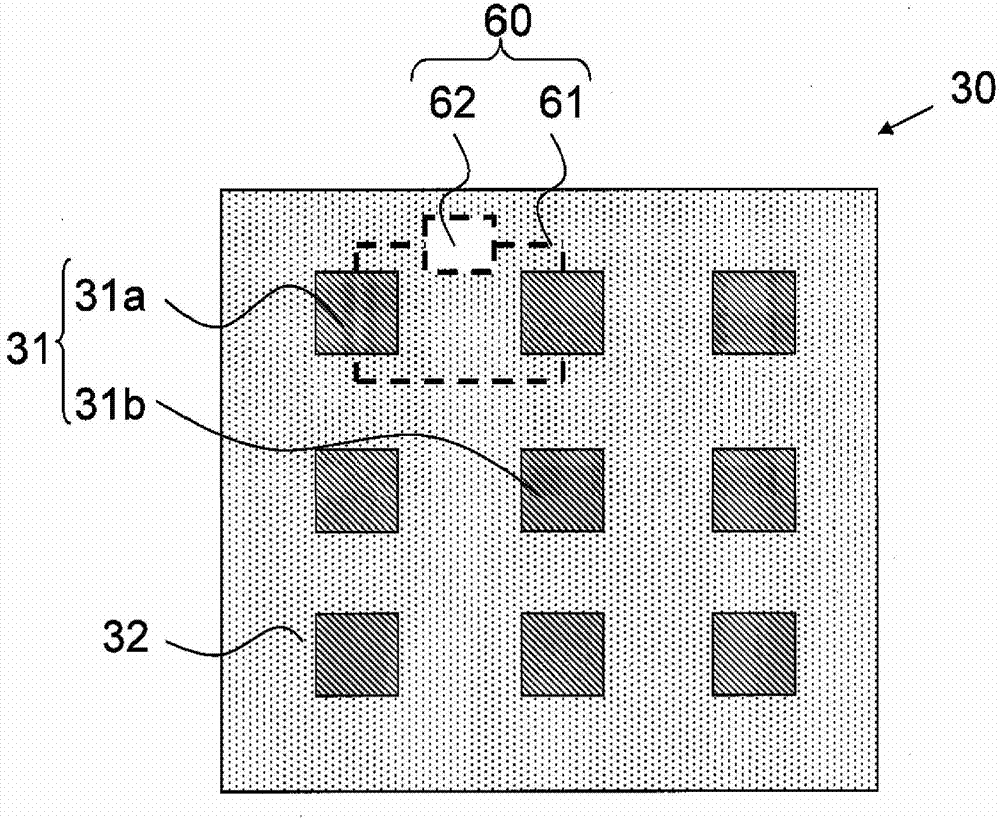

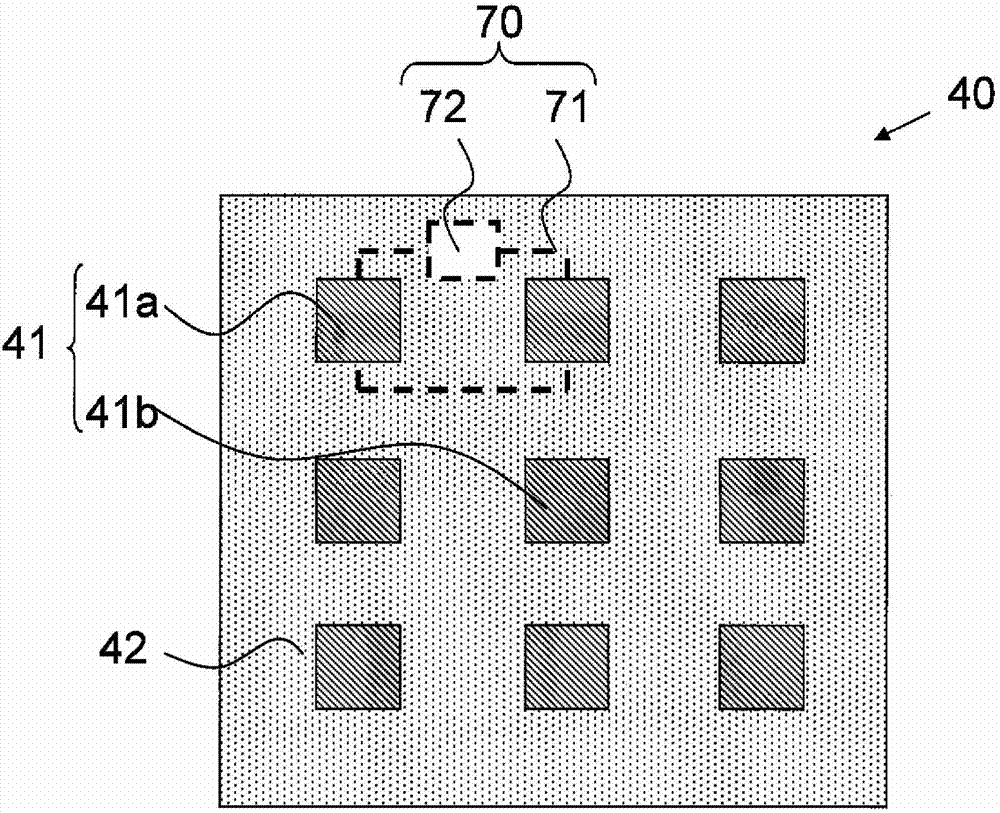

[0025] The circuit board 10 and the first semiconductor chips 20 a are interconnected by the first interconnection unit 30 , and two of the first semiconductor chips 20 a are interconnected by the first interconnection unit 30 . The first semiconductor chip 20 a and the second semiconductor chip 20 b are interconnected by the second interconnection unit 40 , and two of the second semiconductor chips 20 ...

no. 2 example )

[0053] Figure 5 is a diagram illustrating a semiconductor device 200 of the second embodiment. Denote with the same reference numerals as the figure 1 The components of the semiconductor device 100 are the same, and the detailed description will not be repeated. In the semiconductor device 200 , the first signal from the first detection unit 62 and the second signal from the second detection unit 72 are used to estimate the load state in the semiconductor device 200 and to estimate the lifetime of the semiconductor device 200 .

[0054] Apart from figure 1 In addition to the semiconductor device 100 , the semiconductor device 200 further includes a storage unit 210 , a load estimating unit 220 , and a lifetime estimating unit 230 . As the storage unit 210, a storage device 400 such as a memory is used. As the load estimating unit 220 and the lifetime estimating unit 230 , an arithmetic processing unit 500 such as a CPU is used. The load estimation unit 220 is electricall...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap