Construction method for network-on-chip topological structure based on no-buffer router framework

A construction method and network-on-chip technology, applied in the field of computer architecture, can solve the problem of high average delay and energy consumption, and achieve the effect of reducing average delay and energy consumption, reducing impact, and reducing the possibility of conflict

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

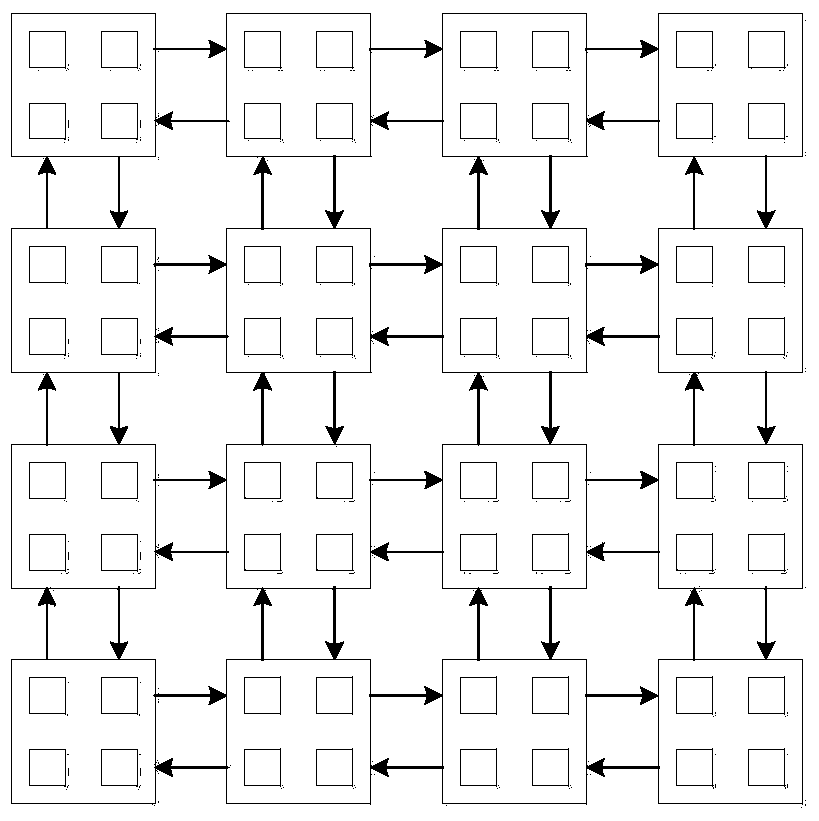

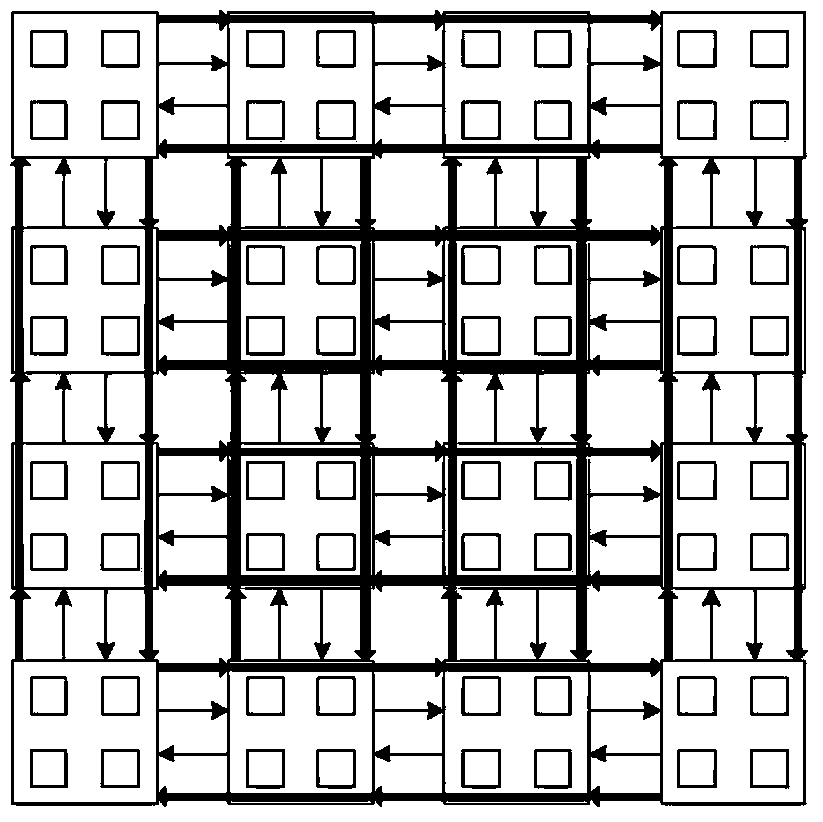

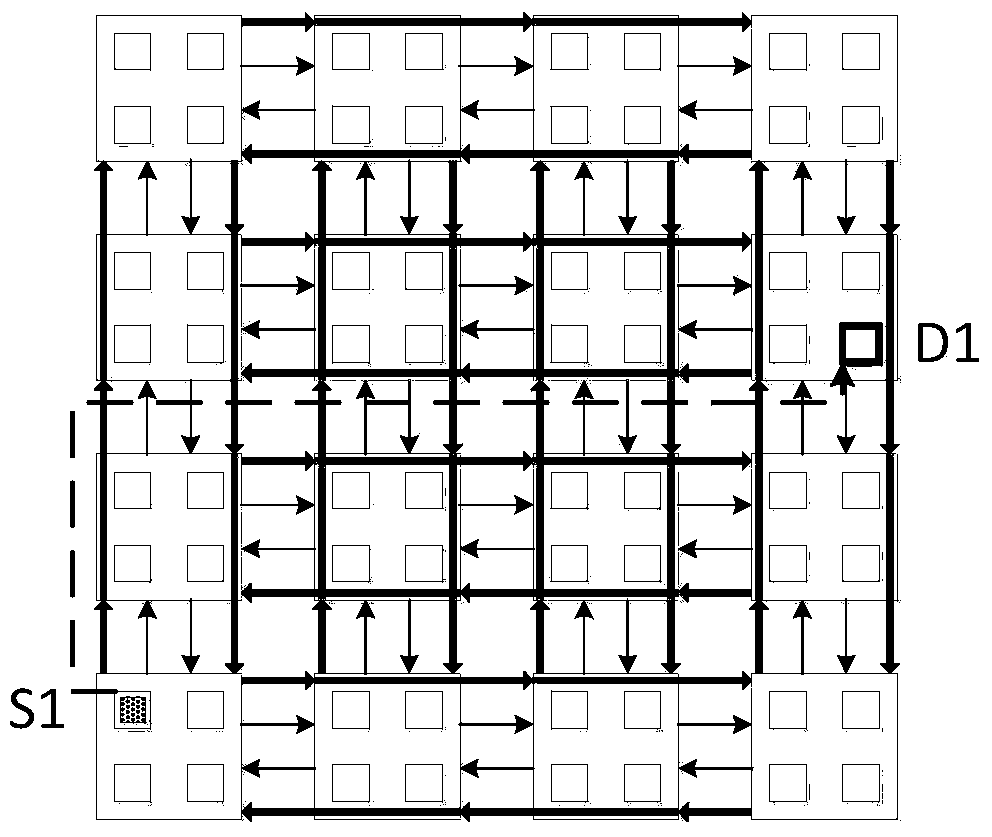

[0026] Currently widely used centralized mesh topology such as figure 1 shown. The present invention introduces a bus on each row and each column on the basis of the existing centralized mesh topology structure, and connects all routers on the row and the column together to form a redundant centralized mesh- bus structure. Its construction method includes the following steps:

[0027] Step 1, connect each router to 4 local cores.

[0028] figure 1 In , each small square represents a core, and the large square represents a router. Each group of 4 cores is connected to a local router.

[0029] Step 2. Arrange routers as a rectangular array closest to a square.

[0030] figure 1 There are 64 cores and 16 routers arranged in a square.

[0031] Step 3, each router is connected with its horizontally and vertically adjacent routers through a d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More