NAND Flash memorizer and implementing method and system of NAND Flash memorizer

A technology of memory and storage block, which is applied in the field of data storage and can solve the problems of low unit price and large capacity of 1 bit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

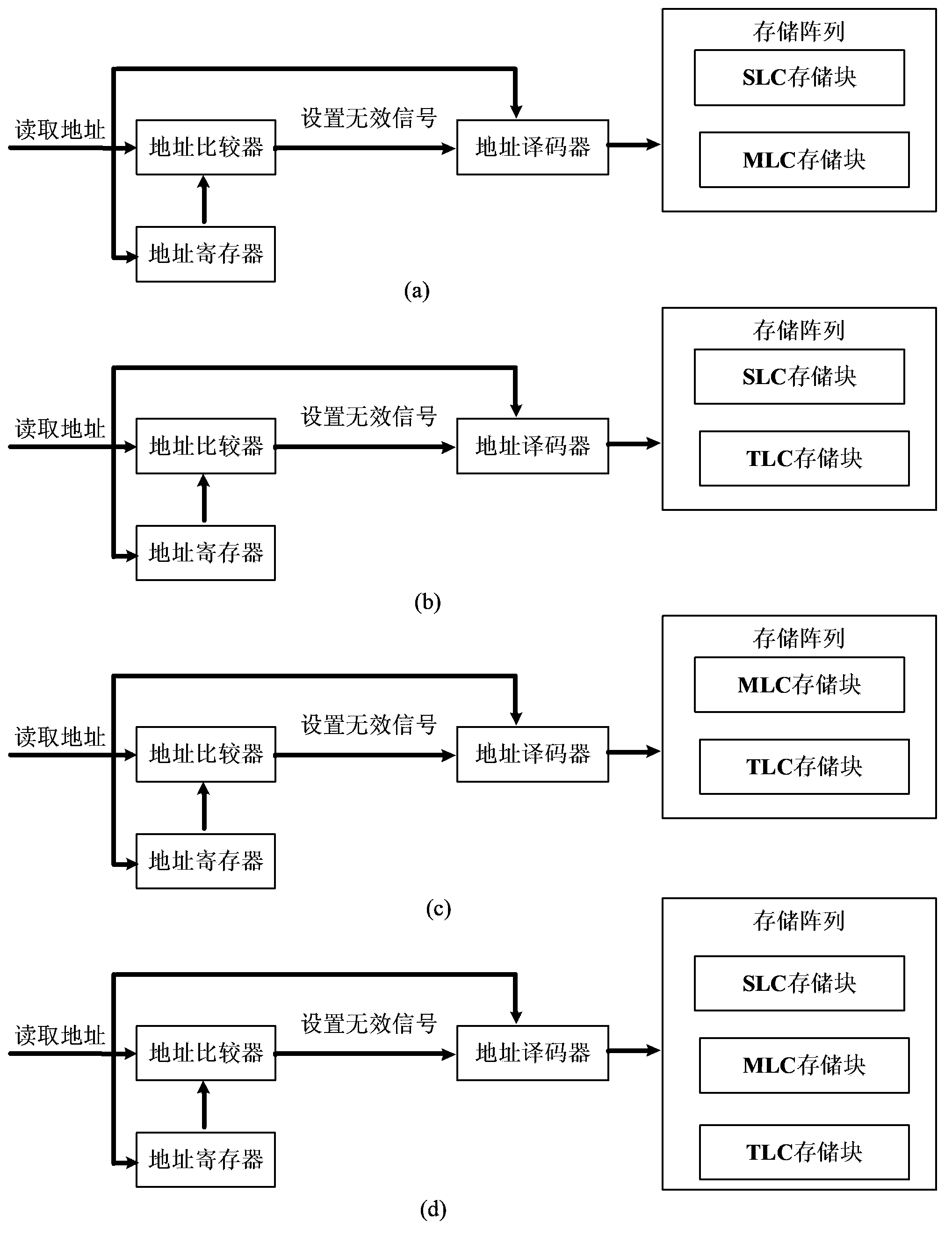

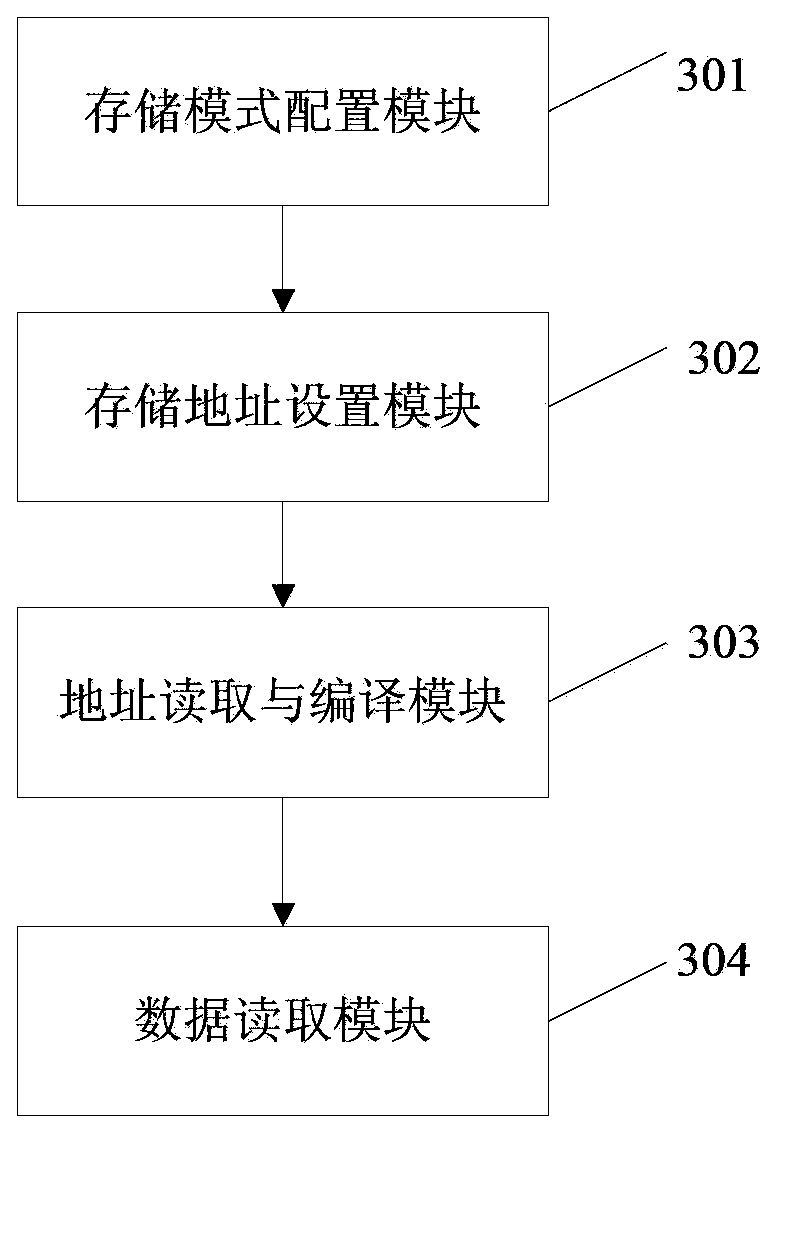

[0101] This embodiment provides a NAND Flash memory, the NAND Flash memory can freely configure the storage mode of each storage block, wherein the storage mode includes SLC mode, MLC mode and / or TLC mode. in:

[0102] SLC (Single-Level Cell, single-value unit), which represents a memory storage unit to store 1 bit, that is, 1bit / cell.

[0103] MLC (Mult i-Level Cell, multi-value storage unit) records multiple sets of bit information in a unit through different levels of voltage, and realizes multi-bit storage capacity in the storage unit, typically 2bit, that is, 2bit / cell, represented as 1 memory storage unit stores 2 bits, the speed and life can be well balanced, and the storage density of SLC is theoretically doubled. It is generally used in solid-state hard disks, mobile hard disks, and high-performance U disks.

[0104] TLC (Trinary-Level Cell, three-value storage unit) means that a memory storage unit can store 3 bits, that is, 3bit / cell. Using charges of diff...

Embodiment 2

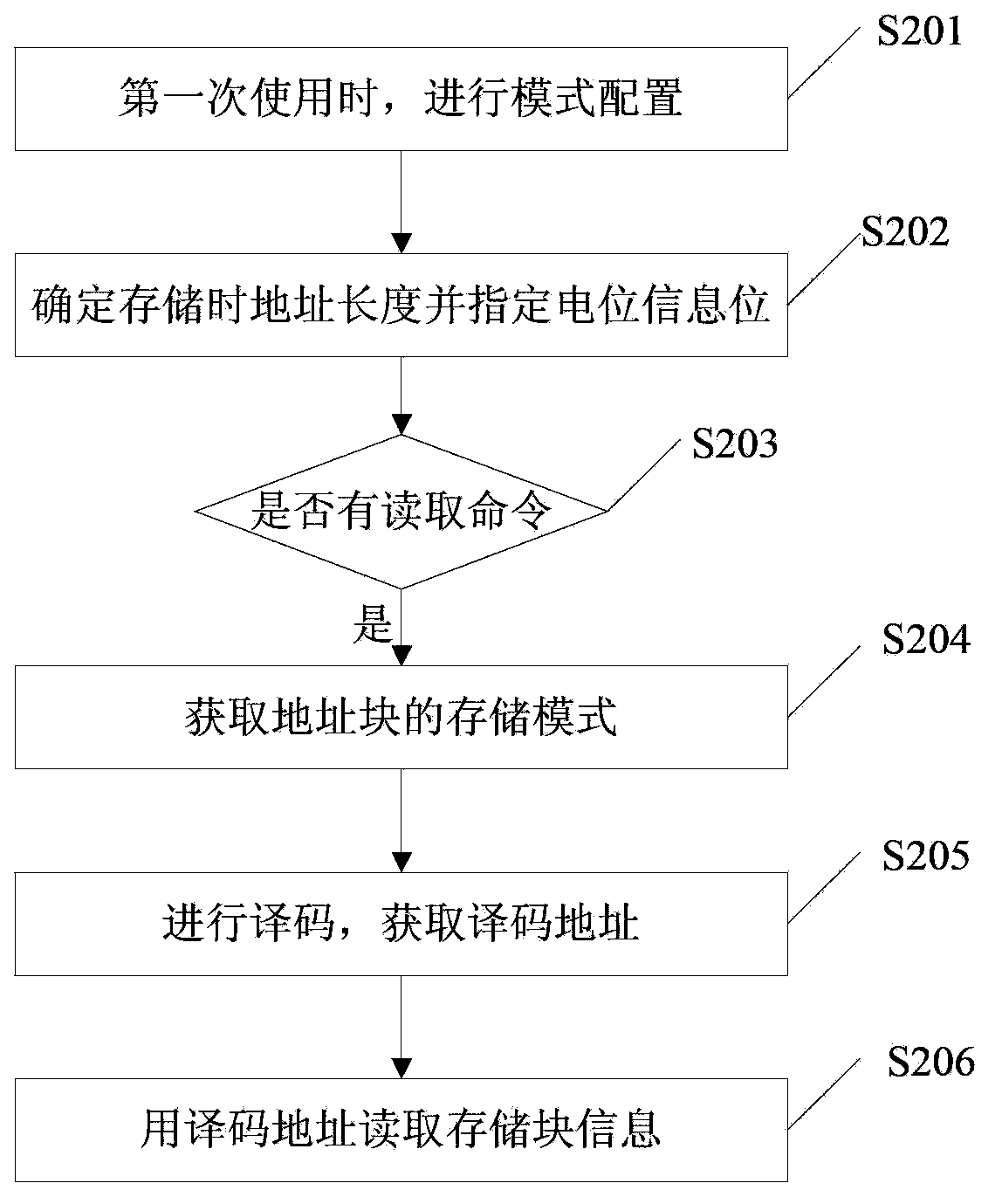

[0143] When the NAND Flash memory provided in this embodiment is used for the first time, the memory is set to a partial SLC mode and a partial MLC mode (that is, mode 4 in the above embodiment). An address list is established in the register for storing the addresses of the storage blocks in the MLC mode, and the addresses of the storage blocks set in the MLC mode are stored in the MLC list.

[0144] If you need to use n-bit address to locate the storage block, you need to use n+1-bit information to store the address of each storage block, and pre-designate one bit from the n+1-bit information to store the potential of the storage block in MLC mode information. Usually the first or last bit is designated to store the potential information of the memory block of the MLC mode

[0145] For example, if the last bit is specified to store the potential information of the memory block in MLC mode, the address of each memory cell is AD , where AD is specified to store the pot...

Embodiment 3

[0151] When the NAND Flash memory provided in this embodiment is used for the first time, the memory is set to a partial SLC mode, a partial MLC mode, and a partial TLC mode (that is, mode seven in the above embodiment). In the register, two address lists are respectively set up to be used to store the address of the storage block of the MLC mode and the address of the storage block of the TLC mode, and the address of the storage block that is set to the MLC mode is stored in the MLC list, and will be set as Addresses of memory blocks in TLC mode are stored in the TLC list.

[0152] If you need to use n-bit address to locate the storage block, you need to use n+2-bit information to store the address of each storage block, and pre-designate two bits for storing the potential of the storage block in TLC mode from the n+2-bit information information, further specifying one bit from the specified two bits to indicate invalid information when the storage block pointed to by the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More