Astronavigation FPGA universal refresh circuit based on JTAG interface and achieving method thereof

An implementation method and circuit technology, applied in the direction of logic circuits using specific components, logic circuits using basic logic circuit components, etc., can solve problems such as internal function disorder, short-circuiting, functional failure, etc., to achieve complete state and improve reliability. Strong and practical effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

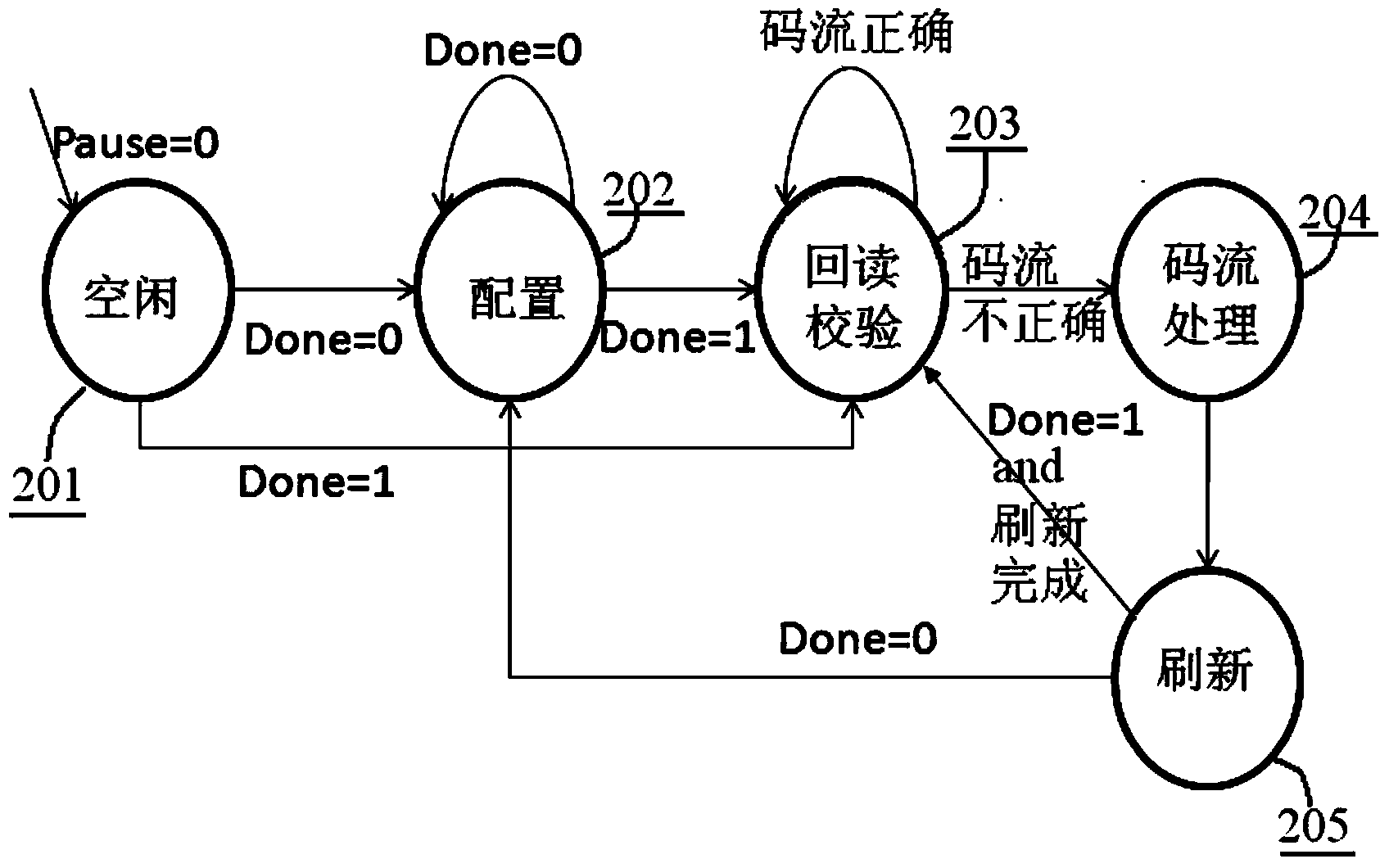

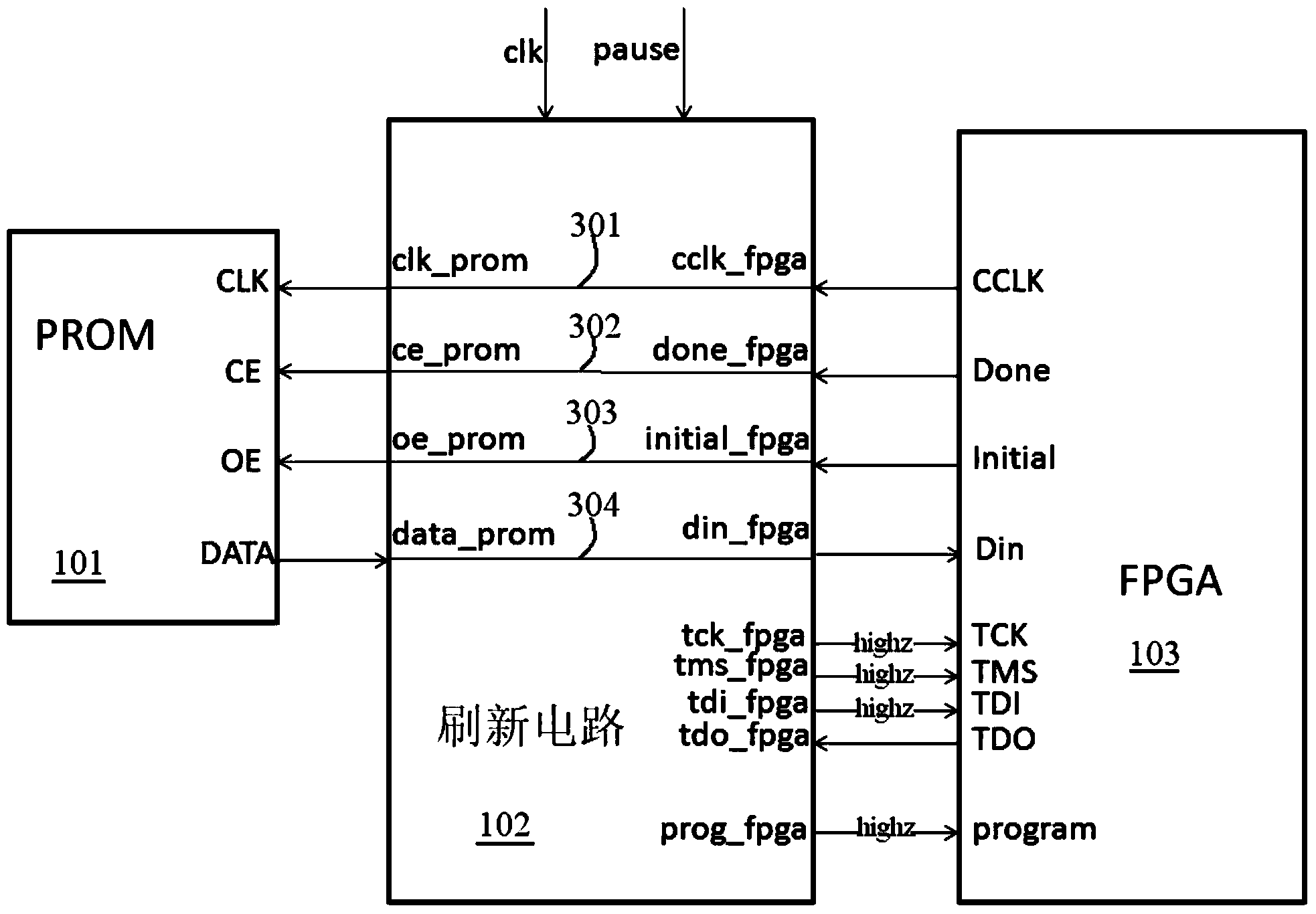

[0068] After power-on, connect the pause pin of the refresh circuit 102 to "0" level, then the refresh circuit 102 suspends work, enters and remains in the idle state 201; when the refresh circuit is in the idle state, if image 3 , connect the internal connections 301, 302, 303, 304, and connect the corresponding pins of PROM101 and FPGA103 together, that is, the CLK pin of PROM101 is connected to the CCLK pin of FPGA103, the CE pin of PROM101 is connected to the Done pin of FPGA103, The OE pin of PROM101 is connected to the Initial pin of FPGA103, and the DATA pin of PROM101 is connected to the Din pin of FPGA103; at the same time, the outputs of tck_fpga, tdi_fpga, tms_fpga and prog_fpga of refresh circuit 102 are in a high-impedance state. At this time, the refresh circuit 102 has no influence on the PROM 101 and the FPGA 103 , and it can be regarded that the refresh circuit 102 is bypassed.

Embodiment 2

[0070] After power-on, the pause pin of the refresh circuit 102 is connected to “1” level, the clk pin is connected to a clock signal with a fixed frequency, and the input signal of the done_fpga pin is started to be detected. If the refresh circuit 102 detects that the done_fpga level is “0”, the refresh circuit 102 will enter the configuration state 202 , otherwise it will directly jump to the readback verification state 203 . In configuration state 202, such as image 3 , the refresh circuit 102 is connected to the internal connections 301, 302, 303, 304, and the corresponding pins of the PROM101 and FPGA103 are connected together, that is, the CLK pin of the PROM101 is connected to the CCLK pin of the FPGA103, and the CE pin of the PROM101 is connected to the Done pin of the FPGA103. Pins, the OE pin of PROM101 is connected to the Initial pin of FPGA103, the DATA pin of PROM101 is connected to the Din pin of FPGA103; during the FPGA configuration process, the Done pin outp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More