Logic controller for nonvolatile memory

A logic controller and non-volatile technology, applied in the field of logic controllers, can solve problems such as complex operation, complex interface of non-volatile memory, error-prone, etc., to simplify the writing operation process, simplify the power-on operation process, and powerful test The effect of the function

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

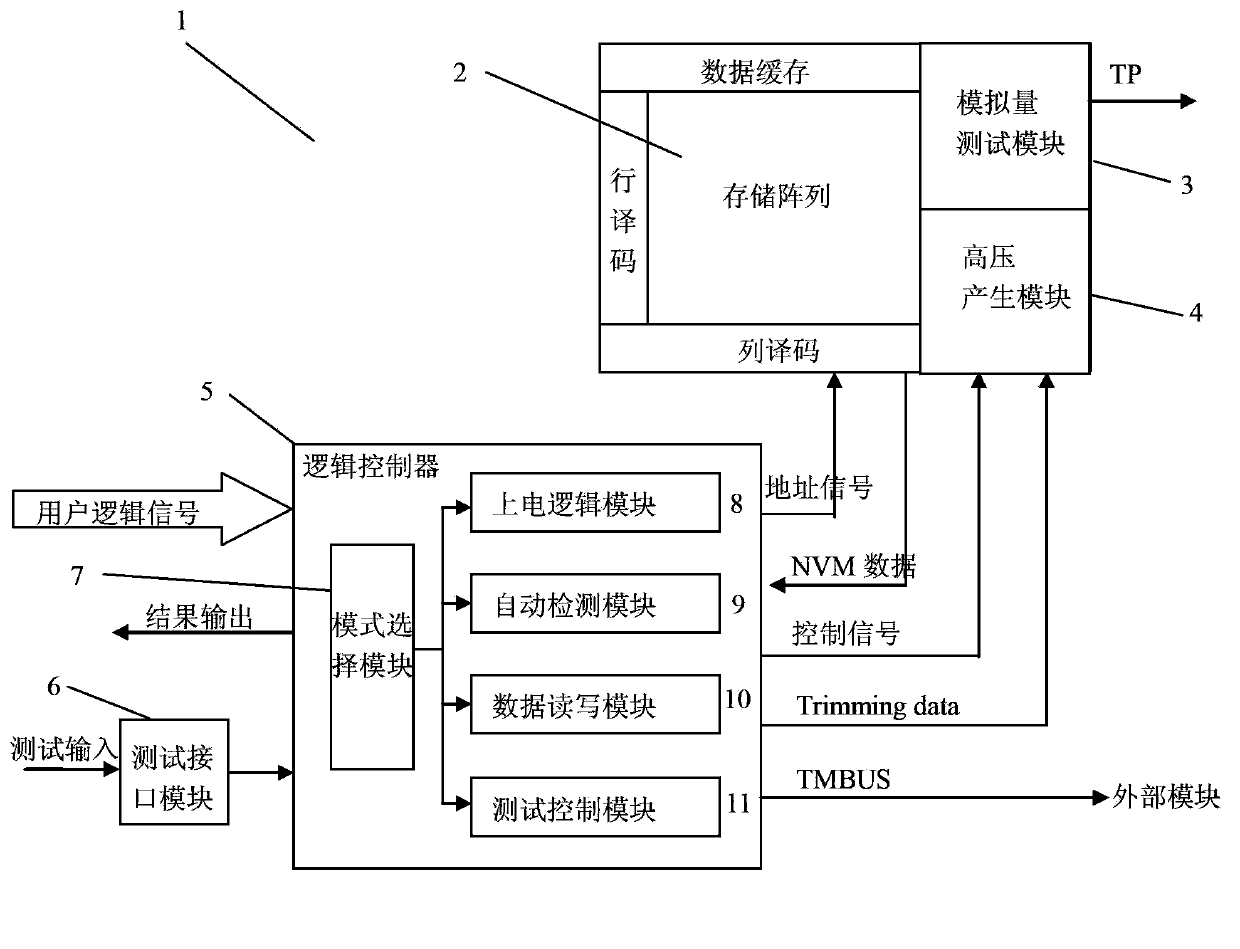

[0043] Such as figure 2 Shown is a schematic diagram of the structure of the non-volatile memory 1 of the embodiment of the present invention. The non-volatile memory 1 of the embodiment of the present invention includes a storage array 2, a test interface module 6, a high voltage generation module 4, an analog test module 3 and a logic controller 5. It also includes row decoding, column decoding and data cache modules. The logic controller 5 includes: a mode selection module 7 , a power-on logic module 8 , a data reading and writing module 10 , an automatic detection module 9 and a test control module 11 .

[0044] The mode selection module 7 is used to generate the working state and working mode of the non-volatile memory 1, the working state includes a user state and a test state; the working mode includes a power-on operation mode, a read operation mode, and a write operation mode. mode, test mode and automatic detection mode; the mode selection module 7 is jointly contr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More