A divide-by-two and high-speed multiplexer

A multiplexer and two-frequency divider technology, which is applied in the field of integrated circuits, can solve the problems of sampling errors and the initial phase of the two-frequency divider is uncertain, and achieves the effect of avoiding sampling errors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

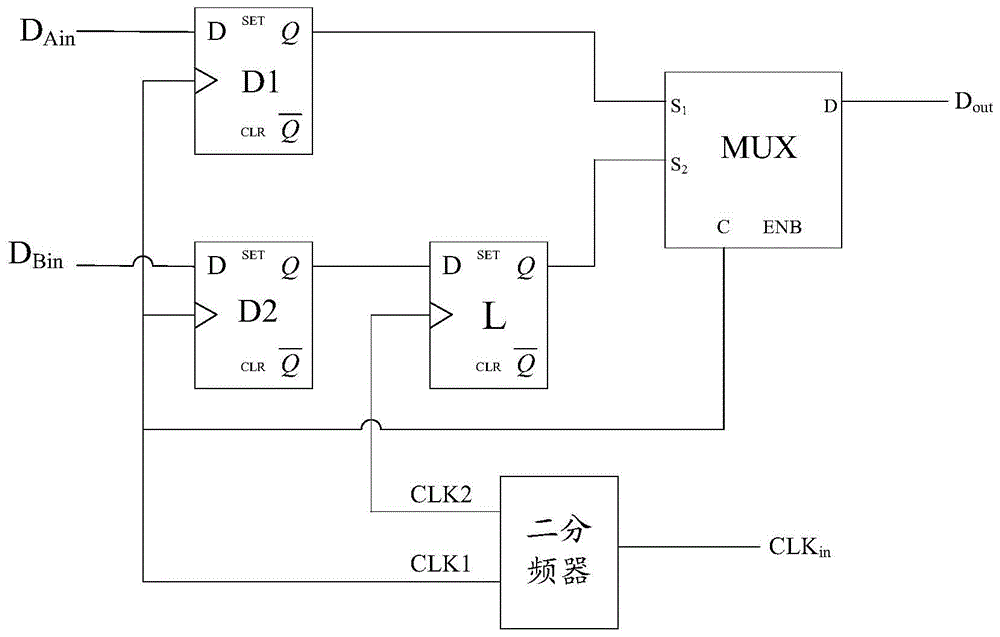

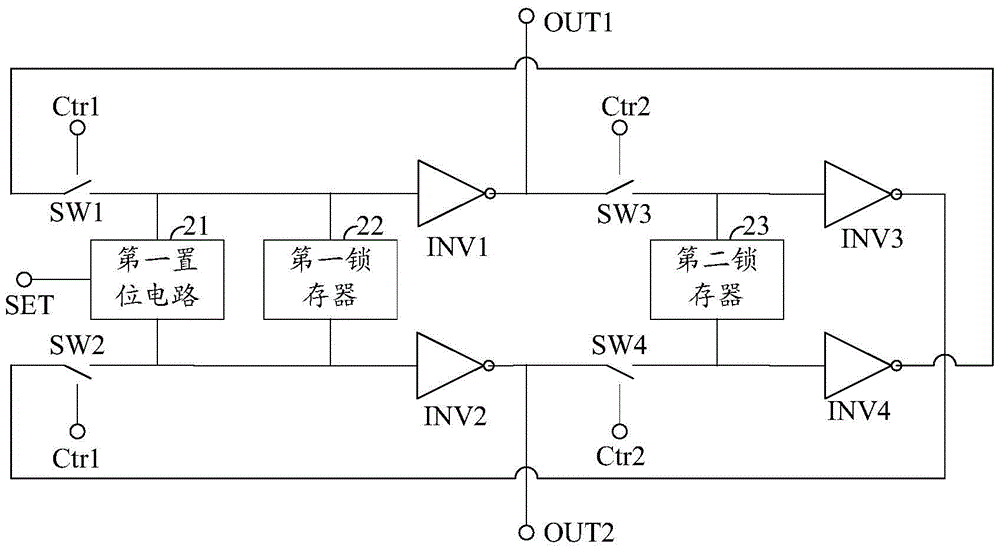

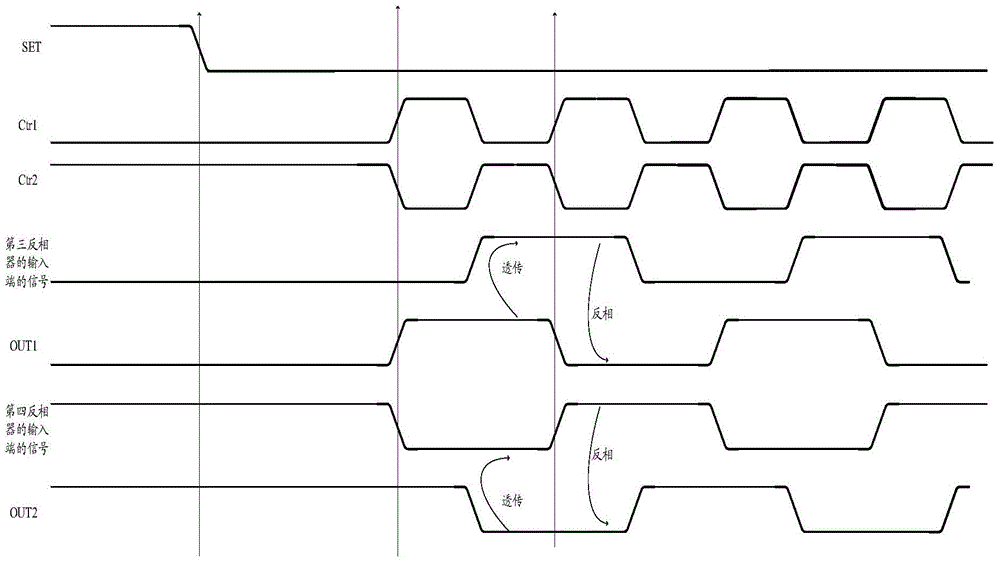

[0060] The frequency divider by two and the high-speed multiplexer provided by the embodiment of the present invention control the frequency divider by a set signal. When the set signal is valid, the first output terminal of the frequency divider by two is at the second level. The second output terminal of the two-frequency divider is the first level; and after the setting signal is changed from valid to invalid, the two-frequency divider is controlled on the first active edge of the clock signal received by the two-frequency divider, The first output terminal of the two-frequency divider outputs the first level, and the second output terminal of the two-frequency divider outputs the second level, so that the initial phase of the two-frequency divider is constant, and then the two-frequency divider is used The high-speed multiplexer of the device is correctly sampled.

[0061] The specific implementation manners of a frequency divider by two and a high-speed multiplexer provid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More