Three-dimensional fan-out type wafer level package structure and manufacturing process

A wafer-level packaging, fan-out technology, used in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve problems such as difficulty, slip, and dislocation are difficult to control, and achieve improvement warping effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will be further described below in conjunction with specific drawings.

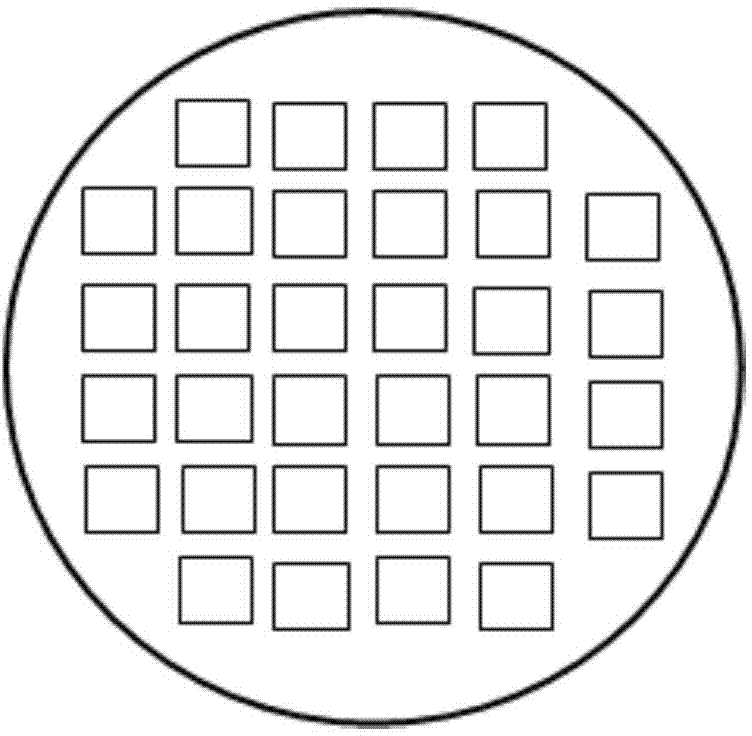

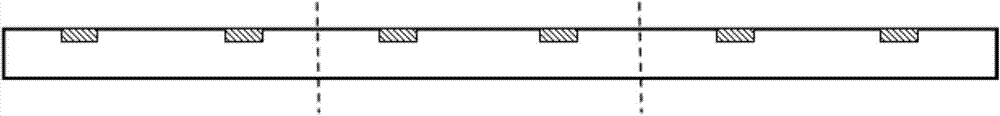

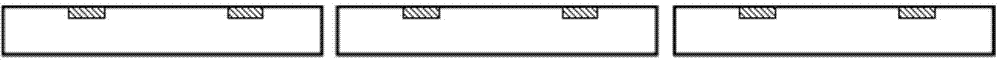

[0046] Such as Figure 18a , Figure 18b As shown, the three-dimensional fan-out wafer level packaging structure includes a first fan-out wafer level package body 10 and a second fan-out wafer level package body 20 (the first fan-out wafer level package body One, two, three or four layers of second fan-out wafer-level packages 20 can be stacked sequentially on top of 10, Figure 18a , Figure 18b Only one stack is shown);

[0047]The first fan-out wafer level package 10 includes a first chip 101 with metal electrodes 1011, 1012 and a first metal layer 102, the first chip 101 and the first metal layer 102 are plastic-sealed by a first plastic package 103 As a whole; the front 101a of the first chip 101 is located on the same plane as the front 103a of the first plastic package 103, the back 101b of the first chip 101 is located on the same plane as the back 103b of the firs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More