An Isolation Setting Method for Hole Impedance Matching in High Speed Circuit Design

A circuit design and impedance matching technology, applied in computing, electrical digital data processing, special data processing applications, etc., can solve the problems of difficulty in adjustment and isolation, difficulty in ensuring accuracy, and time-consuming, and achieve accurate data, data accuracy and reliability. Effective, discriminative way efficient effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

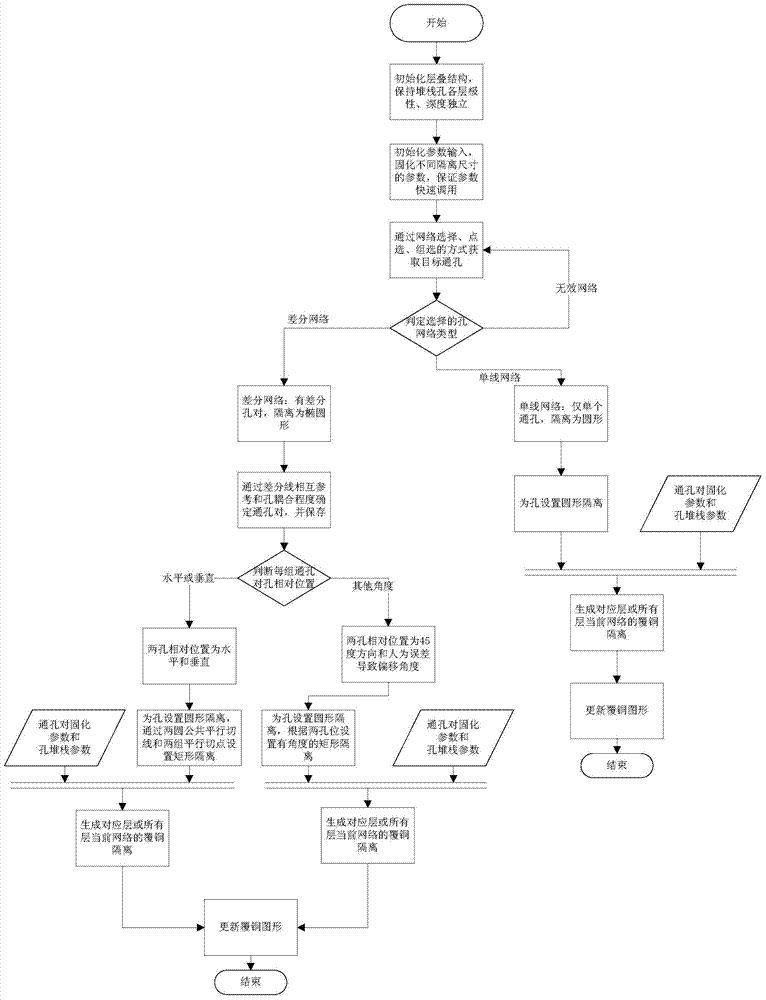

[0022] The present invention will be further described below in conjunction with drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, but not to limit the present invention. In addition, it should be noted that, for the convenience of description, only parts related to the present invention are shown in the drawings but not all content.

[0023] Please refer to figure 1 as shown, figure 1 A flow chart of an isolation setting method for hole impedance matching in high-speed circuit design provided by an embodiment of the present invention.

[0024] In this embodiment, the isolation setting method for hole impedance matching in high-speed circuit design includes the following steps:

[0025] Step S101, start, initialize the stack structure, keep the polarity and depth of each layer of the stack hole independent, this situation may include hole stack information such as blind holes, back ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More