Heterogeneous multi-core processor based on ARM, DSP and FPGA and task scheduling method

A multi-core processor and heterogeneous technology, applied in the directions of multi-program device, program startup/switching, resource allocation, etc., can solve the problems of multi-core processors such as poor adaptability, poor resource control ability, and poor parallel processing ability, and achieve The effects of strong task processing ability, improved resource utilization and environmental adaptability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

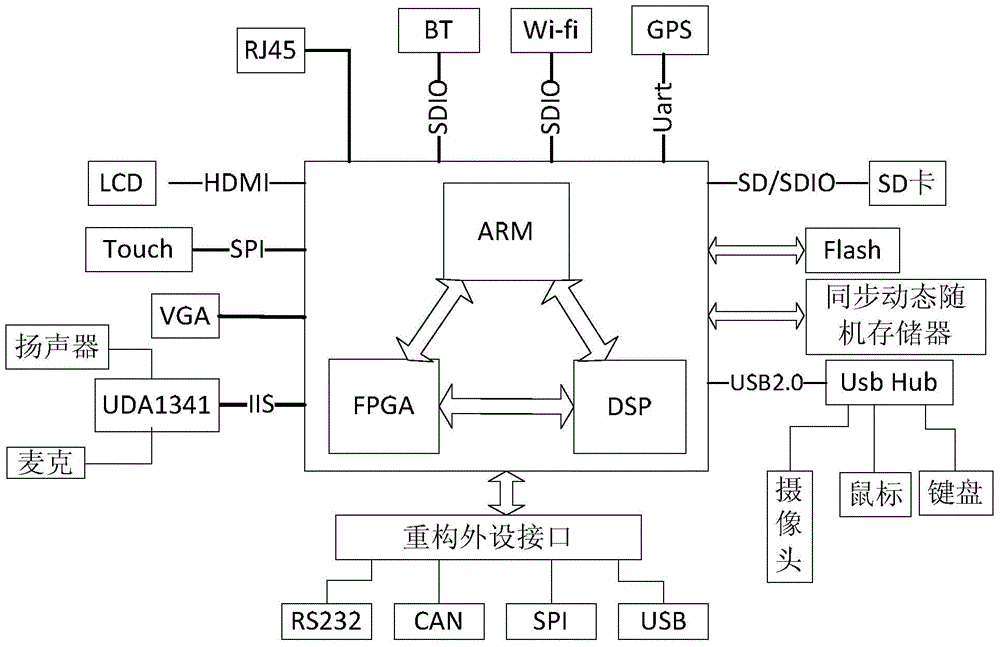

[0020] Specific implementation mode one: combine figure 1 with figure 2 Describe this embodiment mode, the heterogeneous multi-core processor based on ARM, DSP and FPGA described in this embodiment mode includes ARM, DSP, FPGA and peripheral interface, data transmission is carried out between described ARM, DSP and FPGA, and described peripheral The interface includes RS232 interface, CAN bus interface, SPI interface and USB interface. The ARM is used for transaction processing and system management and control, DSP is used to perform tasks containing a large number of calculations, and FPGA is used to restructure into a dedicated processing module And various I / O interfaces.

[0021] The heterogeneous multi-core processor based on ARM, DSP and FPGA described in this embodiment is designed for some complex environments, such as figure 1 As shown, based on three embedded processors ARM, DSP and FPGA, many commonly used IO interfaces, communication interfaces and human-comput...

specific Embodiment approach 2

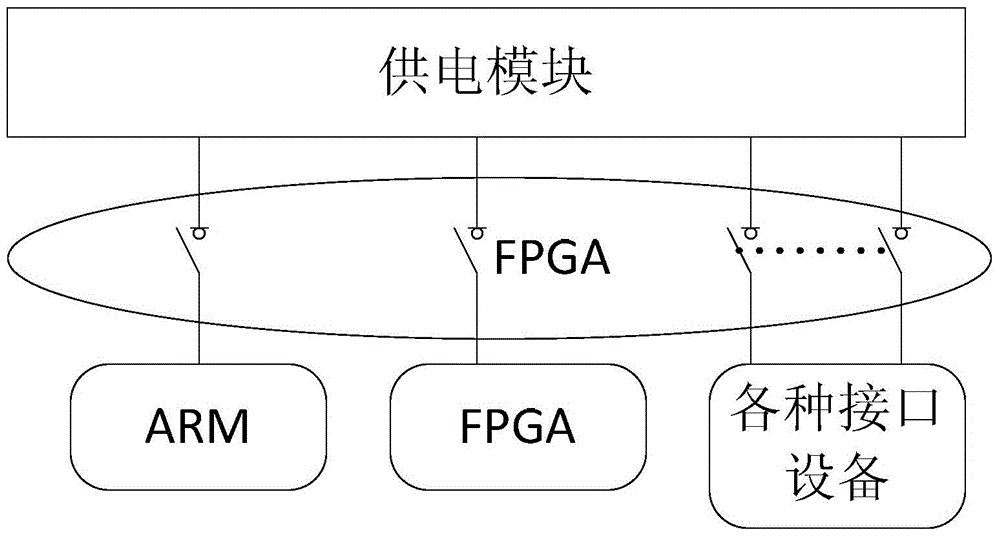

[0042] Specific implementation mode two: combination image 3 This embodiment is described. This embodiment is a further limitation of the heterogeneous multi-core processor based on ARM, DSP and FPGA described in the first embodiment. In this embodiment, the FPGA is embedded with a software-implemented power supply module. The power supply module is used to control the power supply of ARM, DSP and FPGA.

[0043] This implementation mode focuses on optimization for the power consumption problem. In the overall platform, the power consumption is mainly composed of two parts: the power consumption of the interface module chip (such as USB, IIC, SDIO, etc.) and the processor core. Through experimental testing, in the heterogeneous multi-core processor based on ARM, DSP and FPGA described in the first embodiment, the energy consumed by the three processors accounts for the vast majority of the entire system. The power consumption of three processors can reduce the power consumpt...

specific Embodiment approach 3

[0044] Specific implementation mode three: combination figure 1 This embodiment is described. This embodiment is a further limitation of the heterogeneous multi-core processor based on ARM, DSP, and FPGA described in Embodiment 1. In this embodiment, the ARM, DSP, and FPGA are connected through serial interface for interconnection.

[0045] In this embodiment, when the load of each processor is relatively large and the amount of interactive data between each processor is small, the simplest serial interface interconnection can be selected, such as UART, SPI, etc., without wasting more The interface resources can achieve the purpose of communication.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More