A Real-time A/D Fault Diagnosis Method Based on FPGA

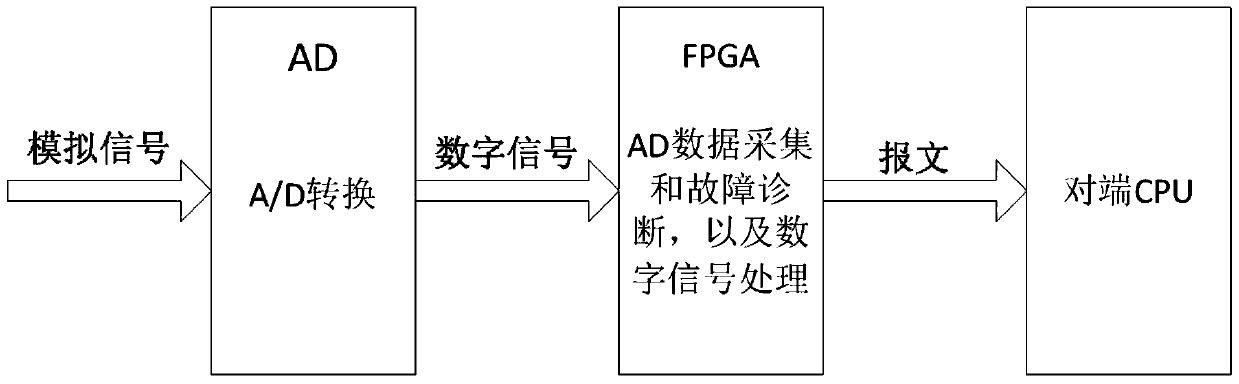

A diagnosis method and real-time fault technology, applied in the direction of analog/digital conversion calibration/testing, etc., can solve the problems of time-consuming and laborious, poor real-time SV data, unable to guarantee illegal SV detection, etc., achieving strong portability and shortening the re-development cycle. , Improve the effect of anti-interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

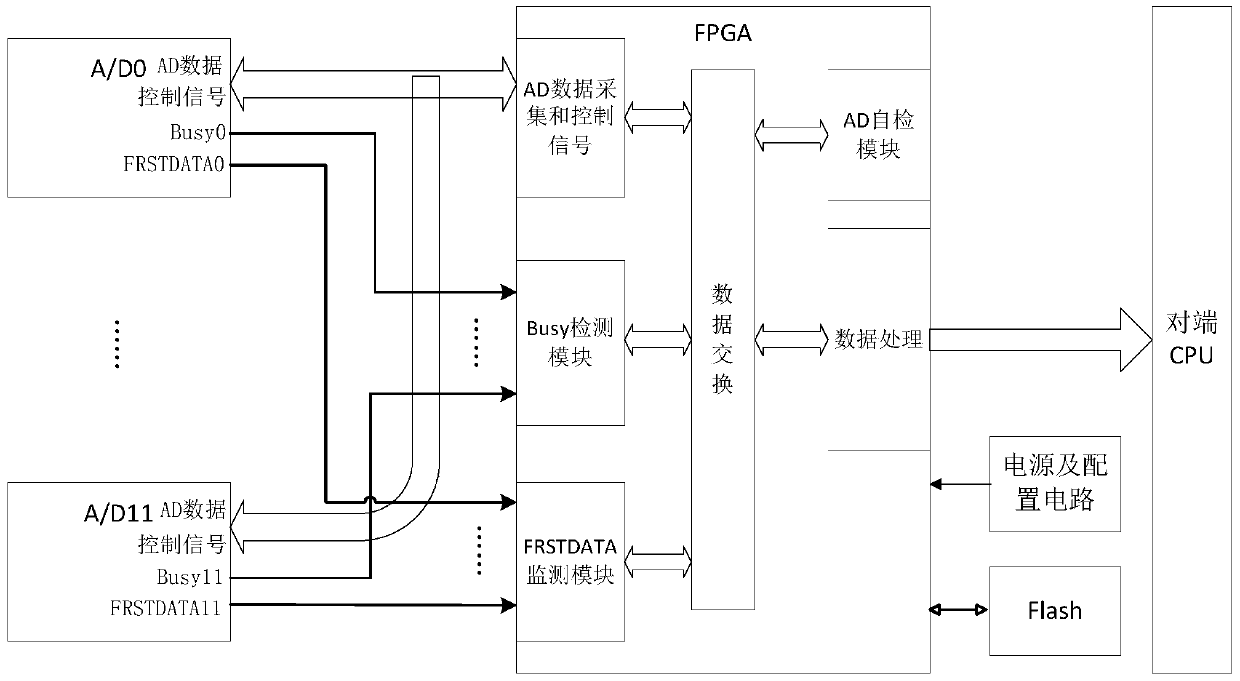

[0028] As a specific implementation mode, the Spartan6 series XC6SLX4 of Xilinx Company and the AD7606 of ANALOGDEVICES Company are selected, each A / D has 8 channels, so 12 A / Ds are used to support 96 channels, and the parallel processing characteristics of FPGA fully satisfy Real-time detection of the 12 A / Ds.

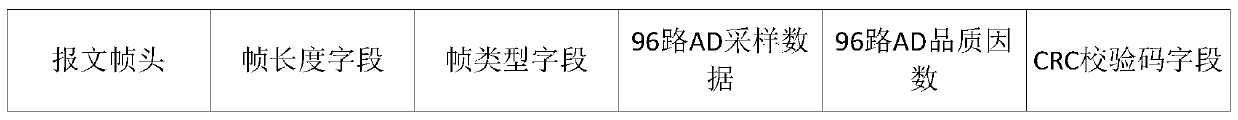

[0029] The present invention connects the eighth channel of each A / D to the power supply VCC for A / D self-inspection. Implementation method: FPGA detects the output characteristic signals and A / D of 12 A / D chips in each sampling cycle. Self-inspection channel, record the level changes of 12 A / D characteristic signals and do power self-inspection on 12 A / Ds, if the requirements are not met, the A / D is considered to be faulty. Such as figure 2 Shown is the hardware block diagram of the A / D real-time fault diagnosis system of the FPGA of the present invention. First, the system is powered on, and the FPGA is configured from the external flash. After the configuration ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com