Instruction fetching method and instruction fetching structure thereof for low-cost high-band-width microprocessor

A microprocessor and high-bandwidth technology, applied in the direction of concurrent instruction execution, machine execution devices, etc., can solve the problems of high power consumption and area overhead, limited clock frequency, high complexity, etc., achieve short design cycle, eliminate structural redundancy In addition, the effect of improving the instruction fetch bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

[0029] The present invention mainly includes the following aspects in the fetching process:

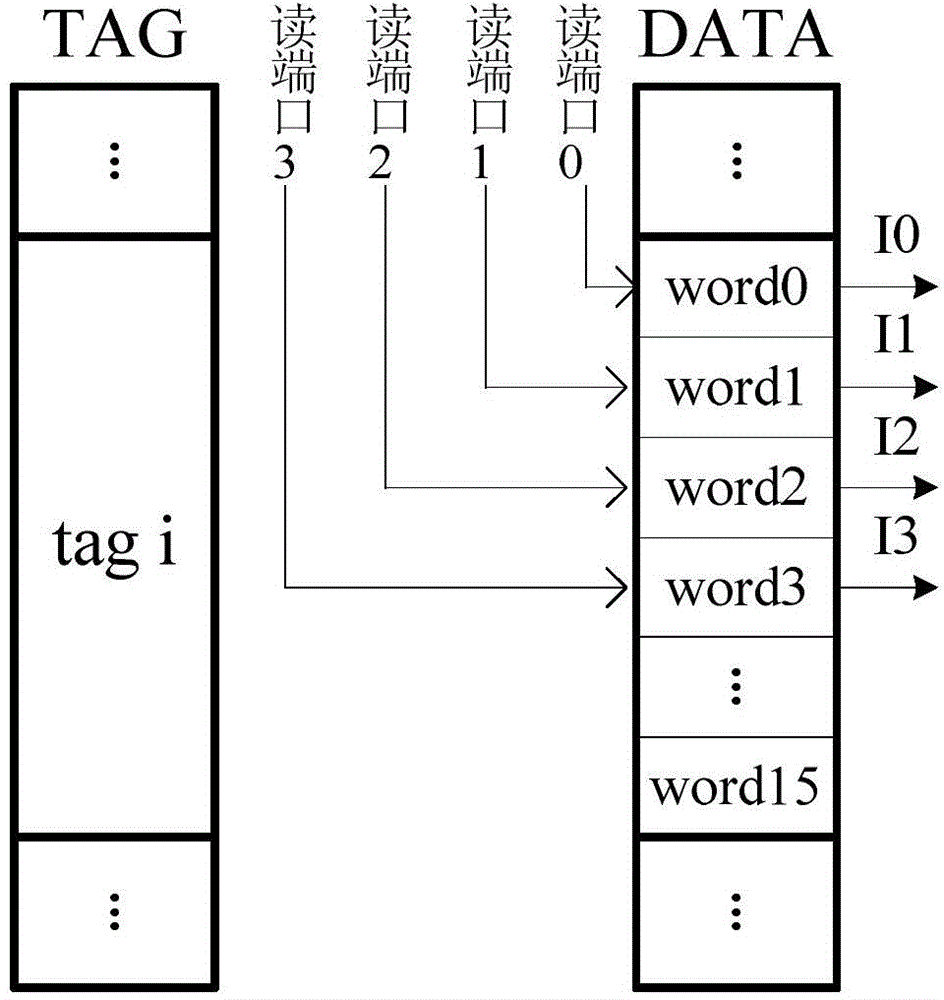

[0030] First, the original unified cache memory is divided into multiple sub-bank parallel storage structures. For example, for a processor whose instruction fetch and execution widths are both M, the cache is divided into M memory banks. Each memory bank only needs A read port can independently perform instruction fetch access, so it can support the maximum instruction fetch bandwidth of the processor as a whole.

[0031] Second, all instructions located in a cache line are addressed in a zigzag manner, that is, the two adjacent lines are connected end to end, and are respectively cached in the M cache banks, so that continuous instruction fetches M instructions are distributed in different memory ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com