Packaging structure for rewiring of packaged two-sided BUMP chip and manufacturing method of packaging structure

A packaging structure and rewiring technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of top-layer chip limitation, overall package size thick, top-layer chip flip position cannot exceed the bottom chip, etc. Achieve the effect of shortening the path, improving the quality, chip size and I/O location flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

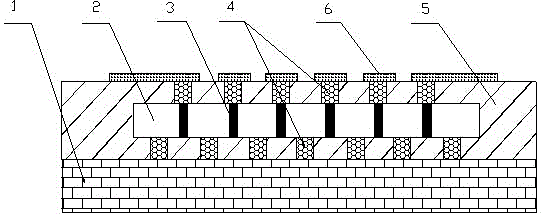

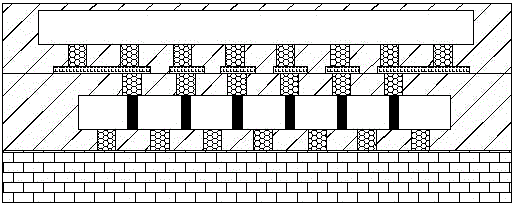

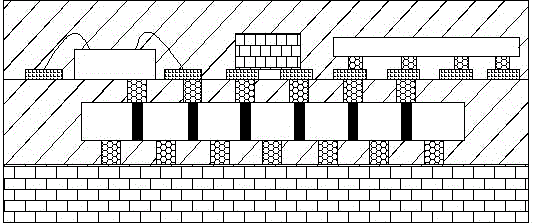

[0044] See figure 1 , The present invention relates to a double-sided BUMP chip encapsulation and rewiring packaging structure, which includes a substrate 1 and a chip 2, on which a plurality of through holes 3 are processed through a silicon via (TSV) process, and the chip 2 Metal bumps (BUMP) 4 are provided on the front and back sides of the chip 2 and the chip 2 is soldered to the front surface of the substrate 1 through the bump 4 on the front side. The bumps 4 on the front and back sides of the chip 2 and the chip 2 are enclosed Plastic compound 5, the front surface of the plastic compound 5 is flush with the top of the bump 4 on the back of the chip 2, and a metal circuit layer 6 is provided on the front surface of the plastic compound 5, and the metal circuit layer 6 is aligned with the bumps on the back of the chip 2. Block 4 is connected.

[0045] The metal circuit layer 6 realizes rewiring after encapsulation, and provides electrical connections for subsequent chips an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More