Packaging structure adopting flexible substrate and TSV chip and manufacturing method of packaging structure

A technology of flexible substrates and packaging structures, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as wire-bonded chips, and achieve the effect of improving quality, improving product performance, and shortening the path

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

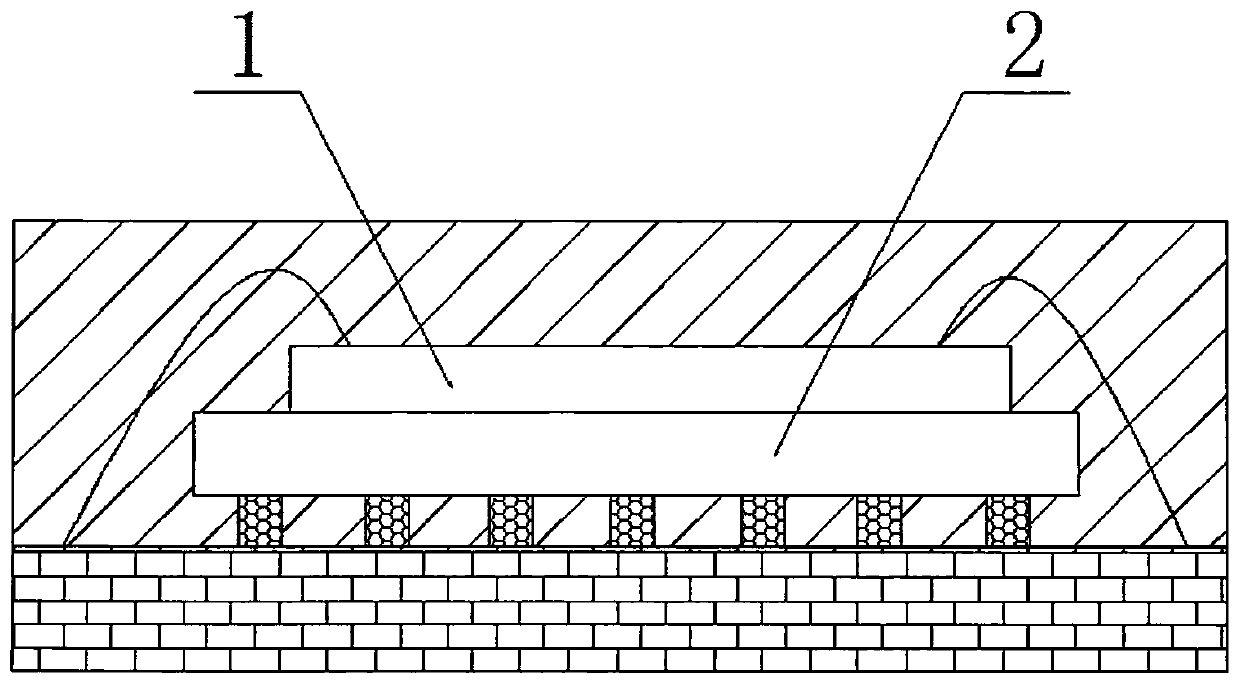

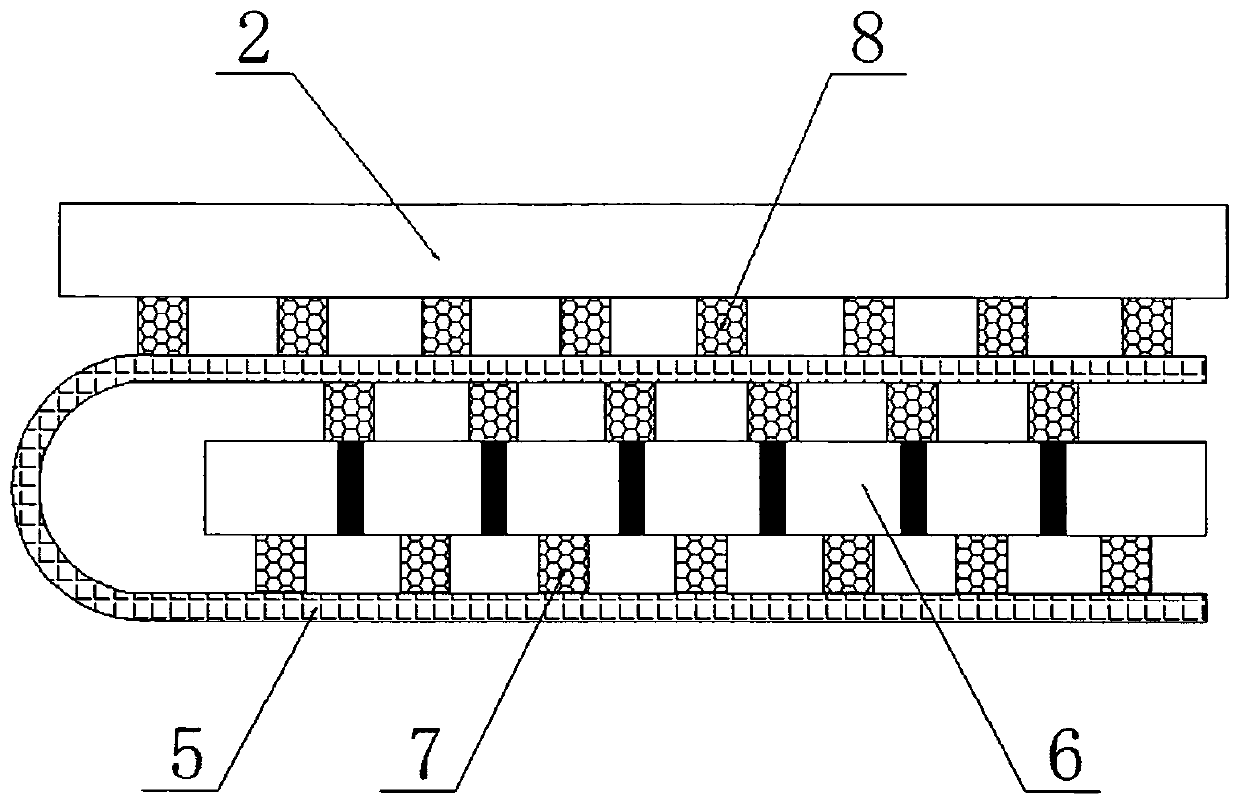

[0045] see image 3 , a packaging structure using a flexible substrate and a TSV chip involved in the present invention, which includes a flexible substrate 5 arranged in a bent manner, a TSV chip 6 is arranged inside the bent part of the flexible substrate 5, and the front and back of the TSV chip 6 Both are connected to the flexible substrate 5 through the first bump 7, and the flip chip 2 is provided on the outer upper surface of the bent flexible substrate 5 through the second bump 8;

Embodiment 2

[0047] see Figure 4 , the difference between embodiment 2 and embodiment 1 is that: the upper surface of the outer side of the flexible substrate 5 that is bent and arranged is provided with a soldered chip 1, a flip chip 2 or an SMT component 9;

Embodiment 3

[0049] see Figure 5 The difference between embodiment 3 and embodiment 1 is that: the flexible substrate 5 is bent multiple times, and a TSV chip 6 is arranged inside each bent portion.

[0050] Its process steps are as follows:

[0051] Step 1, see Image 6 , the chip is processed by TSV according to the requirements, so as to lead the circuit on the surface of the chip to the back of the chip;

[0052] Step two, see Figure 7 , The bumps are made on the front and back of the TSV chip. Before making the bumps, the rewiring process can be added according to the actual needs to realize the rewiring on the surface of the TSV chip, so that the layout of the TSV and the bumps is more reasonable;

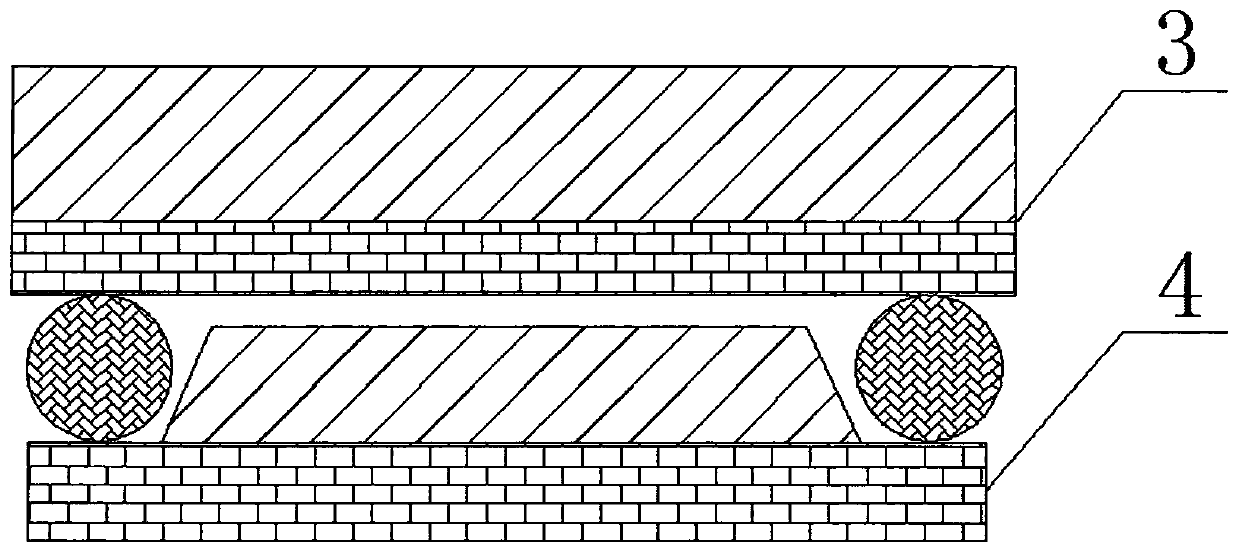

[0053] Step three, see Figure 8 , mount the TSV chip on the flexible substrate by the flip-chip process;

[0054] Step 4, see Figure 9 , bending the flexible substrate, welding the other side of the TSV chip to the other side of the bent flexible substrate, so as to realize the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More