High-voltage device and low-voltage device integrated structure and integrated method

A technology of high-voltage devices and low-voltage devices, which is applied in the field of semiconductor integrated circuit manufacturing, can solve the problems of large device area and light doping concentration, and achieve the effects of reducing device area, low cost, and reducing width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

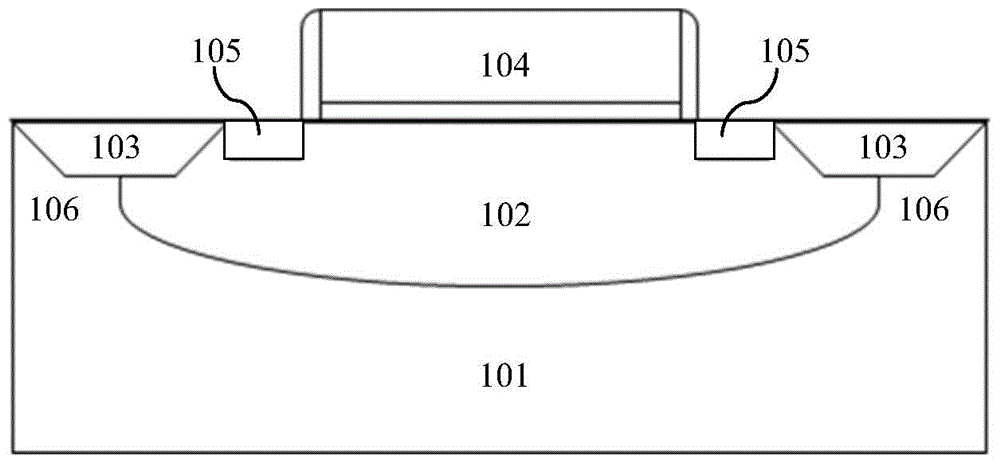

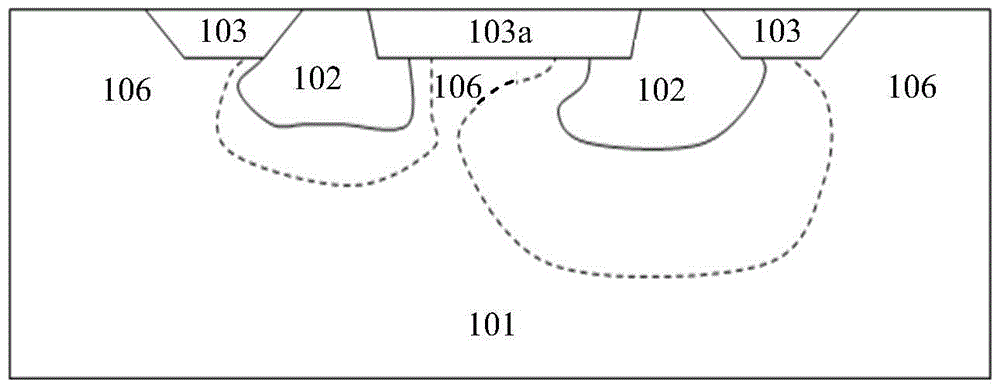

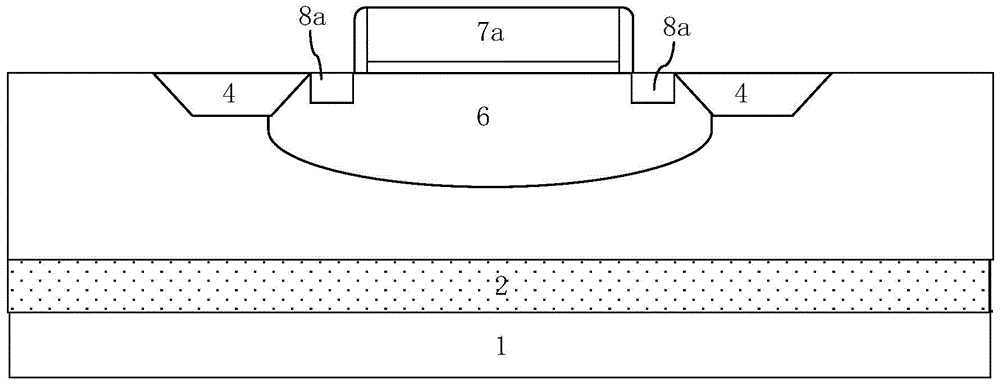

[0038] Such as image 3 As shown, it is a schematic diagram of an NMOS transistor of a low-voltage device with an integrated structure in an embodiment of the present invention; Figure 4 Shown is the schematic diagram of the PMOS tube of the low-voltage device of the integrated structure of the embodiment of the present invention; Figure 5 Shown is a schematic diagram of an N-type high-voltage device with an integrated structure in an embodiment of the present invention; as Figure 6 Shown is a schematic diagram of a P-type high-voltage device with an integrated structure according to an embodiment of the present invention. The low-voltage device of the integrated structure of the high-voltage device and the low-voltage device in the embodiment of the present invention is a CMOS device, and the CMOS device includes an NMOS transistor and a PMOS transistor; the breakdown voltage of the high-voltage device is greater than that of the low-voltage device.

[0039] Both the low...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More