Semiconductor device and formation method

A semiconductor and device technology, applied in the field of semiconductor devices and formation, can solve problems such as threshold voltage drift and degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

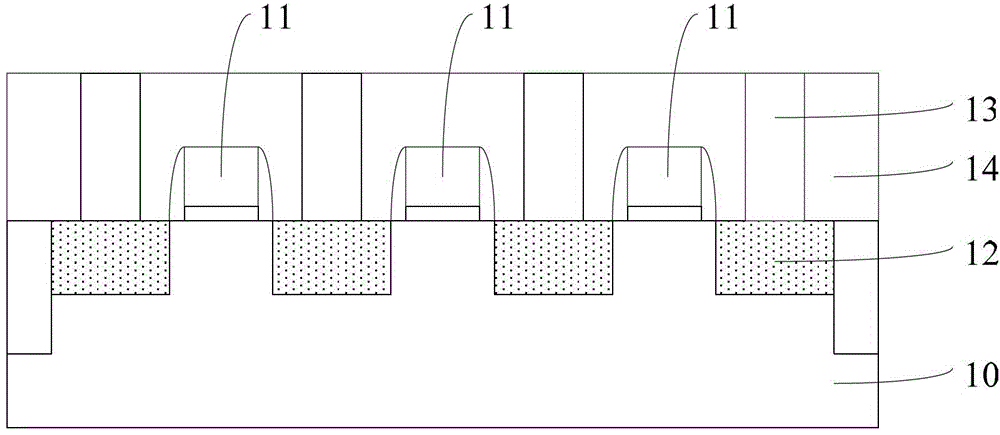

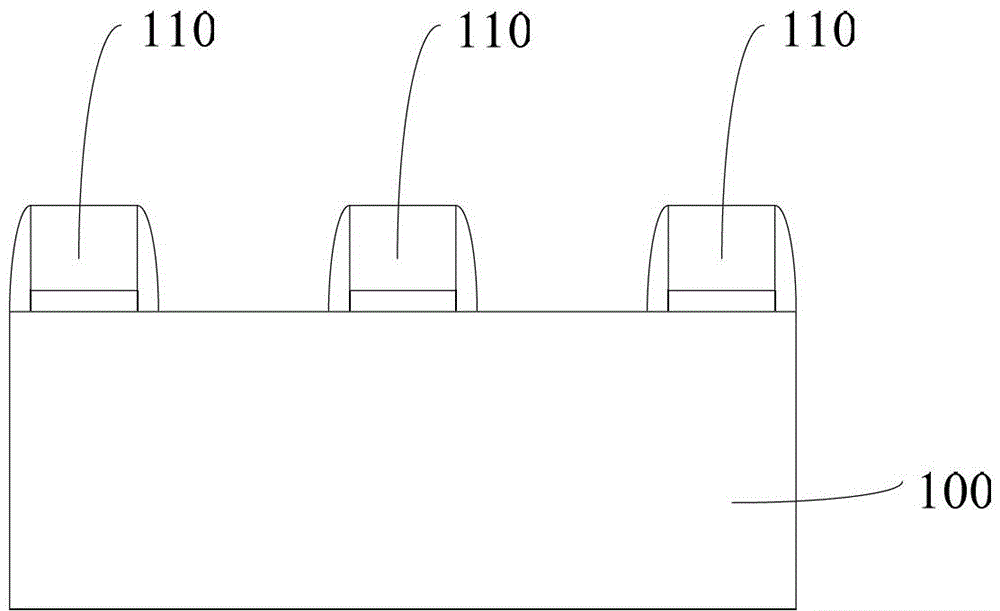

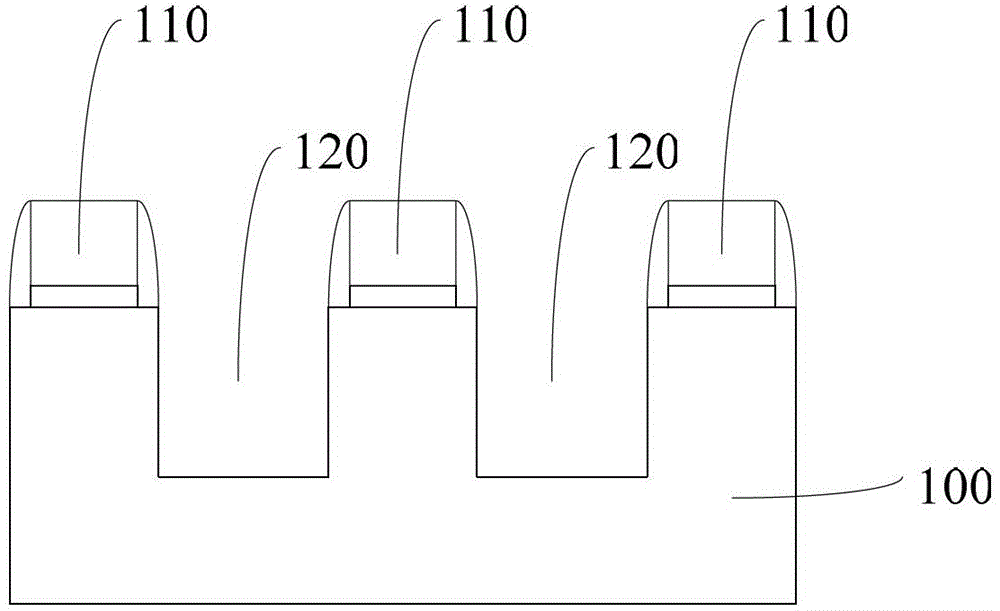

[0026] As described in the background technology, figure 1 In the semiconductor device shown, since the shallow trench isolation structure is not formed between adjacent MOS transistors, there may be leakage current between the channel regions of different MOS transistors, causing problems such as crosstalk, noise margin degradation, and threshold voltage drift. , for this reason, the present invention provides a kind of semiconductor device and its forming method, and the forming method of described semiconductor device comprises: form trench in the semiconductor substrate between adjacent gate structure, utilize selective epitaxial process to form trench in trench An epitaxial layer with protruding morphology is formed on the bottom surface; an insulating layer is formed in the epitaxial layer; a stress layer is formed in the groove, and the stress layer is used as a source and drain region. Since trenches are formed in the semiconductor substrate between adjacent gate struc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More