Chip debugging method and debugging circuit under normal operating mode

A technology of normal working mode and debugging method, which is applied in the direction of measuring electricity, measuring electrical variables, measuring devices, etc., and can solve the problems of complex test sequence output test sequence rapid analysis, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described below in conjunction with the accompanying drawings.

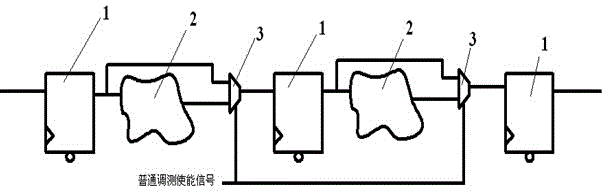

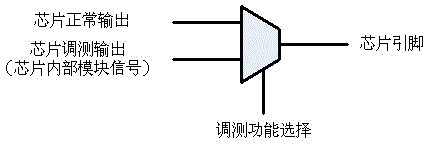

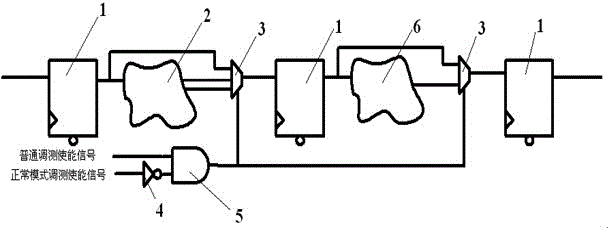

[0022] Usually a chip includes a lot of pins, but these pins will not be used in every working state of the chip at the same time, and the new function definition of the pins that can not be used in the current working state will not affect the normal operation of the chip. Therefore if figure 1 As shown, the chip debugging method in normal working mode provided by the present invention is to use the pin multiplexing technology when the chip pin function is defined, and output the normal function output signal of the chip and the internal signal that needs to be drawn out after multiplexing. To the chip pin, that is, the current output signal of the pin is controlled by the multiplexer, so that the multiplexer can be controlled to output the internal signal as the output value to the pin in the normal working debugging mode.

[0023] Then in the back-end design of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com