System on chip and control method

A technology of system-on-chip and control method, which is applied in the direction of instrumentation, electrical digital data processing, etc., can solve problems such as technical difficulty and high cost, failure to meet design requirements, and inability to further reduce development and upgrade costs, etc., to achieve rich system products Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] Various embodiments of the invention will be described in more detail below with reference to the accompanying drawings. In the various drawings, the same elements are denoted by the same or similar reference numerals. For the sake of clarity, various parts in the drawings have not been drawn to scale.

[0042] The invention can be embodied in various forms, some examples of which are described below.

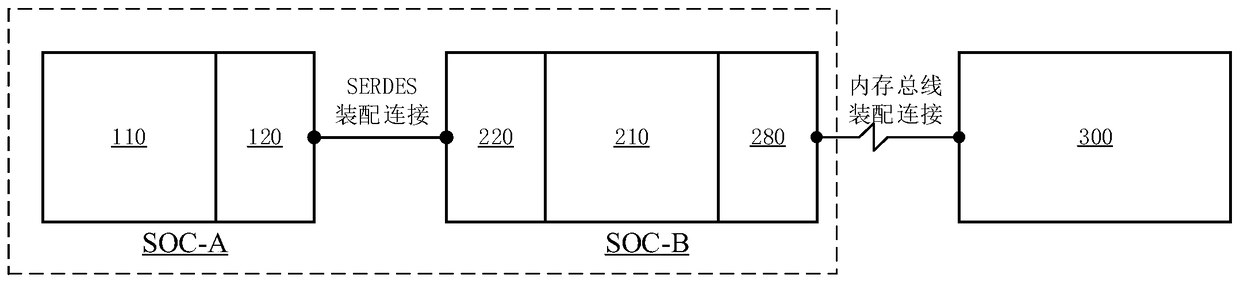

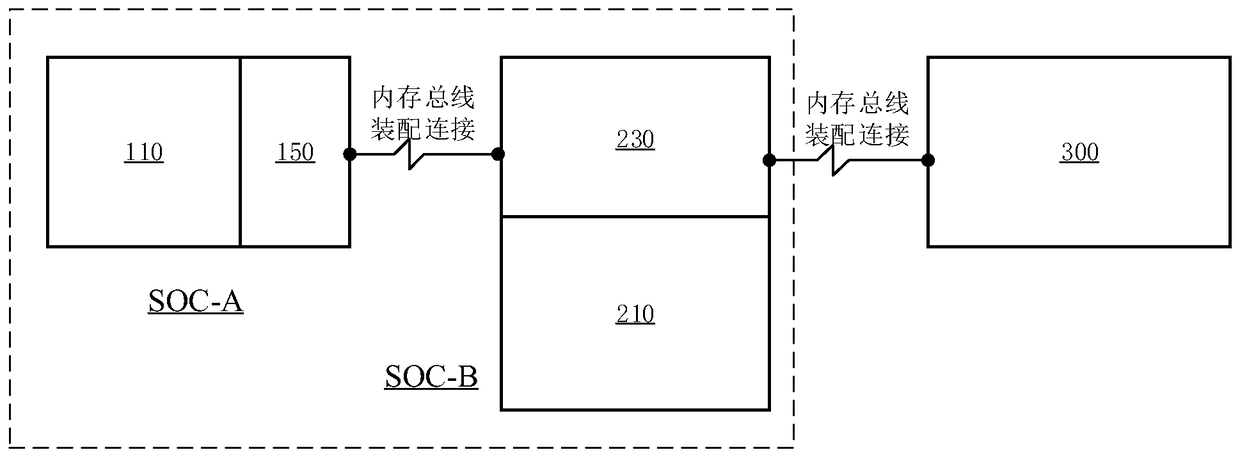

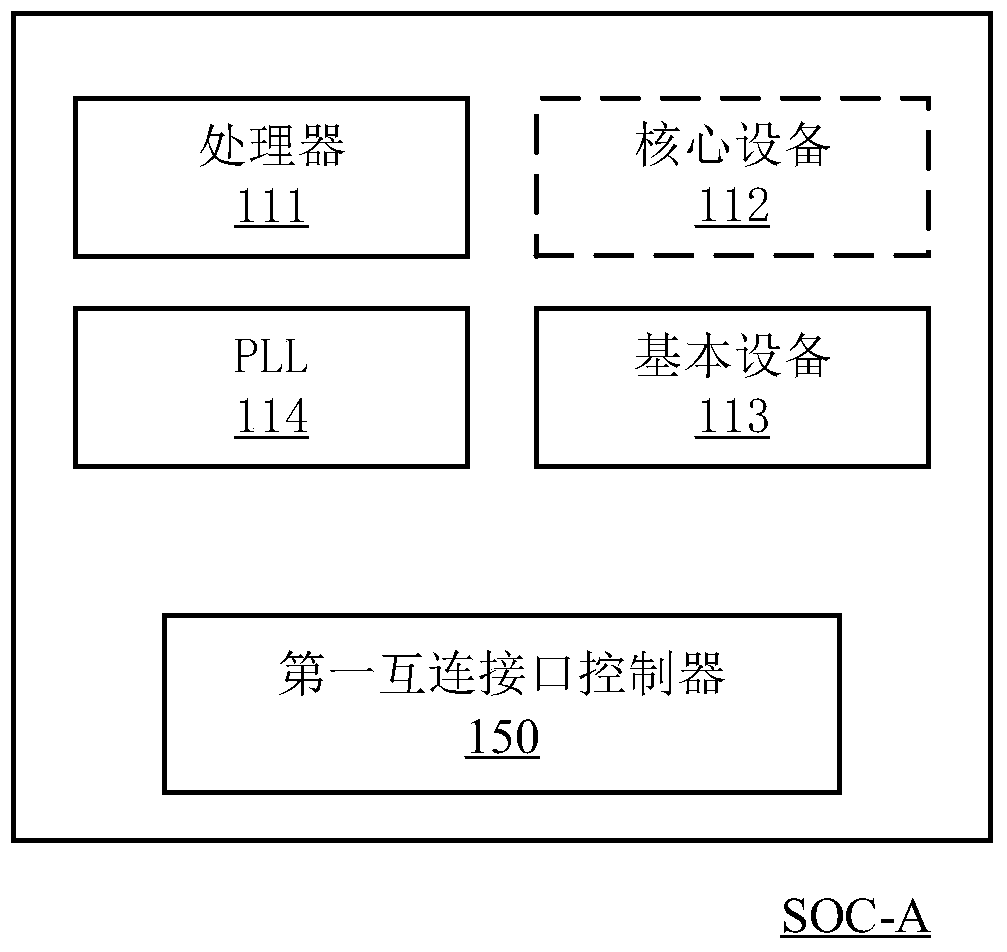

[0043] figure 2 A schematic block diagram of a system on chip and its external memory according to the present invention is shown. As shown in the figure, the SOC is divided into two circuit parts, SOC-A and SOC-B. SOC-A includes a first main function module 110 and a first interconnection interface controller 150 , and SOC-B includes a second main function module 210 and a second interconnection interface controller 230 .

[0044] However, unlike the prior art, a memory bus connection is used between SOC-A and SOC-B. Correspondingly, the first interconnection inte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More