Dependency mesh based instruction-level parallel scheduling method

A scheduling method and instruction-level technology, applied in the field of compilation optimization, can solve the problems of not reflecting the correlation, not reflecting the relationship between instructions and functional units in real time, and not showing other correlations between instructions, so as to achieve the effect of improving parallelism

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The present invention will be further described below in conjunction with the accompanying drawings and specific preferred embodiments, but the protection scope of the present invention is not limited thereby.

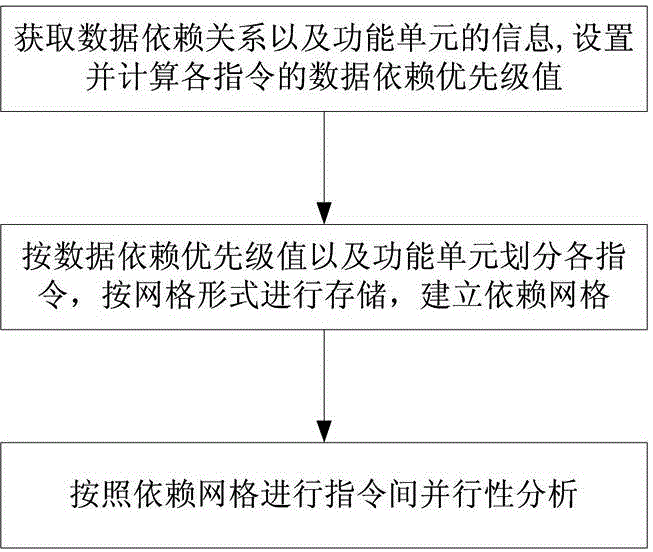

[0041] Such as figure 1 As shown, this embodiment is based on a grid-dependent instruction-level parallel scheduling method, and the steps include:

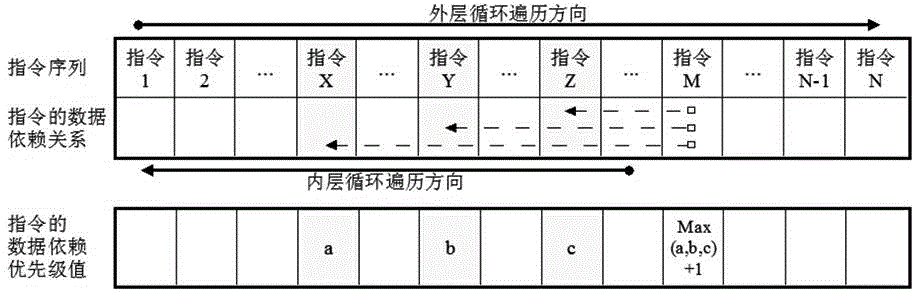

[0042] 1) Obtain the data dependency relationship between instructions in the target basic block and the information of the functional unit corresponding to each instruction, set and calculate the data dependency priority value of each instruction according to the data dependency relationship;

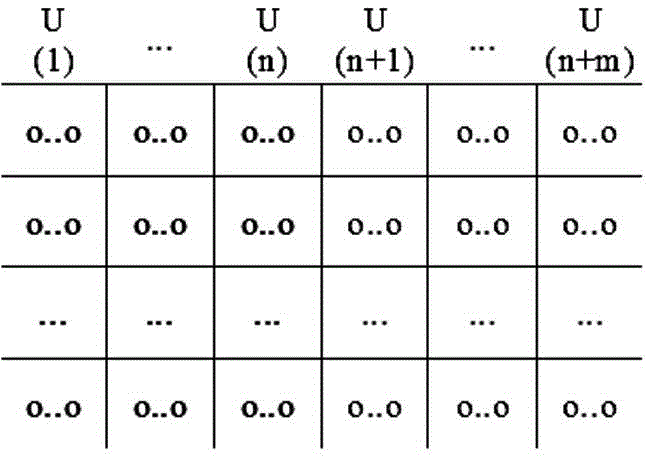

[0043] 2) Divide each instruction according to the data dependency priority value and functional unit, store the divided results in the form of a grid, and establish a dependency grid to obtain the dependency relationship between the instruction and data dependency priority, and the functional unit;

[0044] 3) According t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More