BPSK (Binary Phase Shift Keying) subcarrier related demodulation bit boundary determination circuit and method

A subcarrier and boundary technology, applied in the field of digital correlation demodulation circuit, can solve problems such as uncertainty, and achieve the effect of improving the success rate and simplifying the design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

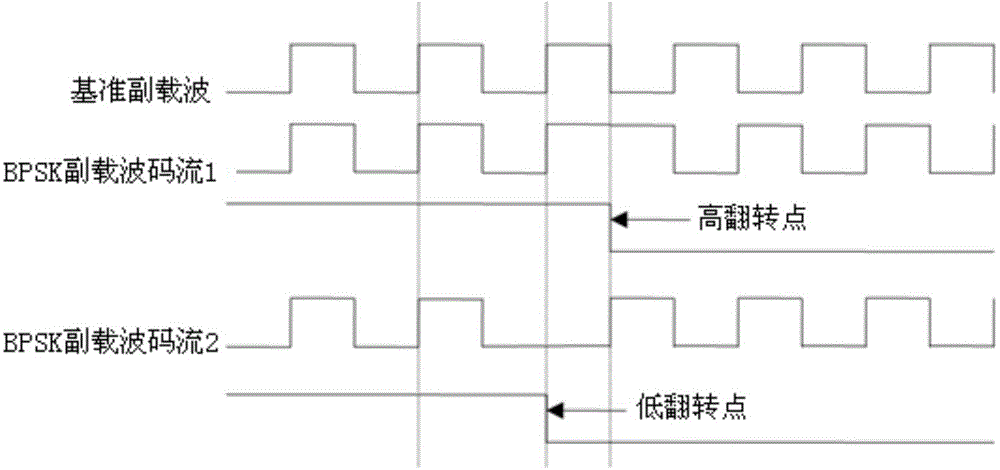

[0028] see figure 2 As shown, in the following embodiments, the BPSK subcarrier-related demodulation bit boundary determination circuit includes: a BPSK subcarrier rising edge counter, a first comparison module, a BPSK subcarrier high level statistical counter, a The second comparison module, a BPSK subcarrier high-low level counter, and a first flip bit boundary signal generation module. The BPSK subcarrier refers to the BPSK subcarrier at the 847k baud rate specified in the ISO / IEC14443 protocol.

[0029] The BPSK subcarrier rising edge counter counts the rising edges of the input BPSK subcarrier, and is used to count the number of BPSK subcarrier signals after the analog receiving circuit is turned on during the bit synchronization period.

[0030] The first comparison module compares the count value of the BPSK subcarrier rising edge counter with a set count threshold to generate a count enable signal, and when the count value of the BPSK subcarrier rising edge counter i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More