n-type buried layer covered semi-superjunction lateral double-diffused metal oxide semiconductor field effect transistor

An oxide semiconductor, lateral double diffusion technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as reducing the lateral breakdown voltage of SJ-LDMOS devices, the P-type column region cannot be completely depleted, and the charge balance is broken. , to achieve the effect of low specific on-resistance, high breakdown voltage, and improving the contradictory relationship

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

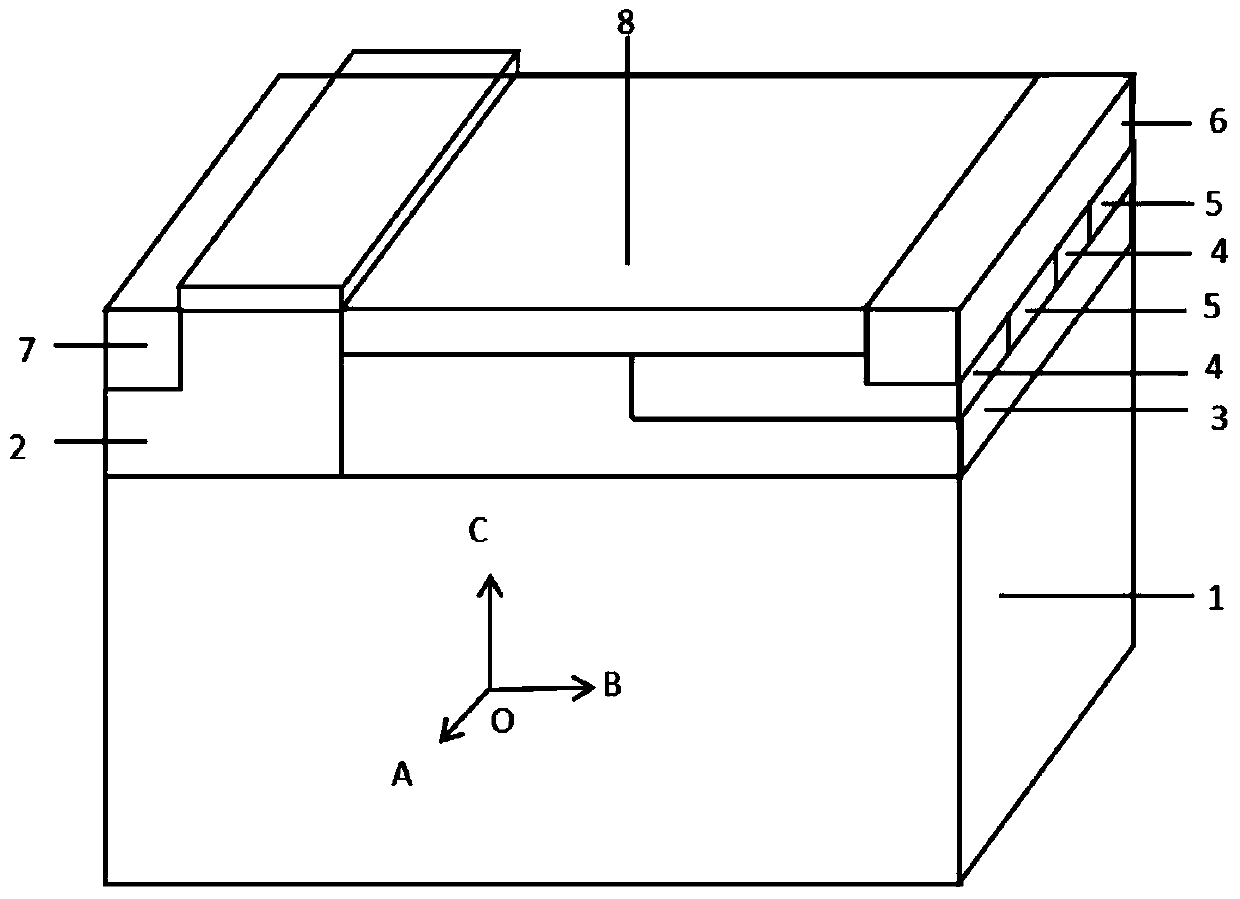

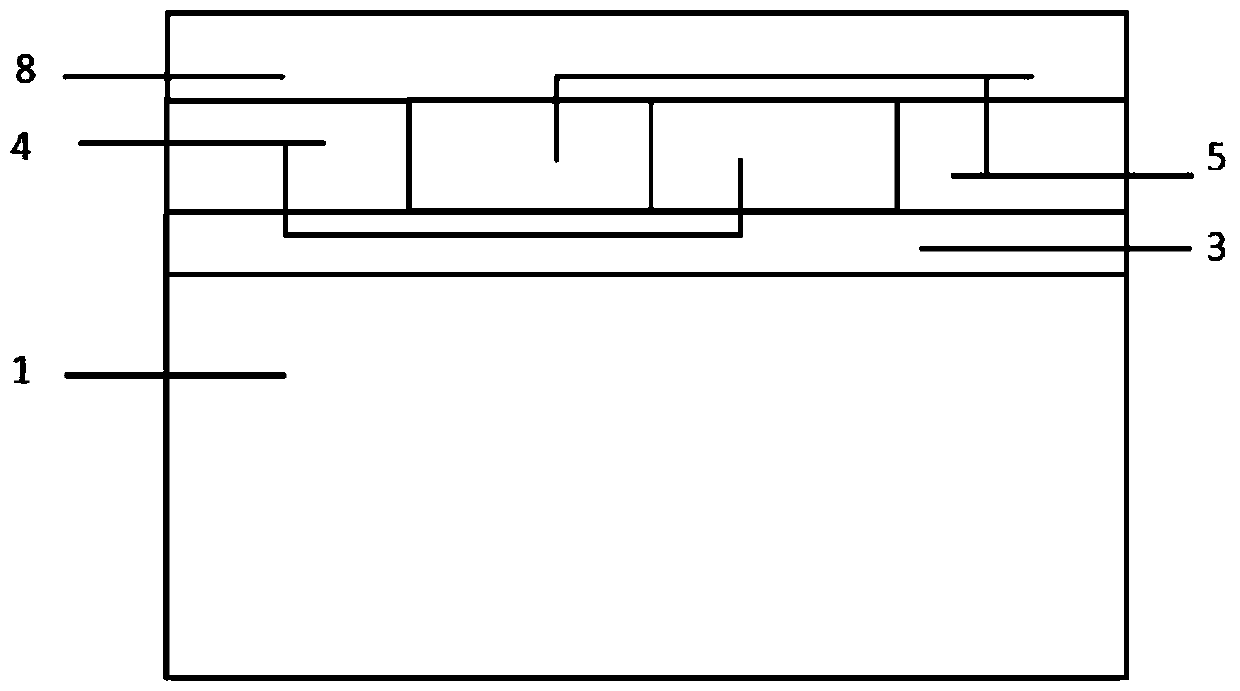

[0027] see figure 1 with figure 2 In the following, an N-type buried-layer-covered (N-channel) semi-superjunction lateral double-diffused metal-oxide-semiconductor field effect transistor is taken as an example to specifically introduce the new structure in the embodiment of the present invention. Those skilled in the art should be able to recognize that this embodiment does not limit the protection scope of the present invention.

[0028] The N-type buried layer covered semi-superjunction lateral double-diffused metal oxide semiconductor field effect transistor includes:

[0029] P-type substrate 1;

[0030] a P-type base region 2 located on the surface of the P-type epitaxial layer on the P-type substrate;

[0031] An N-type source region 7 located on a part of the surface of the P-type base region;

[0032] The semi-super junction region is arranged at intervals between the N-type pillar region 4 and the P-type pillar region 5 (two cycles are shown in the figure), and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More