Monitoring layout and monitoring method of gate process

A gate and process technology, applied in the field of gate process monitoring layout, can solve the problems of process step deviation, low semiconductor production yield, poor reliability of monitoring results, etc., and achieve the effect of high reliability and accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

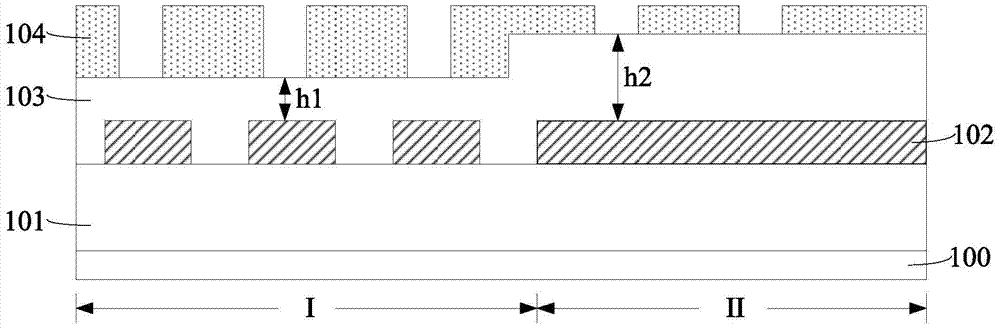

[0037] It can be seen from the background art that the monitoring reliability of the gate process in the prior art is poor, and it is difficult to judge whether there is a deviation in the gate process, resulting in a low yield rate of semiconductor production.

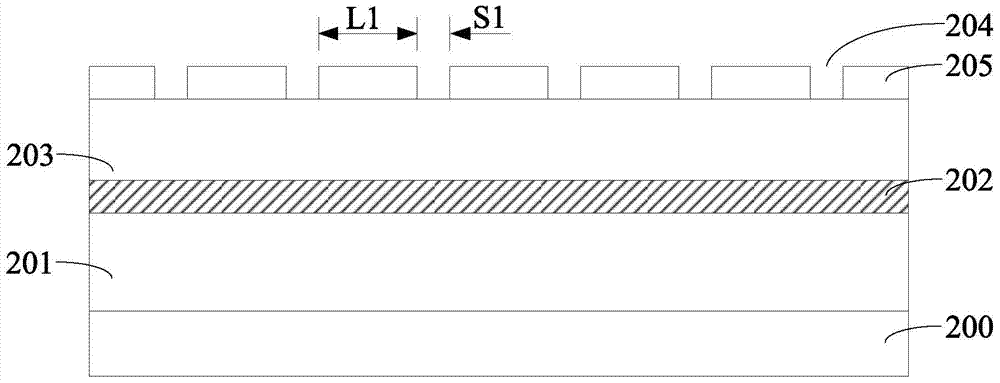

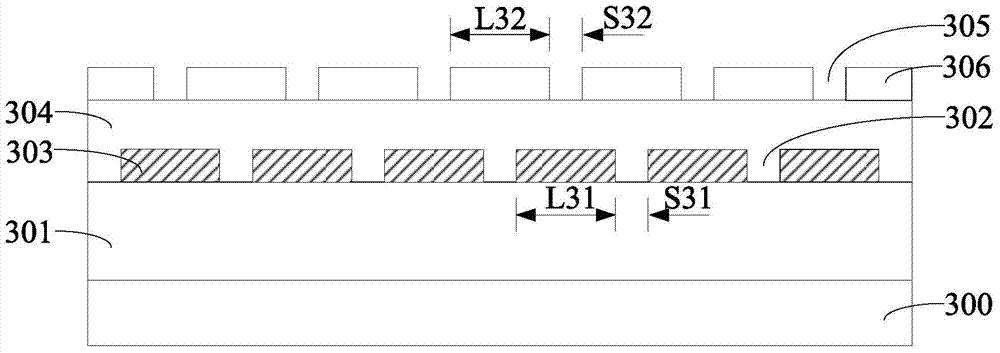

[0038]The OCD monitoring method for the characteristic size of the gate process is studied. The monitoring of the gate process includes after development inspection (ADI: After Develop Inspection) and after etching inspection (AEI: After Etch Inspection). Among them, post-development inspection refers to It is: after the patterned photoresist is formed, the characteristic size and alignment characteristics of the patterned photoresist are monitored. Post-etching monitoring refers to: after the etching process is completed, the pattern formed by etching Monitoring of feature size and alignment characteristics. Through the analysis of ADI monitoring data and AEI monitoring data, it can be judged whether the gate process...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More