Method for processing synchronous logic structures in gate-level netlist

A gate-level netlist and synchronous logic technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of long time and large consumption of human resources, and achieve the effect of shortening the time period and saving human resources.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

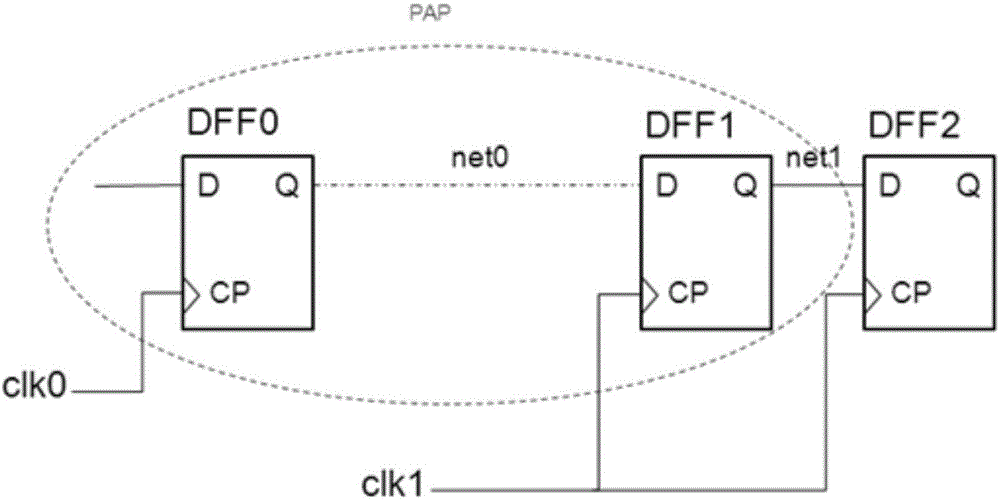

[0025] A kind of method of processing the synchronous logic structure in the gate-level netlist of the present invention, specifically comprises the following steps:

[0026] The first step, utilize TCL and Perl script to find out the structure of all two register cascades in the gate-level netlist to be processed, that is, the Q terminal (output terminal) of one register DEF1 is directly connected to the D terminal (input terminal) of another register DEF2 The structure of the terminal) is aggregated into element table 1 as follows, and each cascade structure is a table element:

[0027] Table 1

[0028] [( / her0 / her1 / her2 / … / DFF1_0000),( / her0 / her1 / her2 / … / DFF2_0000)]

[0029] [( / her0 / her1 / her2 / … / DFF1_0001),( / her0 / her1 / her2 / … / DFF2_0001)]

[0030] [( / her0 / her1 / her2 / … / DFF1_0002),( / her0 / her1 / her2 / … / DFF2_0002)]

[0031] [( / her0 / her1 / her2 / … / DFF1_0003),( / her0 / her1 / her2 / … / DFF2_0003)]

[0032] [( / her0 / her1 / her2 / … / DFF1_0004),( / her0 / her1 / her2 / … / DFF2_0004)]

[0033] [( / her0 / her1 / her2 / ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com