Time-interleaved pipeline-sar type adc circuit

A technology of time interleaving and circuit, applied in the direction of electrical components, electrical signal transmission systems, signal transmission systems, etc., can solve the problems of system performance degradation, lower conversion rate, increase of circuit complexity and power consumption, etc., to reduce hardware resources and Clock signal drive circuit, effect of power consumption and area reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

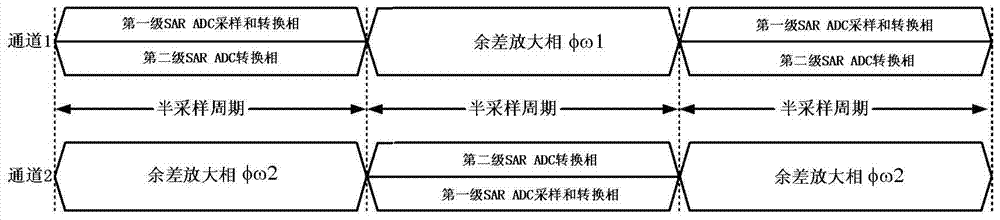

[0018] The time-interleaved Pipeline-SAR ADC circuit of the present invention reduces the mismatch of offset voltages between two channels by sharing a comparator between the two channels.

[0019] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

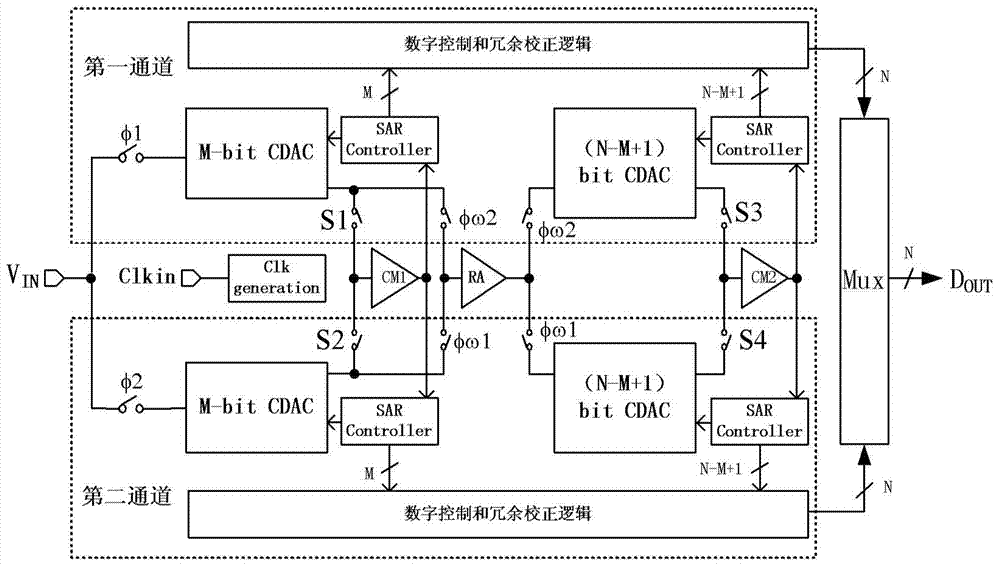

[0020] In an exemplary embodiment of the present invention, a time-interleaved Pipeline-SAR ADC circuit is provided. figure 2 It is a schematic circuit diagram of a time-interleaved Pipeline-SAR ADC circuit according to an embodiment of the present invention.

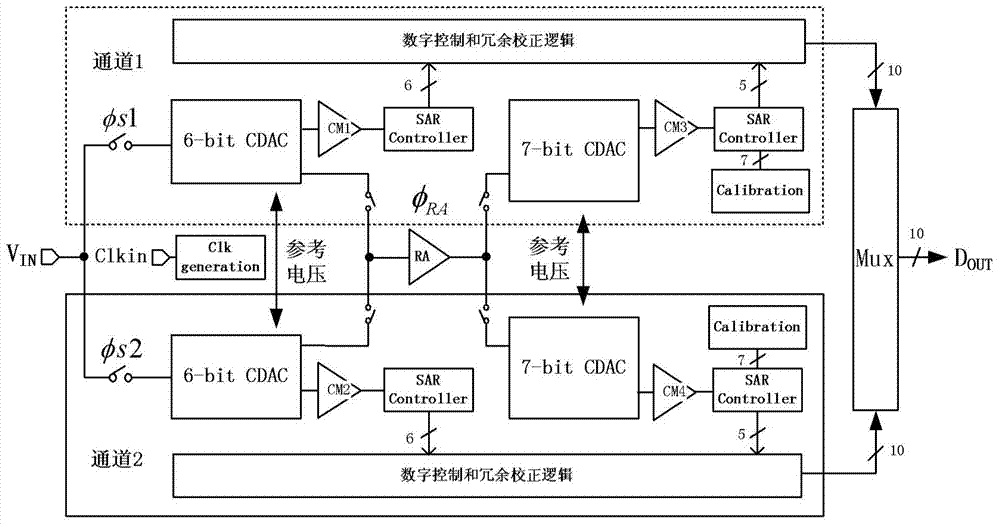

[0021] Please refer to figure 1 and figure 2 , the time-interleaved Pipeline-SAR ADC circuit and figure 1 The shown time-interleaved Pipeline-SAR ADC circuit has a similar structure, both of which are composed of two identical upper and lower channels, and the two channels...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More