A method of acquiring topology information of fpga based on text tree structure model

A technology of text tree structure and topology information, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of ISE software, such as large amount of information, not convenient enough, unable to file output topology information, etc., to improve the module The effect of topological relationship partition efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

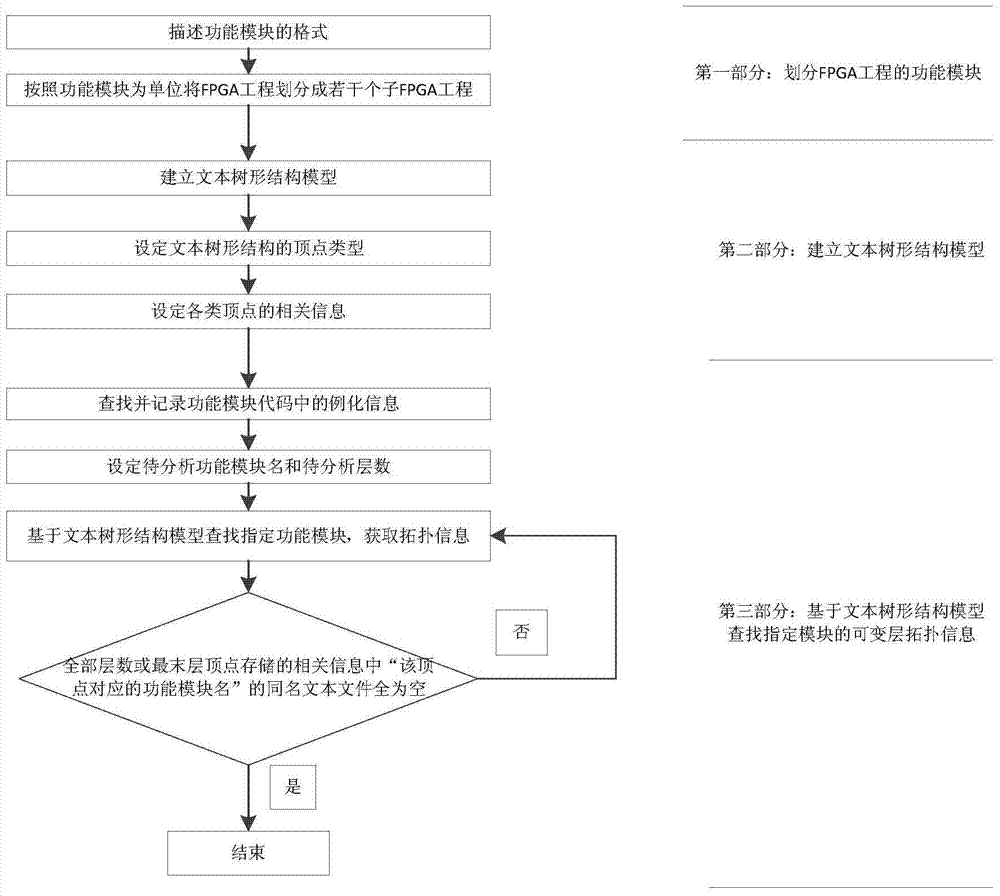

[0039] The core idea of the present invention is to divide the FPGA project into modules, and establish a text tree structure model describing the topological relationship between the modules, then complete the text information abstraction of the topological relationship information based on the text tree structure model, and finally store it in a text file and Output module topology information.

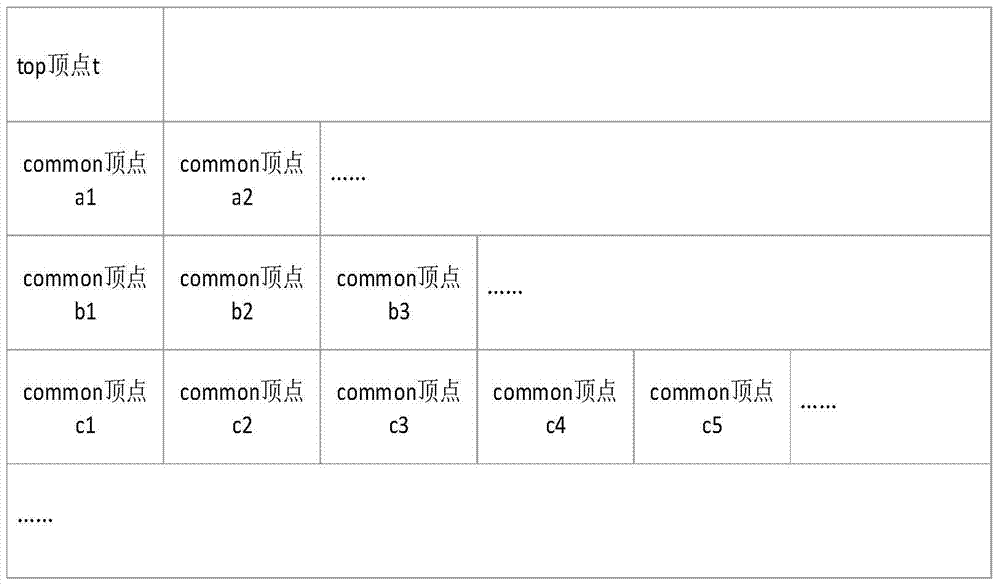

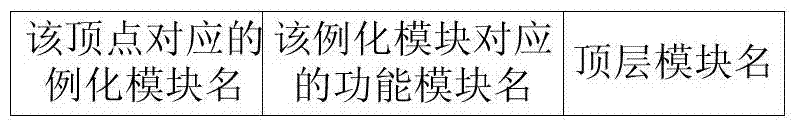

[0040] refer to figure 1 , the present invention a kind of FPGA topological relationship division method based on text tree structure model, its realization steps are as follows

[0041] Part 1: Divide the functional modules of the FPGA project

[0042] Step 1: Establish a function module, the code segment format of the function module includes three parts, namely the first part is the library reference part marked by the keyword library, the second part is the entity part marked by the keyword entity, and the second part is the entity part marked by the keyword entity. The thre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More