Array substrate and manufacturing method thereof, display panel and display device

A technology for array substrates and display panels, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

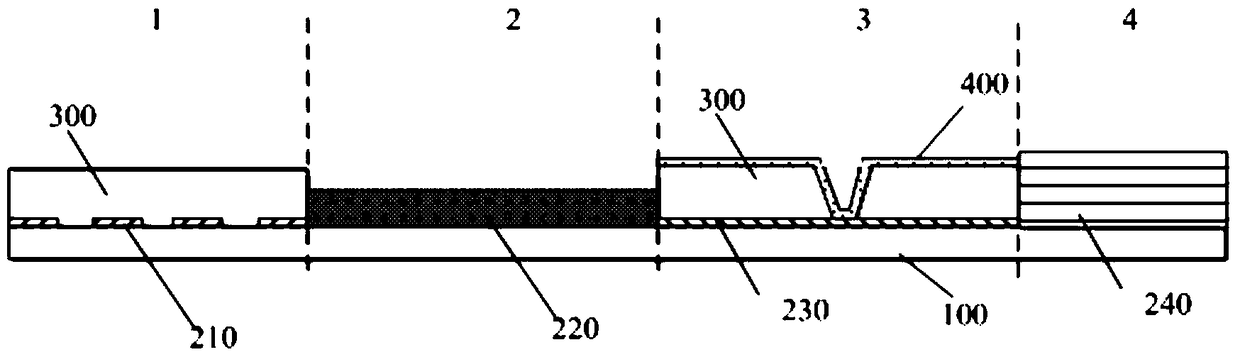

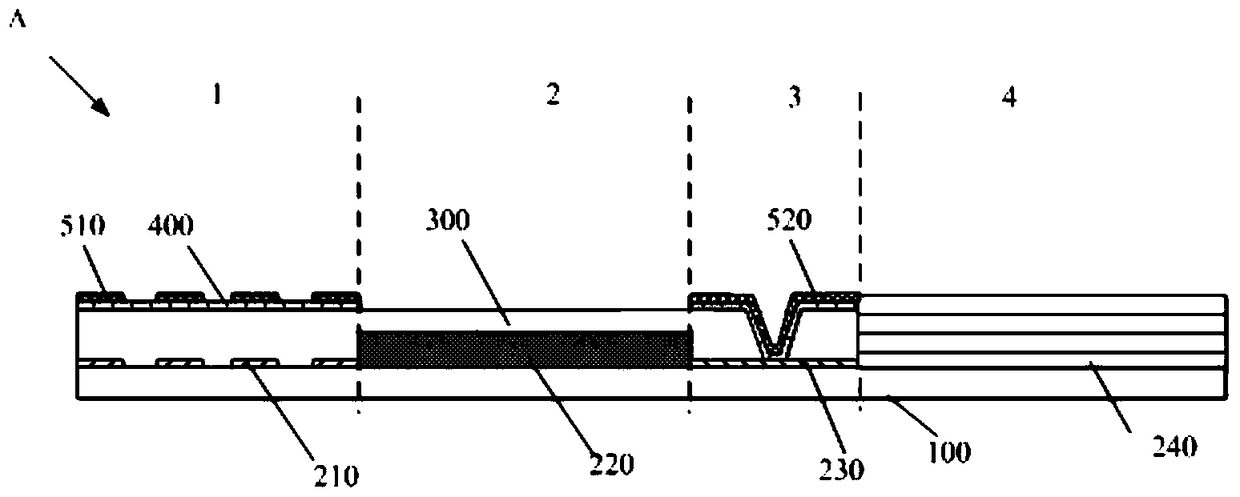

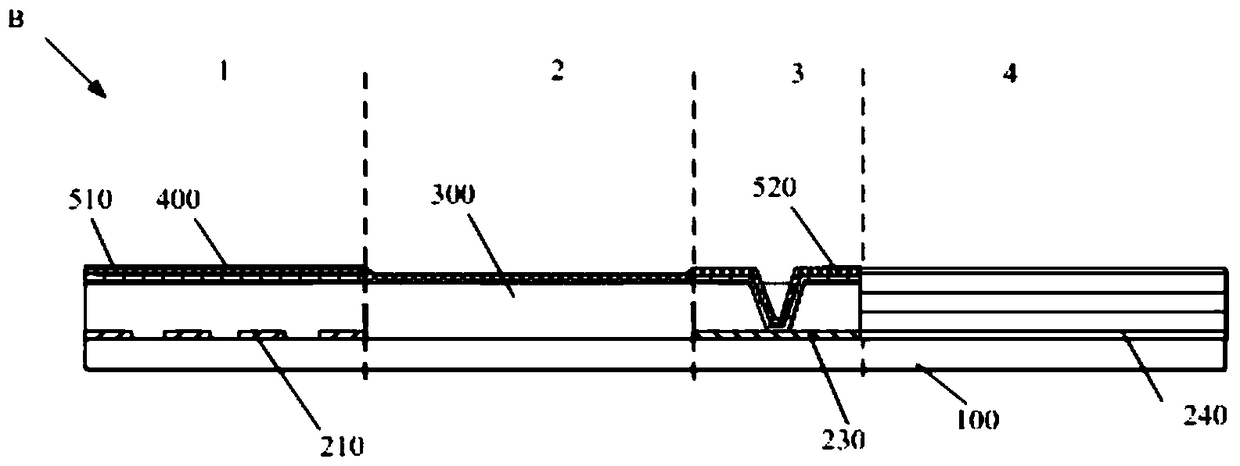

[0055] For the array substrate provided in Embodiment 1 of the present invention, please refer to figure 2 , image 3 and Figure 4 ,in figure 2 for in Figure 4 The schematic cross-sectional view at A shown in, image 3 for in Figure 4 The schematic cross-sectional view at B shown in ; the array substrate includes: a substrate 100, which can be divided into four regions 1, 2, 3, and 4 according to the structure formed above the substrate 100; specifically, Area 1 is a GOA signal line area, and the array substrate has a GOA signal line 210 on the base 100 in this area; Area 2 is a GOA area, and the array substrate has a GOA circuit 220 on the base 100 in this area, see Figure 4 , the GOA circuit 220 includes a plurality of shift register units 221 cascaded together, and each shift register unit 221 includes a plurality of thin film transistors (not shown); area 3 is the common electrode wiring (COM) area, the array substrate has a first common electrode wiring 230 on...

Embodiment 2

[0072] The structure of the array substrate provided by Embodiment 2 of the present invention may refer to Figure 5 , Image 6 and Figure 7 ,in Figure 5 for in Figure 7 The schematic cross-sectional view at A shown in, Image 6 for in Figure 7The schematic cross-sectional view at B shown in ; in Embodiment 2 of the present invention, the gate drive circuit trace 210, the gate drive circuit 220, the first common electrode trace 230, the second common electrode trace 510, and the conductive connection part 520 is also provided with an insulating layer 300, the insulating layer 300 is provided with a via hole at the position of the first common electrode trace 230, the first common electrode trace 230 and the conductive connection part 520 are connected through the via hole; Figure 2-Figure 4 The structure of the array substrate is different in that the gate driving circuit wiring 210 , the gate driving circuit 220 and the first common electrode wiring 230 are located ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More