Circuit and method for achieving two keys on single PAD

A button and circuit technology, which is applied in the field of integrated circuit input control, can solve the problems of increased chip packaging cost, unsolvable error identification, increased chip cost, etc., to reduce the area of pins and packaging, avoid the problem of key strings, and save Effects of PAD resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other.

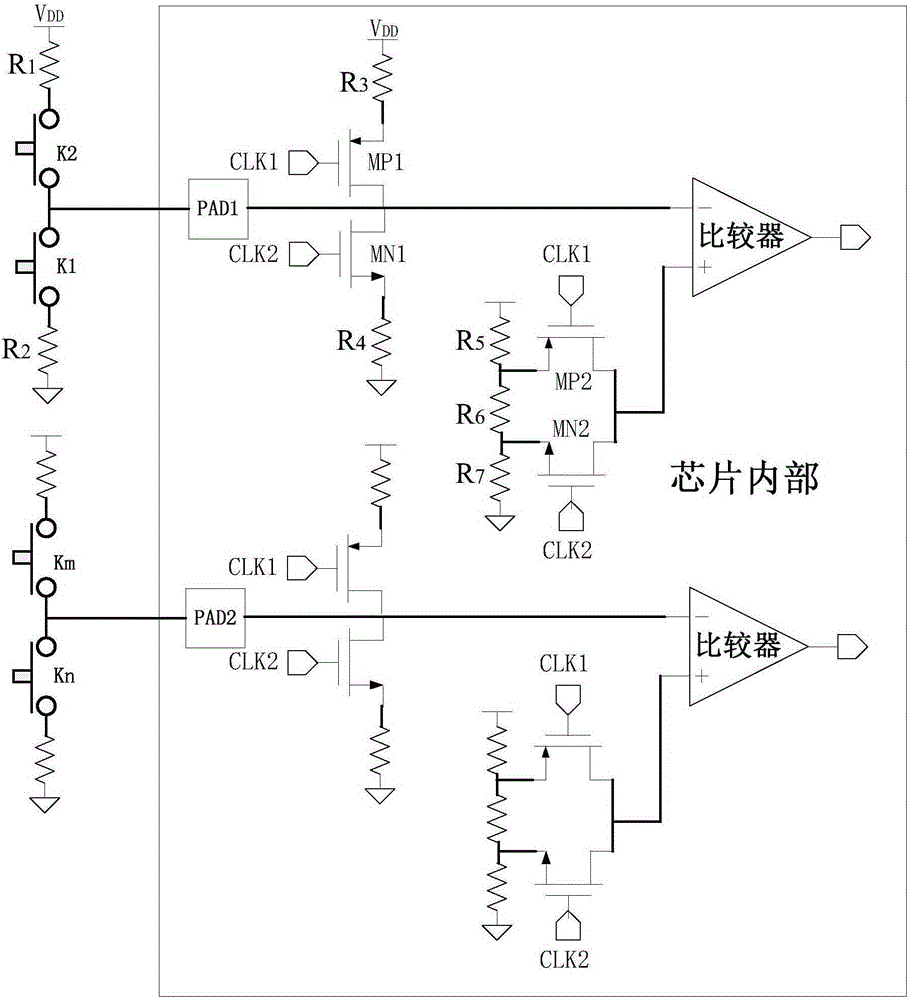

[0027] Such as image 3 As shown, a single PAD circuit realizes two buttons, which includes a first button K1, a second button K2, PAD pins PAD1 / PAD2, a first button sampling circuit, a second button sampling circuit, a reference voltage, a comparator And button identification circuit (not shown in the figure); one end of the first button K1 is connected to the PAD pin PAD1, and the other end is connected to the power supply VDD through the first resistor R1; one end of the second button K2 is connected to the PAD pin PAD1 , and the other end is grounded through the second resistor R2; the output ends of the sampling circuit of the first button K1 and the sampling circuit of the second button K2 are connected with the PAD pin PAD1, and are used for discontinuously testing the first button K1 and the second...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More