Sapphire-substrate single-electrode LED chip structure and preparation method thereof

A sapphire substrate and LED chip technology, which is applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of restricting the light extraction rate of small-sized chips, achieve the effect of reducing the proportion of electrode area and improving the light extraction rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

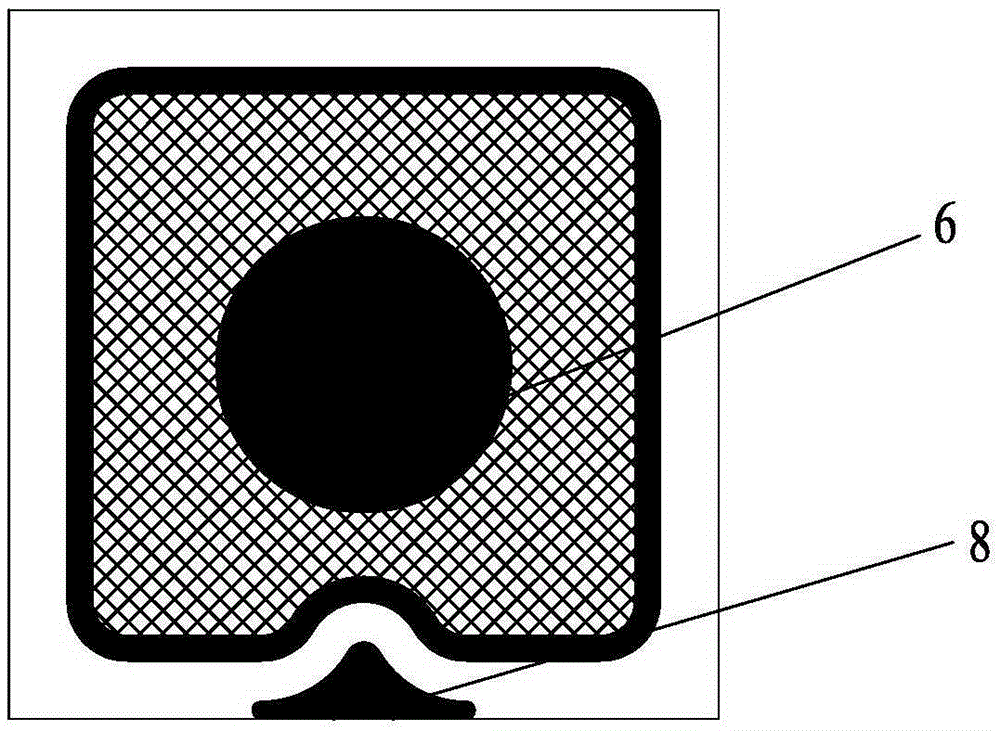

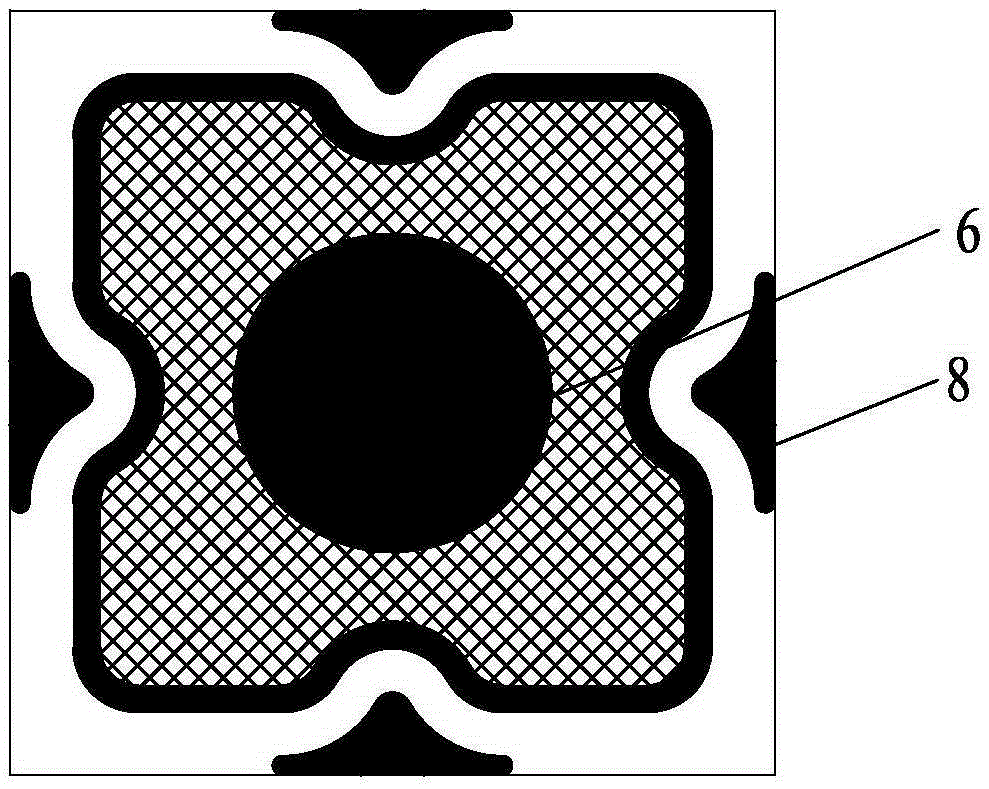

[0039] Such as Figure 1 ~ Figure 3 , Figure 7 As shown, the sapphire substrate single-electrode LED chip structure of the present invention includes a sapphire substrate 1, and an epitaxial structure layer is grown on the sapphire substrate 1, and the epitaxial structure layer includes a U-GaN layer 2, an N-GaN layer 3, an MQW layer 4 and the P-GaN layer 5, the MQW layer 4 and the P-GaN layer 5 are partially etched to expose the N-GaN layer 3, an ITO layer 9 is provided on the P-GaN layer 5, and a positive electrode 6 is provided on the ITO layer 9; One side of the sapphire substrate 1 (such as figure 1 shown), multiple sides (such as figure 2 shown) or multiple sides (such as image 3 As shown), the inclined grooves 7 are arranged respectively, the inclined grooves 7 extend from the upper surface of the N-GaN layer 3 to the lower surface of the sapphire substrate 1, and the inclined grooves 7 are half or 1 / 4 of a conical hole; The sidewall of the chute 7 is covered wit...

Embodiment 2

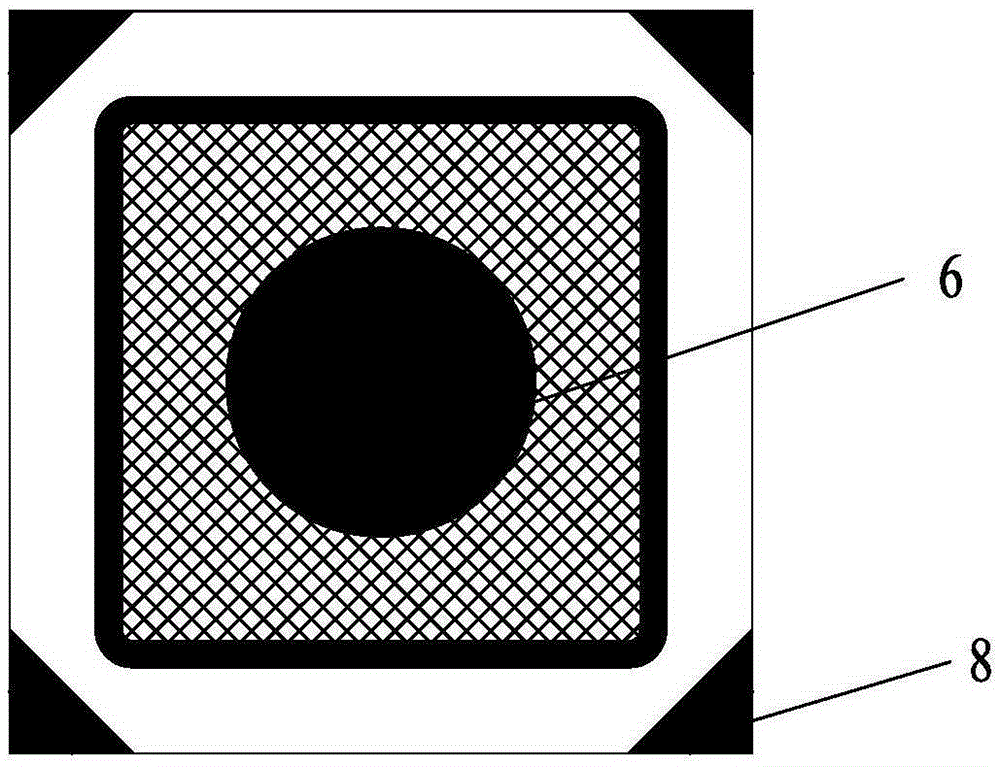

[0048] Such as Figure 4 ~ Figure 6 , Figure 10 As shown, the sapphire substrate single-electrode LED chip structure of the present invention includes a sapphire substrate 1, and an epitaxial structure layer is grown on the sapphire substrate 1, and the epitaxial structure layer includes a U-GaN layer 2, an N-GaN layer 3, an MQW layer 4 and the P-GaN layer 5, the MQW layer 4 and the P-GaN layer 5 are partially etched to expose the N-GaN layer 3, an ITO layer 9 is provided on the P-GaN layer 5, and a positive electrode 6 is provided on the ITO layer 9; One side of the sapphire substrate 1 (such as Figure 4 shown) or multiple sides (such as Figure 5 As shown), a slanted groove 7 is provided, and the slanted groove 7 extends from the upper surface of the N-GaN layer 3 into the sapphire substrate 1 , and the side wall of the slanted groove 7 is covered with a metal layer with a thickness of 1-5 μm to form a negative electrode 8 .

[0049]The preparation method of the sapphir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More