Technology mapping method of multipath selector based on FPGA

A technology of multiplexer and process mapping, which is applied in the field of process mapping of multiplexers, can solve problems such as occupation, and achieve the effects of saving occupation, reducing logic delay, chip efficiency and area optimization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

[0024] The methods in the following embodiments of the present invention are implemented based on CMEM5 or CMEM7FPGA devices. In order to better understand the technical solutions provided by the embodiments of the present invention, the logic structure of the CMEM5 / M7FPGA devices is briefly described first.

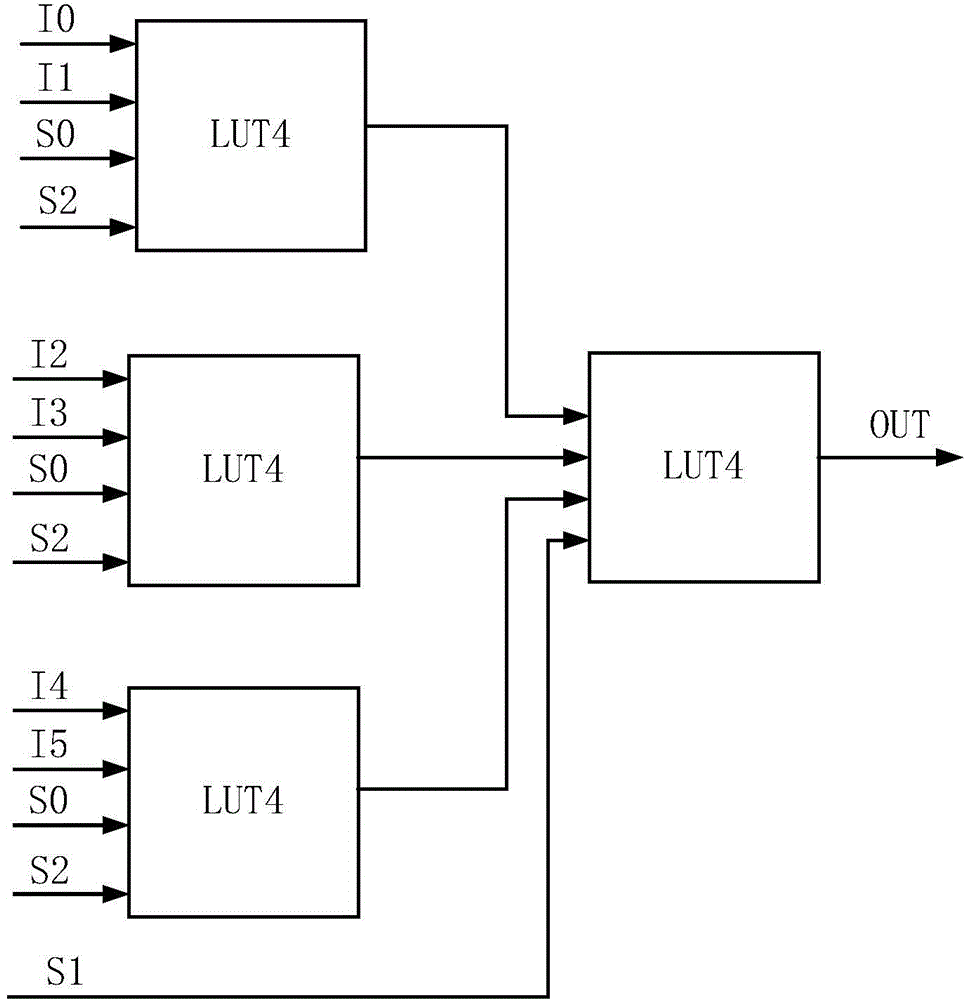

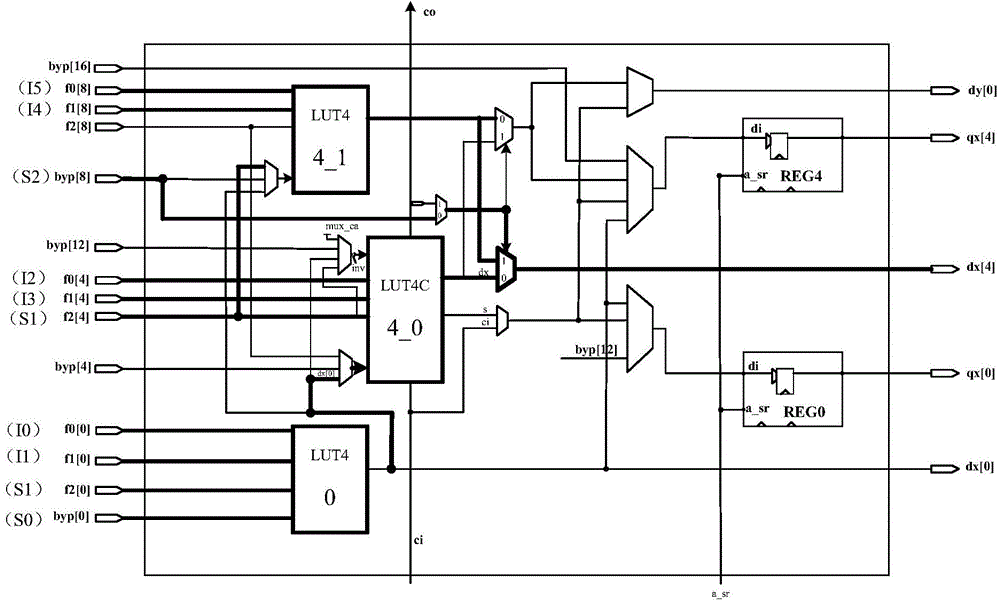

[0025] In the architecture of CMEM5 / M7FPGA, the FPGA chip includes multiple logic units (LogicElement, LE), each LE includes multiple logic areas (LogicParcel, LP), and each LP includes two four-input look-up tables LUT4, 1 LUT4C (LUT4 with carry chain) and two registers.

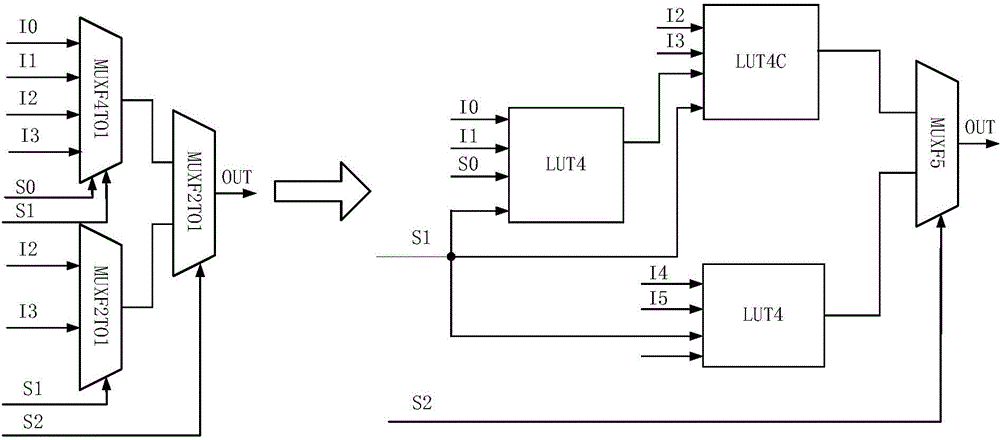

[0026] figure 2 Schematic diagram of the logical mapping of the one-of-six selector provided by the embodiment of the present invention; image 3 based on figure 2 The logic mapping provided is the logic mapping diagram of the six selecto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com