Design method for displaying starting-up schedule at Post stage of server

A design method and server technology, applied in the direction of instrumentation, calculation, electrical digital data processing, etc., can solve problems such as the inability to obtain the system startup progress and affect the user's operation experience, and achieve the goal of improving product competitiveness, simple and reliable solutions, and low cost Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

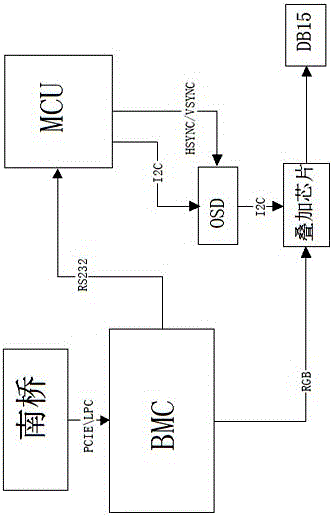

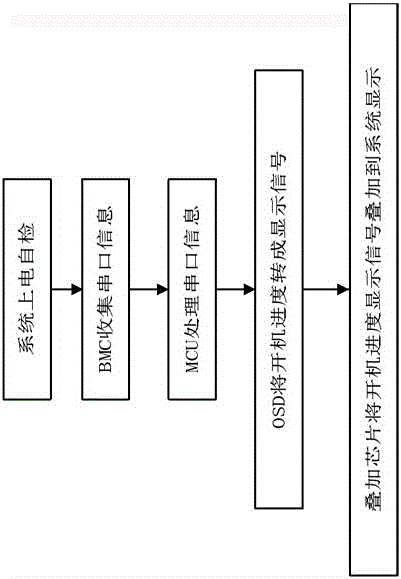

[0031] Such as figure 1 As shown, a design method for displaying the boot progress in the server Post stage, the method applies the video overlay technology to the motherboard design in the server, and controls the MCU, OSD (on-screen display) chip and video overlay chip, each component They are interconnected through the bus, and the boot progress information is displayed on the display, among which:

[0032] 1) BMC (BaseManagementController, Baseboard Management Controller): Integrate the network card function, interconnect with the in-band south bridge chip, interact with the in-band and out-of-band system, obtain the system startup progress information, and send data to the MCU through the serial port; among them The south bridge chip is a part of the host system, interconnected with the BMC through the PCIE and LPC bus, and can send the boot information to the BMC in real time;

[0033] 2) MCU: Process the boot progress data sent by BMC, make the data into display data a...

Embodiment 2

[0037] On the basis of Embodiment 1, the MCU described in this embodiment has UART and I2C interface functions, and the UART interface is interconnected with the BMC in the server system to obtain system startup progress information, and the data is sent to the OSD chip through the I2C bus. Process the boot progress information and send it to the OSD for display signal conversion, and at the same time the MCU will send a video synchronization signal (HSYC\VSYC) to the OSD to control the position and size of the displayed image on the display.

Embodiment 3

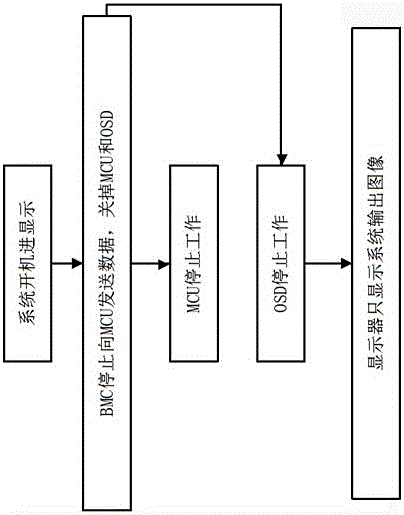

[0039] On the basis of Embodiment 2, the system startup progress display in this embodiment is only before the system enters the display state in the post stage. When the system is turned on and enters the display state, the BMC will notify the MCU to turn off the OSD chip and cancel the system startup progress. show.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More