Current mirror for effectively inhibiting power source voltage influence

A power supply voltage and current mirror technology, applied in the direction of adjusting electrical variables, control/regulating systems, instruments, etc., can solve the problem of large influence of output current, and achieve the effect of suppressing the influence of output current, offsetting errors, and improving the power supply rejection ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

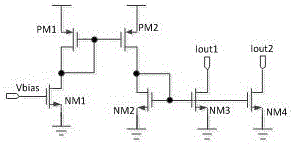

[0036] Such as figure 2 , image 3 As shown, the reference current generating circuit includes a PMOS transistor PM1 and an NMOS transistor NM1, the gate of the PMOS transistor PM1 is connected to the drain of the NMOS transistor NM1, the source of the PMOS transistor PM1 is connected to the power supply, and the drain of the PMOS transistor PM1 is connected to the drain of the NMOS transistor NM1. drain; the gate of the NMOS transistor NM1 is connected to the bias voltage Vbias of the external port, and the source of the NMOS transistor NM1 is grounded; the first mirror circuit includes a PMOS transistor PM2 and an NMOS transistor NM2, and the gate of the PMOS transistor PM2 is connected to that of the NMOS transistor NM1 Drain, the source of the PMOS transistor PM2 is connected to the power supply, the drain of the PMOS transistor PM2 is connected to the drain of the NMOS transistor NM2, the gate of the NMOS transistor NM2 is connected to the drain of the NMOS transistor NM...

Embodiment 2

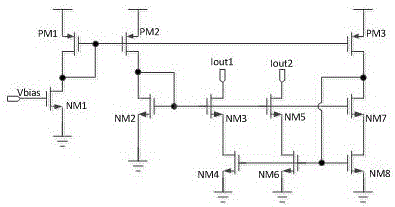

[0043] Such as Figure 4 As shown, the reference current generation circuit includes a PMOS transistor PM1 and an NMOS transistor NM1, the gate of the PMOS transistor PM1 is connected to the bias voltage Vbias of the external port, the source of the PMOS transistor PM1 is connected to the power supply, and the drain of the PMOS transistor PM1 is connected to the NMOS transistor NM1 The drain of the NMOS transistor NM1 is connected to the drain of the NMOS transistor NM1, and the source of the NMOS transistor NM1 is grounded; the first mirror circuit includes a PMOS transistor PM2 and an NMOS transistor NM2, and the gate of the PMOS transistor PM2 is connected to that of the NMOS transistor NM2. Drain, the source of the PMOS transistor PM2 is connected to the power supply, the drain of the PMOS transistor PM2 is connected to the drain of the NMOS transistor NM2, the gate of the NMOS transistor NM2 is connected to the drain of the NMOS transistor NM1, and the source of the NMOS t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More