Vector vliw architecture graph coloring register grouping method

An allocation method and register technology, applied in the field of code compilation optimization, can solve problems such as limiting degrees of freedom, constructing conflict graphs, poor applicability, etc., and achieve the effect of reducing time pressure, reducing space pressure, and obvious effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0084] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

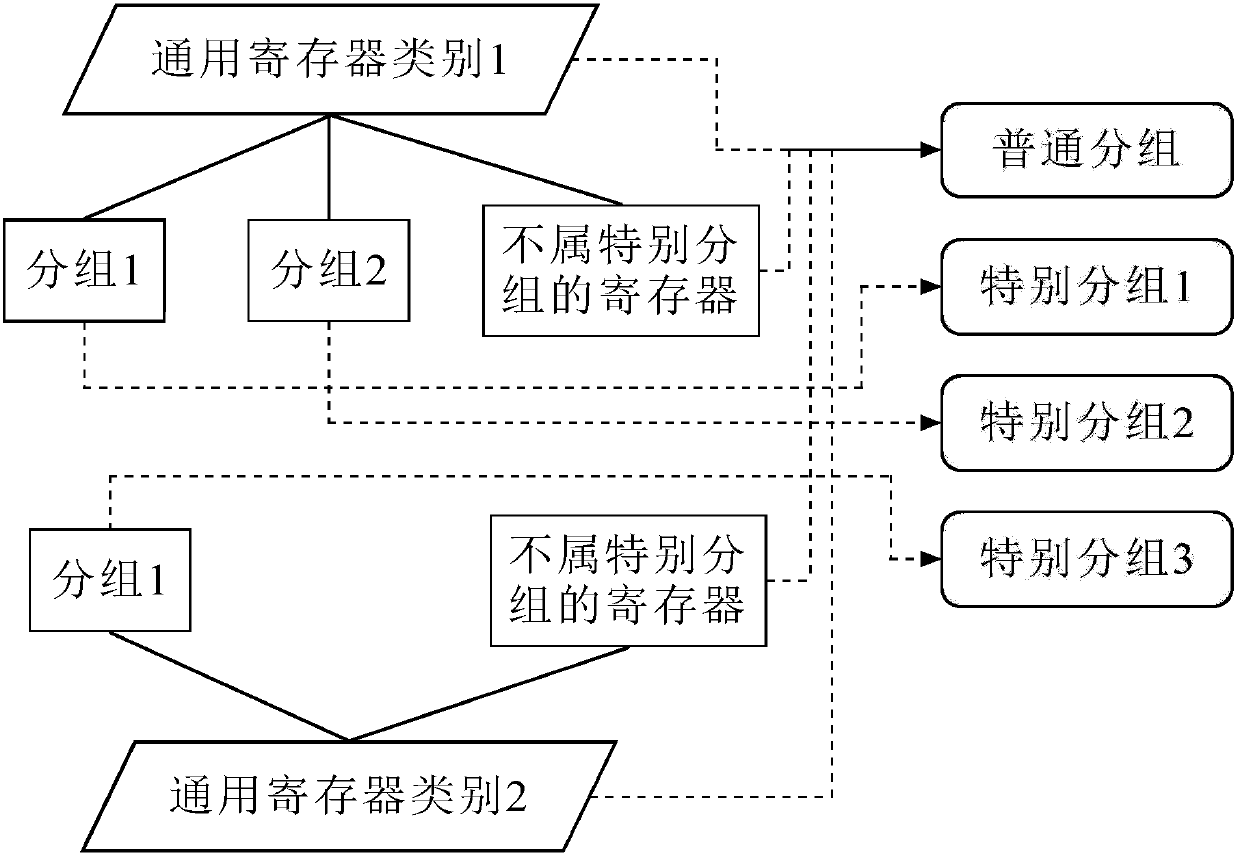

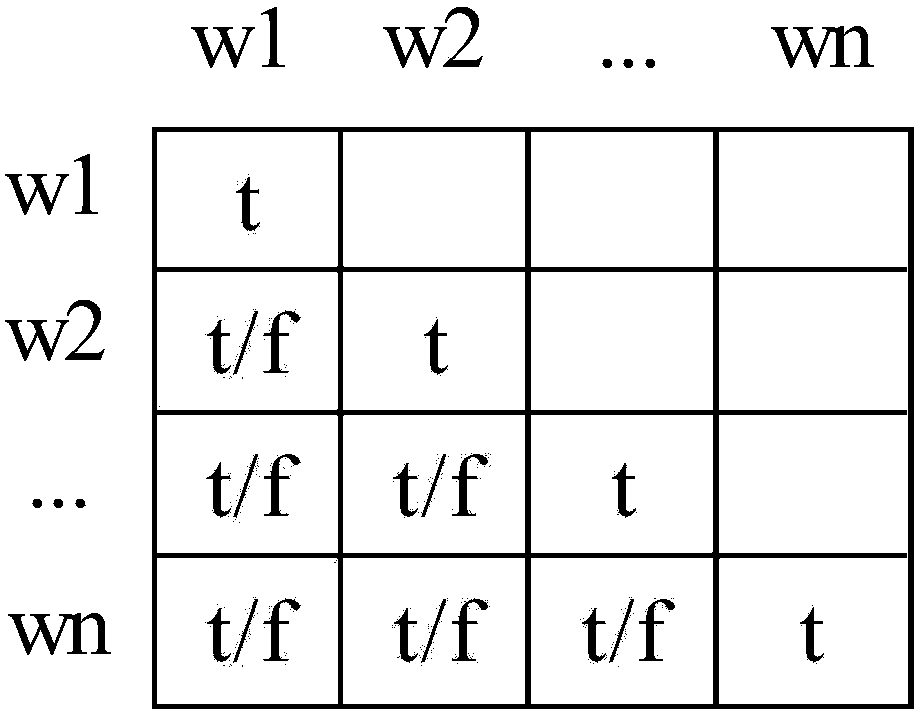

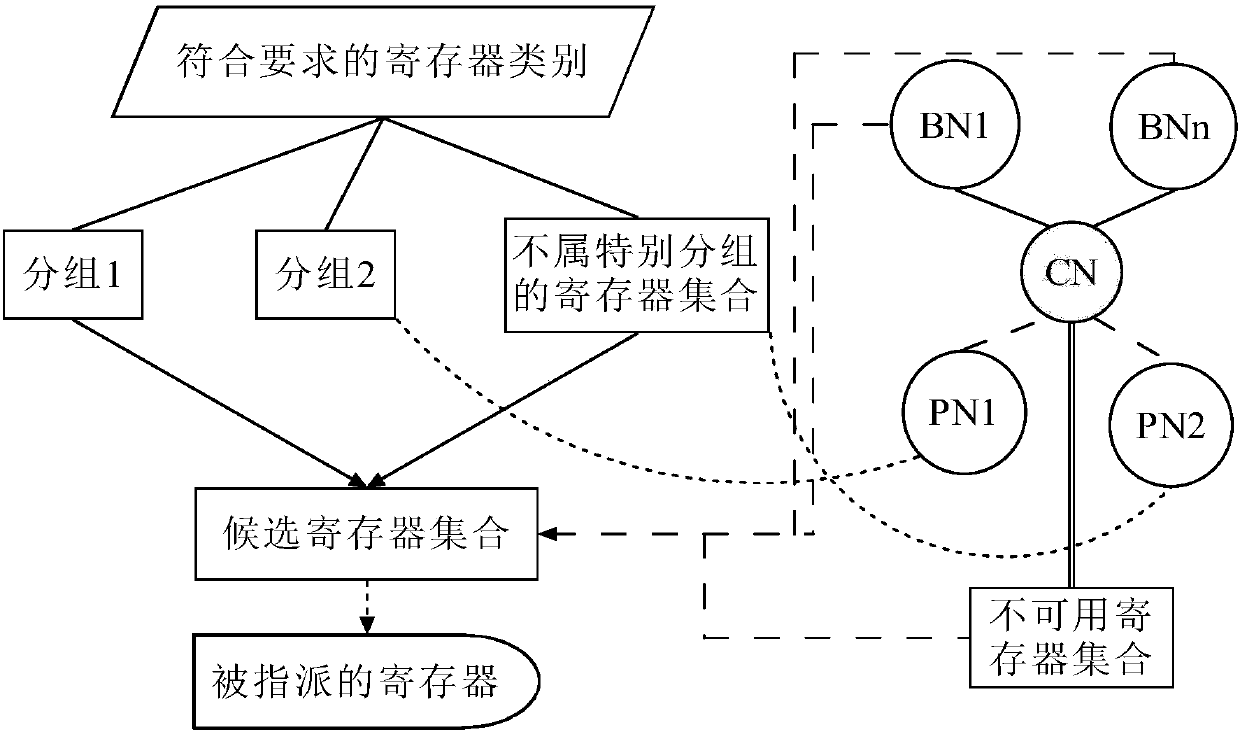

[0085] The vector VLIW architecture diagram coloring register group allocation method of the present invention is to abstract multiple groups in various registers in advance according to the requirements of the hardware; when register allocation is performed, the appropriate group is allocated according to the requirements of the instruction template where the candidate is located registers in . The method of the present invention takes the graph coloring method as the basic idea, improves and optimizes the following links on the basis of the typical graph coloring global register allocation method: analysis of register allocation candidates' attributes related to register requirements, conflict relationship analysis, register allocation Merge, Conflict Graph Pruning, Physical Register Assignment.

[0086] The method of the present i...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap